基于XCR3256的低功耗存储测试器研究设计

发布时间:2011-1-26 17:57

发布者:conniede

|

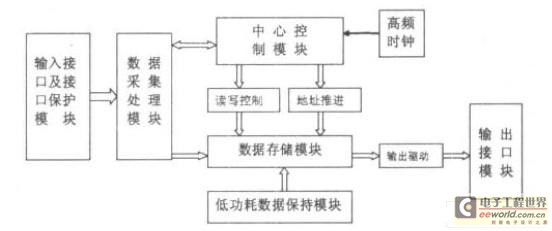

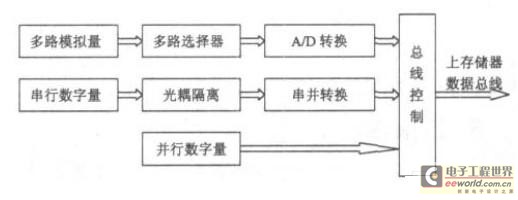

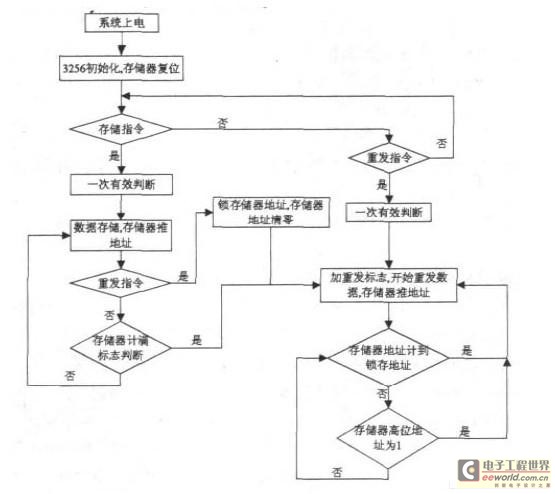

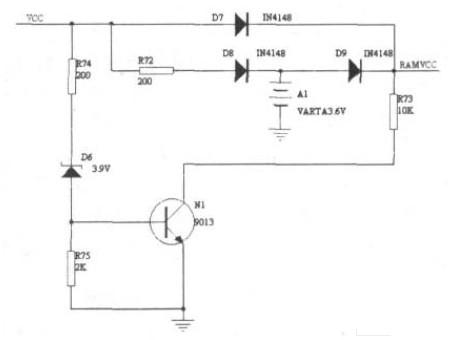

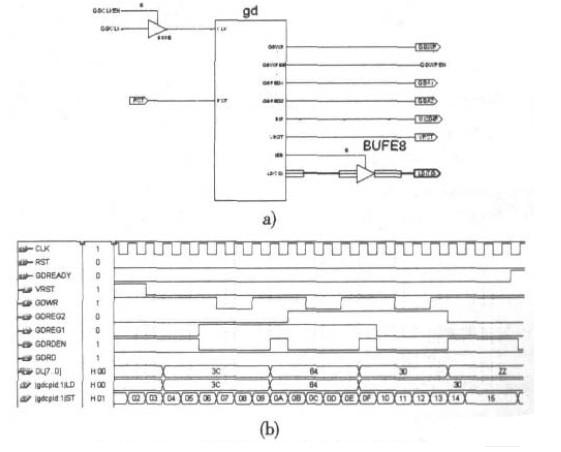

1 引言 在各类飞行器系统的科研过程中,对动态数据的测试通常有两种方式:一是无线电遥测法,二是利用专用传输线检测飞行器工作状态。然而,当飞行系统再入大气等离子中断区或者在水下时,则无法及时动态获得系统状态信息。该存储测试器,即黑匣子,即可在例如以上的恶劣环境中实时采集飞行器各种状态信息,并把采集到的数据按照一定的数据格式存储起来,事后再现飞行器在盲区的工作状态。该存储测试器为诸如上述测试过程中的故障模型建立及分析提供了重要依据。 随着科学技术的不断发展,元器件集成更多功能,对测试的要求,除了智能化、存储容量大、安全可靠等之外,对测试设备小型化及低功耗的要求也持续增长。低功耗目标的实现须从电子器件的开发到终端产品的设计各个环节中得到落实。 2 系统设计及工作原理 存储测试器是一个有机的整体,它同时与被测系统又有信息交换。因此,其各个相关的系统必须互相匹配、兼容,协调工作。在模块化设计中实现了时序匹配、阻抗匹配、精度匹配、动态范围匹配等。 2.1 系统设计 该数据存储测试器基于XCR3256主控,可实现采编存储重发功能,能够在指令控制下通过接口模块采集多形式种信号,经过数据处理将采集到的数据在帧、码同步信号指令作用下按照32×32的帧格式存储起来。系统框图见图1。 基于飞行器信号形式的多样性,输入接口设计中包括模拟量输入、422差分串行数字量输入以及并行数字量输入。针对以上输入数据进行的数据处理包括串行数据的光隔处理及串并转换,对模拟量的采样及A/D转换,最终生成并行数据,并在中心控制模块的控制下分别写入存储器。数据处理单元见图2。 当系统断电时,由于数据具有低功耗数据保持模块,可将先前存储来的数据保持下来,数据保持能力可达一年之久,再次上电可通过并行口、差分串行口或者高速USB口将数据读出。  图1 数据存储测试器结构图  图2 数据处理单元 2.2 工作原理 系统的工作状态主要有数据采集状态、数据存储状态、数据重发状态以及低功耗数据保持状态。数据存储状态与数据的采集状态并行,而重发状态可在数据存储期间中断存储状态进行,也可以通过判断帧计数来完成计满重发,重发数据前加特殊字字头以标示重发周期的开始。也可在上电之后直接重发,所有重发都可以实现循环重发。  图3 数据存储重发工作流程图 数据存储编帧实现方法:通过对存储命令,启动数据存储状态。帧同步信号共有2个,对应每一主帧最后两路的帧标识EB,90。在主帧中包括三路计数,分别为低计数,中计数和高计数。低计数决定副帧的长度,当低计数从00计到1F(十六进制,下同)时,低计数清零中计数进位,同时主帧的帧标识由 EB,90改写为14,6F(此时对应有副帧同步信号),从而实现了32×32的全帧数据格式。中计数计到FF时清零高计数进位。可通过对帧计数是否连续的判断来鉴别数据的记录是否有丢数,错数。 对于每路副帧的数据格式安排如下:低计数为00,01时插入帧字头,计到1E,1F时记录当前中计数和高计数,中间的28帧记录系统中的各工作状态参数。全帧中同一位置为同一个参数的不同时刻的状态。 3 低功耗的实现方法 降低系统功耗的传统手段主要集中在硬件上, 如:选择低功耗器件、安排不同的供电回路等。然而,硬件只是一个平台,软件的作用不容忽视,总线上几乎每一个芯片的访问、每一个信号的翻转差不多都由软件控制,如果软件能减少外存的访问次数、及时响应中断等都将对降低功耗作出很大的贡献。 3.1 硬件 3.1.1 芯片级低功耗实现技术 在该设计中大部分器件如主控芯片、存储器、总线驱动器、FIFO等都是采用的CMOS、HMOS低功耗器件。 主控芯片选用的Xilinx公司的CPLD,型号为XCR3256,3.3V工作电压,低功耗运作,5V与3.3V兼容I/O端口。对于不用的 I/O口全部设为输出(外面不接任何有驱动的信号)。如果I/O悬空的话,受外界的一点点干扰就可能成为反复振荡的输入信号了,而CMOS器件的功耗基本取决于门电路的翻转次数。此外,悬空的输入引脚由于处于0, 1 之间的过渡区, 可使电路中的反相器P 沟道和N 沟道都处于导通状态, 也将导致CPLD本身功耗增大。如果把它们上拉,每个引脚也会有微安级的电流。因此,在设计中将不同的I/O全部设为输出。 3.1.2 电路级低功耗实现技术 公式(1)为CMOS电路功耗的计算公式。式中:P为静态和动态功耗总合;m为节点数;n为器件总数;VDD为工作电压;fak为时钟频率;ILn为反向漏电流;ISCn为瞬态短路电流;am为节点充电率;cm为节点电容。  从该公式中可见降低系统工作电压可达到降低系统功耗的目的。对于中心控制模块采用专用的低电压电源模块TPS70358进行供电。TPS70358可以提供3.3V/2.5V两组供电方式,同时它本身还具有电源管理功能。 图4为低功耗数据保持电路,在存在系统供电时,可对电池进行充电,当系统掉电时可由电池对存储器进行供电,实现数据的自保持。存储器的静态功耗仅为10mW ,由计算可知该电路实现的数据保持期可达一年以上。  图4 低功耗数据保持电路 3.2 软件 正如我们所知,对于可编程逻辑器件,其内部触发器的翻转次数以及开关量的输出对器件本身的功耗影响非常大。该设计通过软件实现了主控芯片自身的功耗调节,通过控制系统内芯片使能以及总线的工作状态实现了系统级的低功耗。 3.2.1 采用状态机编码 在主程序中采用状态机编码,对输入输出信号进行赋值保护。对最终输出信号不需要更新的输入信号利用状态机控制阻止其传播至下一个状态或其他逻辑块。仅在需要时改变输出值,减少了不必要的开关输出。  图5 82C52的状态机配置模块及仿真结果 从数据采集处理模块出来进入数据存储模块的数据其实为三路数据,通过状态机利用锁存器使三路数据在不同时刻占用存储器的数据总线,有效抑制了无效的开关活动。 3.2.2 充分利用了元器件的使能控制 在整个系统的工作过程中,有时候一些器件的行为对当前的功能实现不是必须的,但增加了多余功耗。如存储器的功耗在片选有效时,无论读写信号状态如何,都将比片选无效时大几十倍以上。在该系统中通过把一个控制系统映射到中心控制模块,在满足必要约束的条件下,尽可能的缩短了各芯片和控制逻辑的片选及使能。通过解除与当前操作无关的器件的使用,有效地减少了系统的总开关活动,降低了系统的功耗。 3.2.3 采用门控时钟技术 在整个程序中分为消抖模块、82C52的配置模块、地址发生器模块、并串转换模块以及数据编帧模块等几大部分,其中又包括若干个进程。对于暂时不用的模块停止其时钟。因为有源时钟缓冲器数目的减少直接导致了翻转触发器次数的减少,而触发器输出端可能的反转也随之减少。运用门控时钟技术要求仔细规划和分割算法,当可节省可观的系统功耗。图5(a)中82C52配置模块中的BUFE即可实现门控作用。 此外,系统时钟频率越高,时钟信号开关活动越频繁,电容性负载就越大,系统功耗也就越大。因此,系统时钟对系统功耗也有显著的影响。结合实际情况,在该设计中选用9. 8306MHz的晶振。 4 结束语 该数据存储测试器技术指标如下: ◆数据存储容量2MByte; ◆数据存储波道30路; ◆80路模拟量采样; ◆422差分串行数字量采样; ◆并行数字量采集; ◆系统功耗:50mA; 相关技术已应用于某某项目的测试,在运动过程中对系统的数字量和模拟量进行存储和重发,取得了良好的效果。 该技术的应用已扩展到各个领域,不仅可为飞行器的重要参数的获取提供了经济、高效的手段,也可为飞机、汽车、坦克、船舶、潜艇等地面、水上、水下运载工具的故障分析提供了充分的依据,对不断完善各类运载工具,降低其研制、维修成本具有一定的意义。 |

网友评论