基于OR1200的嵌入式SoPC硬件平台设计

发布时间:2010-11-16 10:53

发布者:eetech

|

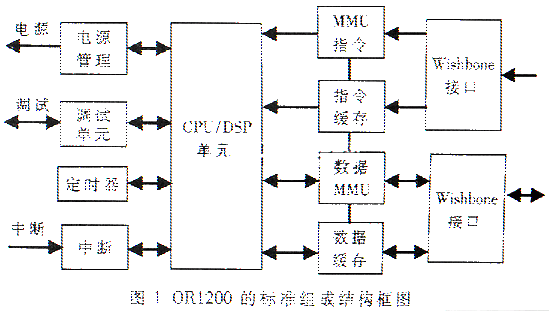

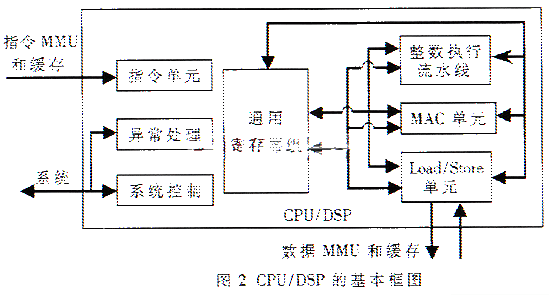

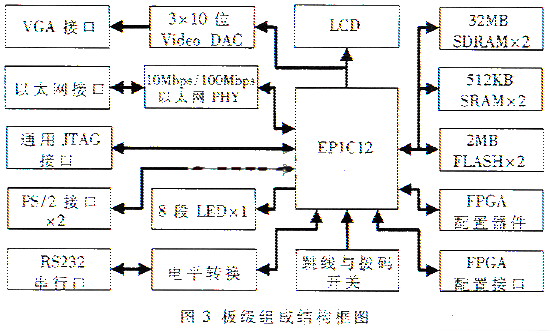

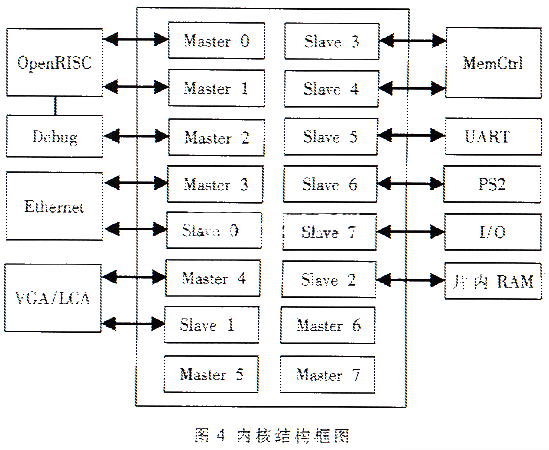

针对现有商业SoPC系统的固有问题,提出了基于开源IP核与软件资源的SoPC系统硬件平台构建方案,并使用Cyclone FPGA进行了实际验证,证明了该硬件平台的实用性。探讨了该平台在普及SoPC技术和研究更高性能系统方面的积极作用。 SoC(System on Chip)片上系统是现代电子系统设计的一个发展方向,它将原先分立的多个芯片集成在一块芯片上,通过提高芯片的集成度、减少系统芯片的数量和相互之间的PCB连线、减少PCB面积来降低整个系统的成本,同时使系统的性能、功能和可靠性都有很大的提高。随着新型的高性能、低成本FPGA的出现和综合技术的提高,基于FPGA的SoPC(System on Programmable Chip)可编程片上系统正逐步走向市场。基于FPGA的SoPC与基于ASIC技术的SoC相比,具有设计周期短、产品上市速度快、设计风险和设计成本低、集成度高、灵活性大、维护和升级方便、硬件缺陷修复和排除简单等优点。因此基于FPGA和包括32位CPU在内的各种IP核的系统级应用开发将是下一代电子系统设计的发展方向。 顺应这个潮流,FPGA器件的方要供应商Altera和Xilinx都推出了各自的SoPC解决方案:Nios系统和MicroBlaze系统。它们功能强大、开发环境和配套IP核完善,是工程应用的首选。但是它们只能用在各自厂商的FPGA上,不但配套IP核价格昂贵,而且用户无法获得所有源代码,不利于我国SoPC技术的发展。  针对这种情况,笔者使用Altera公司的Cyclone FPGA和OpenCores组织提供的各种免费、开源的IP核,构建了以OpenRISC1200CPU为核心,配以各类外围IP核的完全开源的SoPC系统,并成功地运行了μClinux系统。同时本系统采用的所有IP核在源代码不变的情况下可以使用Xilinx的开发工具进行综合、布线,为该系统在其他FPGA平台上的运行打下了良好的基础。 1 OR1200 本系统使用的OpenRISC1200处理器(以下简称OR1200)是OpenRISC系列RISC处理器内核的一员。OpenRISC是由OpenCores组织负责开发和维护、免费、开源的RISC处理器内核家族。OpenRISC1200出现于2001年7月,支持ORBIS32指令集。该指令集包括32位整数指令、基本的DSP指令、32位的Load和Store指令、程序流程控制指令和特殊指令(实际上还不支持除法指令)。2002年8月,OpenRISC1200基本成熟,配有比较完善的软件开发环境和操作系统,改进和维护一直持续到现在。 OR1200是一种32位、标量、哈佛结构、5级整数流水线的RISC处理器,它有32个32位通用寄存器,支持缓存、虚拟存储器和基本的DSP功能,外部数据和地址总线接口符合Wishbone标准。辅助功能包括用于实时调试的调试单元、计数器、可编程中断控制器和电源管理单元,这些功能大大增强了CPU独立工作的能力,对软件调试和操作系统的支持较好,简化了整体系统的设计。OR1200的标准组成结构如图1所示。 CPU/DSP单元是OR1200处理器的核心,其基本结构框图如图2所示。 当使用0.18μm和6层金属工艺时,OR1200的主频可达300MHz,此时可以提供300Dhrystone2.1MIPS和300M次/秒的32%26;#215;32的DSP乘加操作能力。 OR1200在2002年9月被Flextronics公司选中,用于集成在Flextronics的设计中,并提供商业服务。2003年8月,Flextronics公司成功实现了集成OR12000、10Mbps/100Mbps自适应以太网MAC控制器、32位33MHz/66MHzPCI接口、16550兼容UART和Memory控制器的SoC芯片,并成功运行了μClinux和Linux操作系统。  2 板级系统组成 板级系统以Altera的Cyclone系列FPGA EP1C12QC240为核心,配以EPCS4配置存储器和配置电路组成核心系统,再配以2片29LV160DB NOR Flash(4MB)、2片IS61LV25616 SRAM(1MB)、2片HY561620 SDRAM(64MB)、1个RS232串行口、1个通用JTAG接口和8段LED、按钮、拨码开关组成基本系统。Flash、SRAM和SDRAM组成存储系统,它们共用FPGA的存储器总线,大大减少了存储系统占用的FPGA管脚数,并为系统提供了运行大型软件所需要的存储器空间。通用JTAG接口可以通过专用接口电缆与PC机的并口相连,实现对CPU的在线调试和系统存储空间的访问。串行口可以为系统实现一个基本的控制台,并可以作为向系统下载大量数据的通道。因此,基本系统的组成足以调试和运行基本的μClinux系统。 完整的板级系统的组成框图如图3所示,它除了基本系统以外,还包括1片10Mbps/100 Mbps自适应以太网PHY芯片、320%26;#215;240彩色STN LCD、10位%26;#215;3通道视频DAC和2个PS2接口。使用以上完整的板级系统可以实现简单的网络和人机界面应用,再配以μClinux操作系统即可实现一个完整的计算机系统。 3 内核的集成、仿真与验证 内核的集成、仿真与验证是建立本平台的难点。要实现上述所有功能,除了OpenRISC1200 CPU外,至少还需要以下IP: Wishbone总线互连; CPU Debug模块; 通用I/O控制器; 片内高速RAM控制器; 16550兼容UART控制器; Memory控制器; 0Mbps/100 Mbps自适应以太网MAC控制器; VGA/LCD控制器; 8042兼容PS/2控制器。 以上多数IP可以从OpenCores获得,像通用I/O控制器和片内高速RAM控制器这类简单的IP,可以自己编写。不过需要注意的是,为了使系统能够正确地运行或者获得更好的综合效果,多数IP在集成时都要进行修改。需要修改的IP及其修改内容如下: OR1200:通用寄存器组、缓存、MMU使用的RAM块需要针对Synplify进行修改,以便能够综合至M4KRAM块中,MMU、DSP MAC单元根据需要决定是否在配置中去掉,以提高速度,减少逻辑资源的占用; Wishbone总线线连:添加空穴地址空间的访问处理; UART控制器:数据接收和发送FIFO需要针对Synplify进行修改,以便能够综合到M4K RAM块中; Memory控制器:添加复位后的默认值配置,以便系统可以选择从Flash或者SRAM启动; 以内网控制器:控制寄存器和FIFO需要针对Synplify进行修改,以便能够综合进M4K RAM块中,并且需要添加对不支持Burst模式的Wishbone总线互连接口的支持; VGA/LCD控制器:显示FIFO需要针对Synplify进行修改,以便能够综合进M4K RAM块中,并且需要修改对扫描时钟输出的控制。  使用以上IP构建的系统内核的结构框图如图4所示。中间模块是Wishbone总线互连IP,它有8个主设备、8个从设备接口。OR1200的指令和数据接口各占用了一个主设备接口。Debug模块需要访问存储空间,因此也用了一个主设备接口。以太网控制器使用主存储器来存储、获得数据,VGA/LCD控制器使用主存储器获得显示缓冲数据,因此它们也都占用了一个主设备接口。以太网、VGA/LCD和Memory控制器的控制寄存器空间各占用了一个从设备接口,Memory控制器的存储器空间占用了一个从设备接口,其余的UART、PS/2、I/O和片内RAM控制器各占用了一个从设备接口。  为保持软件的兼容性,在设置Wishbone总线互连IP各个主设备和从设备的地址以及分配中断号时,需要符合ORP标准。ORP(OpenRESC Reference Platform)是一个对基于OpenRISC处理器的系统的定义,它包括存储器空间、外围设备的地址定义和中断向量的分配。其作用是标准化基于OpenRISC的硬件和软件的设计,提高软件可重用性并缩短硬件设计的验证时间。 在进行完各个IP的单独测试后,使用OR1200的软件开发包GCC对系统引导程序和μClinux进行编译,并将得到的二进制文件嵌入到存储器仿真文件中,对系统的初始化、引导和操作系统的启动进行仿真。 在仿真成功后,进行了下载验证。由于使用的EP1C12器件的逻辑容量有限,无法同时实现以上所有功能,因此设计了两个配置方案,分别而向网络和个人终端。前者具备以太网功能,但是没有PS/2和VGA/LCD控制器,后者相反。使用Synplify和QuartusII软件对个人终端配置的系统进行综合、布局布线后,系统速度和各模块所占逻辑单元Les(Logic Elements)的情况如表1所示。 表1 系统速度和各模块所占LEs 模 块 LEs -8等级器件速度 -6等级器件速度 OR1200 4170 44.0MHz 62.7MHz Debug 510 UART 250 UART 1060 Memory 820 以太网 2450 VGA/LCD 1550 PS/2 256 通用I/O 20 实际下载验证证明,以上两种配置都可以40MHz的速度运行μClinux系统。目前,已经选定使用该系统作为基于SoPC的数控系统的基础实现平台。 |

网友评论