基于FPGA的RGB到YCrCb颜色空间转换

发布时间:2010-11-9 20:59

发布者:techshare

|

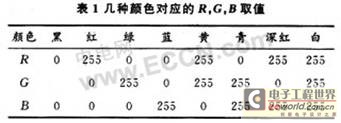

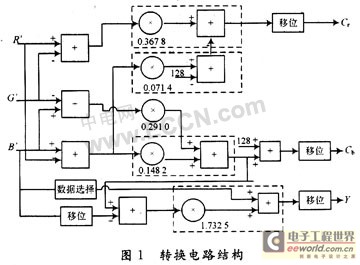

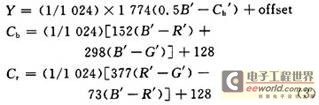

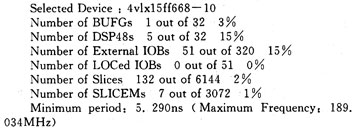

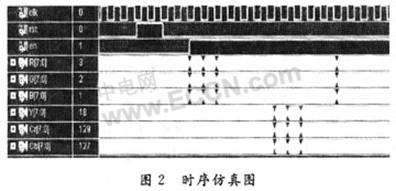

随着多媒体和通信技术的发展,视频图像处理的实时性成为人们关注的热点。视频图像处理一般都是用数字信号处理器(digital signal processor,DSP)来完成的。为了满足实时性要求,往往采用多DSP或DSP阵列的方法,使系统在成本、重量、功耗等方面都会快速升高。现场可编程门阵列(FPGA)运算的并行性和内嵌DSP核等特点,能够提高运算速度满足视频处理的实时性要求。在视频图像显示、处理时,采用的颜色空间主要有RGB,YCrCb两种。RGB基于三基色原理,颜色实现简单,在计算机、电视机显示系统中应用广泛,YCrCb将颜色的亮度信号与色度信号分离,易于实现压缩,方便传输和处理。在视频压缩、传输等应用中经常需要实现RGB与YCbCr颜色空间的相互变换。这里推导出一种适合在FPGA上实现从RGB到YCbCr。颜色空间变换的新算法,采用单片FPGA完成电路设计,利用FPGA内嵌DSP核实现乘法运算,提高了转换算法的运行速度。 1 颜色空间 在RGB颜色空间中,自然界所有颜色都可以用红(R)、绿(G)、蓝(B)三种颜色的不同强度组合而重现。RGB的取值范围分别为0~255,表1列出了几种颜色对应的R,G,B取值。  RGB生成颜色容易实现,被广泛应用在计算机、彩色电视机的显示系统中。但是RGB表示颜色的效率并不是很高,3个颜色分量同等重要,而且亮度信息存在于所有颜色分量中,当需要对像素点的亮度或者色度值进行修改时,必须同时改变RGB三者的值。 YCrCb颜色空间是在开发世界范围数字分量食品标准过程中作为ITU-R BT.601标准的一部分而开发出来的。在YCRCb颜色空间中,Y表示亮度信号,取值范围为16~235;Cr,Cb表示色度信号,取值范围为16~240,亮度信号与色度信号相互独立。这种颜色表示方法可以利用人眼的特性降低数字彩色图像的存储空间。人眼视觉系统(HVS)对亮度细节的敏感度高于颜色细节,适当减少色度分辨率不会明显影响图像的画质,易于实现数据压缩。 2 RGB到YCrCb的转换 在ITU-R BT.601标准中给出了RGB与YCrCb的转换关系式如下: 式中:R’,G’,B’表示Garoma校正后的R,G,B值。该转换关系式是一个3×3乘法矩阵,电路实现时需要9个乘法器和9个加法器,在FPGA中直接实现时将会占用较多逻辑资源。 为了减少逻辑资源的使用,需要对该算法做进一步改进,简化运算过程,从而以较少的逻辑资源实现转换电路。首先对Cb,Cr做如下化简: Cb=0.148 2(B’-R’)+0.291 0(B’-G’)+128 Cr=0.367 8(R’-G’)-0.071 4(B’-R’)+128 对y的计算公式进行化简时,令Y’=0.256 8R’+0.501 4G’+0.097 9B’,Cb’ =-0.148 2R’-0.291 0G’+0.439 2B’,有0.577 2Y’+Cb’=0.495 7B’。为了计算方便,近似值为0.5B’。此时,有Y’=1.732 5(0.5B’-Cb’),与原式误差为△Y’=0.007 4B’,其范围为0~1.887。当以Y’表示Y时,需要对误差作补偿。计算公式可表示为: Y=1.732 5(0.5B’-Cb’)+offset 式中:offset=16-0.007 4B’,化简后的转换公式如下: Y=1.732 5(0.5B’-Cb’)+offset Cb=0.148 2(B’-R’)+0.291 0(B’-G’)+128 (2) Cr=0.367 8(R’-G’)-0.071 4(B’-R’)+128 式中:Cb’=0.148 2(B’-R’)+0.291 0(B’-G’), offset=16-0.007 4B’。 根据B’的取值不同,offset的取值取整后为14,15,16。在计算过程中,可以用一个数据选择器根据B’值的不同选择offset的值。0.5B’的计算可以用移位实现。化简后的转换算法,对Y,Cb,Cr的计算将比原来节省4个乘法器。在FPGA中,加法器、数据选择器和移位算法的实现比乘法器简单,该化简将利于减少逻辑资源的应用,简化实现电路,提高运算速度。 转换电路结构如图1所示。  3 基于FPGA的实现 在FPGA中,对乘法的实现比较复杂,可以采用如下几种方法: (1)直接用编程语言描述乘法运算,由综合工具自动实现,用该方法描述,实现简单,但是耗用比较多的逻辑资源。 (2)利用查找表的方式实现乘法运算,事先把要相乘数据的所有结果算出来存到ROM中,根据输入数据的值读取相应的结果,当用该方法相乘数据位数比较多时,会占用大量的存储空间。 (3)用FPGA中内嵌的乘法器实现,该方法实现简单,当用VHDL语言实现时,调用相应的乘法模块即可。 本文采用第三种方法,用专用乘法器来实现转换公式中的乘法运算。Xilinx的Virtex 4系列FPGA芯片内嵌的乘法器为Xtreme DSPTM Slice-DSP48 Slice其工作频率高达500 MHz,支持多种独立的功能,包括乘法器、乘累加器(MAC)、后接加法器的乘法器、三输入加法器、桶形移位寄存器、宽路线多路复用器、大小及比较器或宽计数器。本文将运用DSP48 Slice模块实现乘加运算,在电路结构图的虚线框中,乘法和加法的运算将用单个DSP48 Slice模块实现。这样将会减少转换关系式中加法器的数量,节约逻辑资源,在程序中可以用元件例化语句调用DSP48 Slice模块,实现方法简单,程序简洁。为了满足浮点数和运算精度的要求,适合在FPGA中实现,将式(2)改写为:  式中的除法运算可以通过截断低位数据的方法实现,在截断数据时,对截去小数部分判断,采用4舍5人的方法,当截去部分的最高位是1时,有进位,最高位是0时,直接舍去。用VHDL语言描述式(3)的转换算法,输入R’,G’,B’是8位无符号二进制数,进行加减运算时,需要做符号位补位。  在每个运算部件(包括乘法和加减法器)的输出以及系统的输入/输出之间加上缓存寄存器,实现流水线设计,能提高资源利用率,加快运算速度,寄存器级数由运算延时大小决定。在输出端用计数器控制运算开始时的噪音输出。箝位电路控制输出数据范围满足颜色空间的要求。 4 仿真结果 在Xilinx的Virtex4-FX平台实现现图1的电路结构,用ISE软件仿真。资源使用情况如下:  时序仿真结果如图2所示。  通过图2可以验证转换算法的正确性。在使能信号en有效后,经过6个时钟的运算时延,输出端有转换结果输出,输出结果四舍五入,误差0.5,比以往算法提高了变换结果的精度。 5 结 语 通过对转换算法的研究,推导出适合在FPGA上实现的新算法,算法优点突出。算式中乘法器采用DSP48 Slice模块实现,提高了转换算法的运算速度。从综合报告可以看出,除了使用5个DSP48s外,其他资源使用的比较少。运算速度最大能够达到189 MHz,能够充分满足运算量大,实时性要求高的应用。 |

网友评论