NiosⅡ和USB接口的高速数据采集卡设计

发布时间:2010-11-8 15:13

发布者:eetech

|

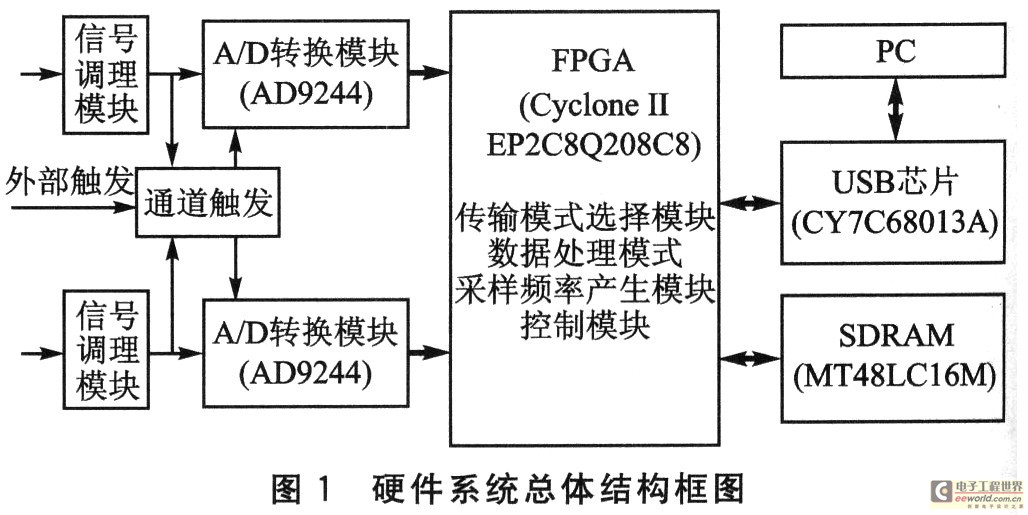

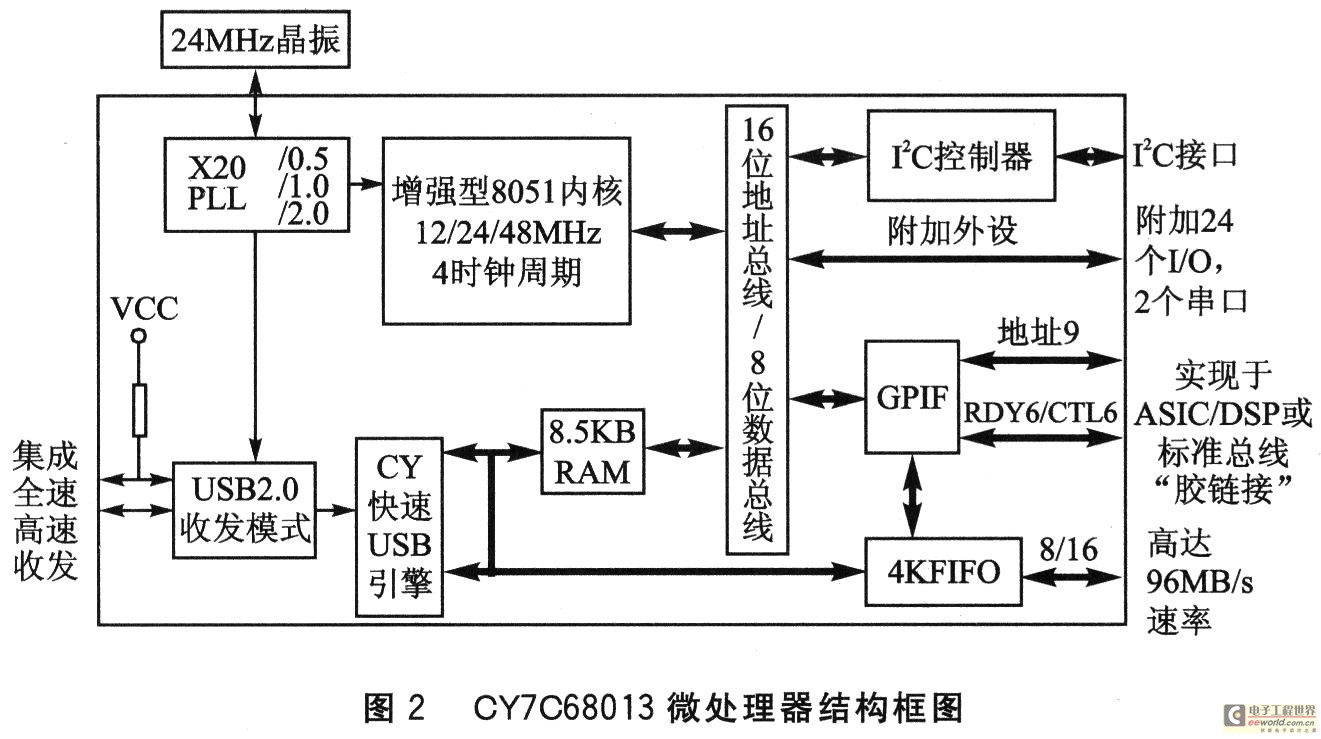

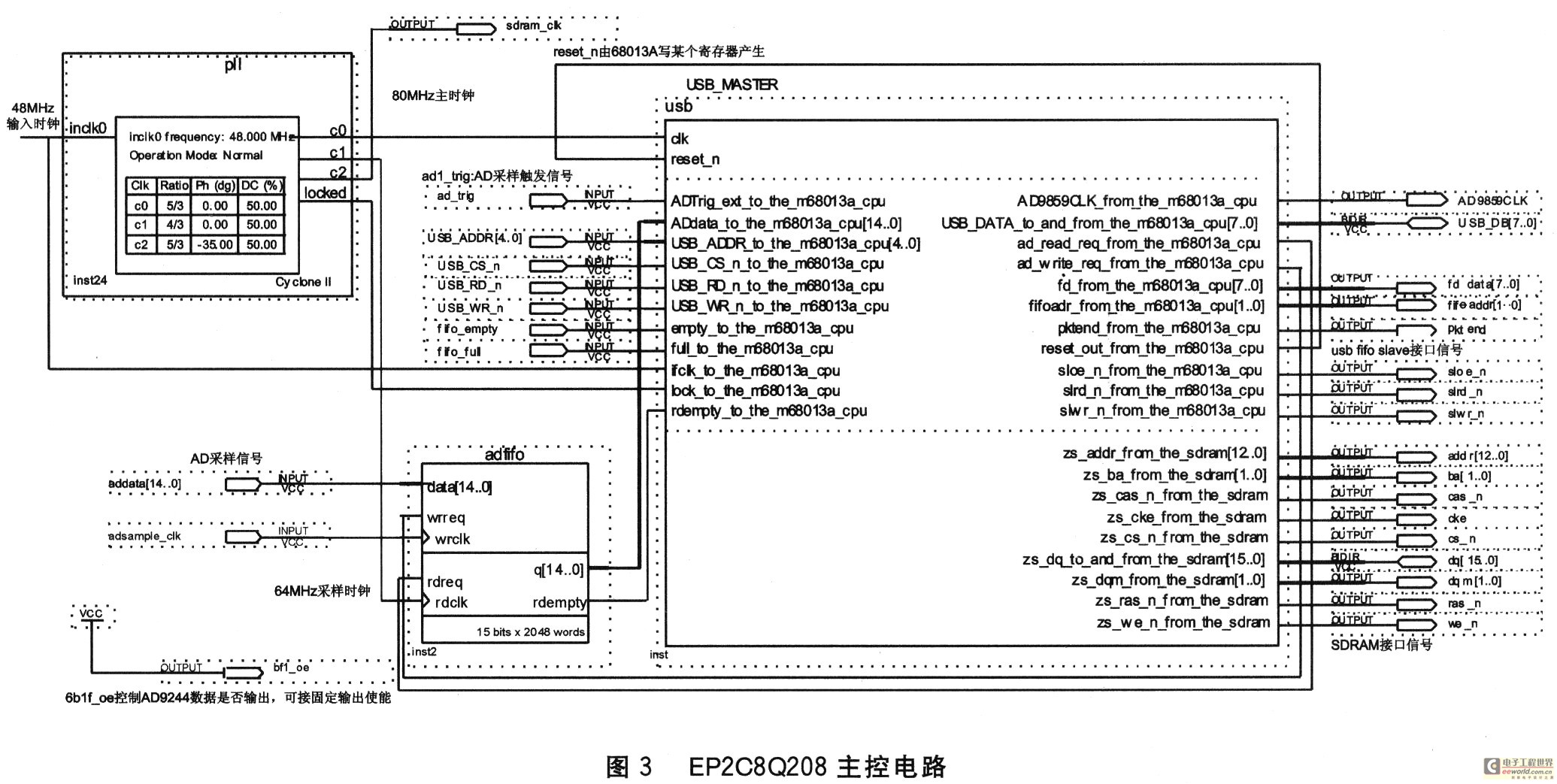

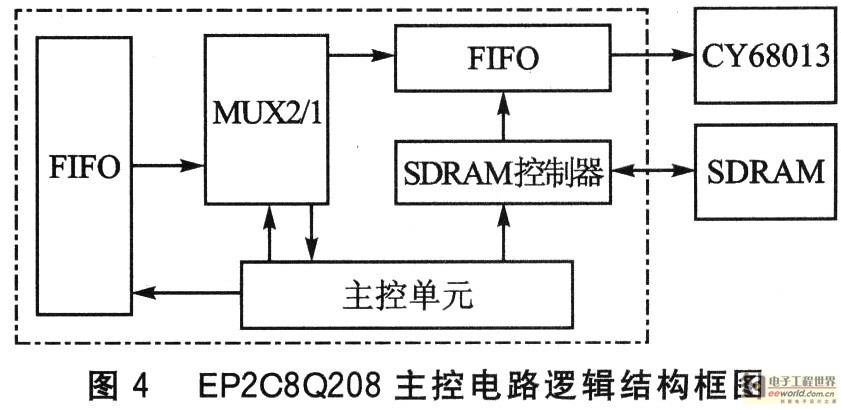

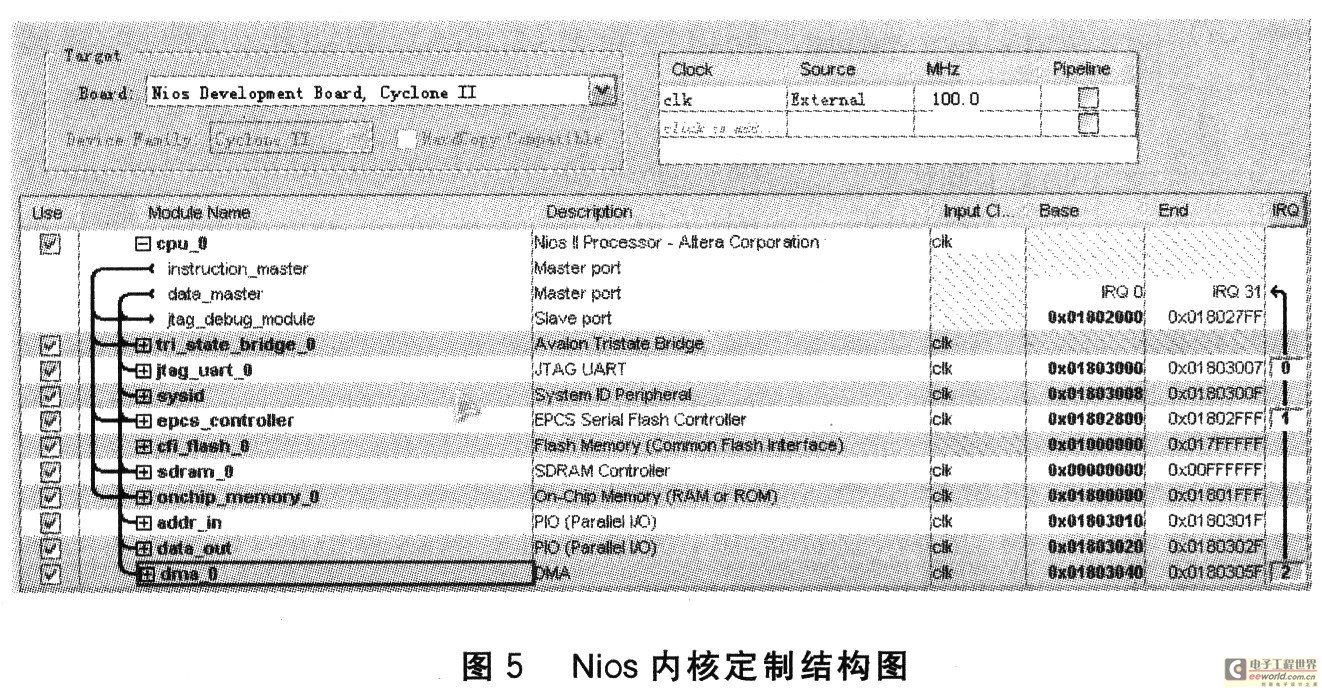

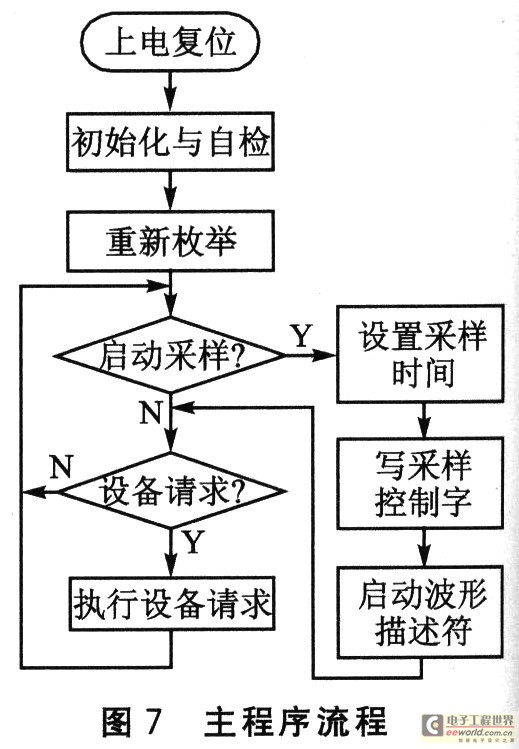

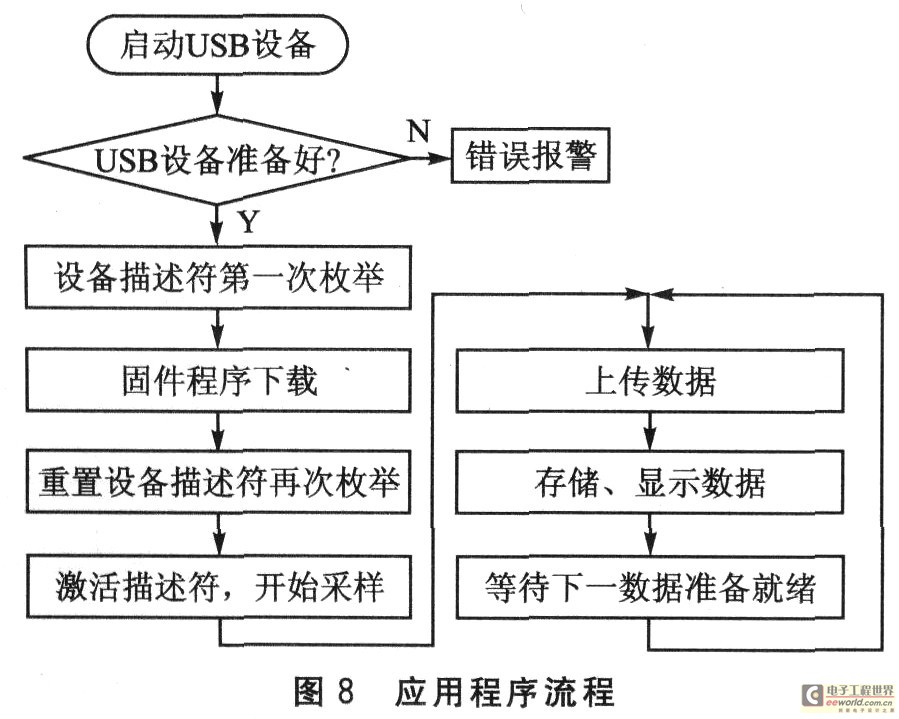

随着现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像信号处理等一些高速、高精度的测量中,都迫切需要进行高速数据采集(如雷达信号分析、超音波信号分析);而进行数字处理的先决条件是将所研究的对象数字化,因此数据采集与处理技术日益得到重视。在图像信号处理、瞬态信号检测、工业过程检测和监控等领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。现在的高速数据采集处理卡一般采用高性能数字信号处理器(DSP)和高速总线技术的框架结构。DSP用于完成计算量巨大的实时处理算法,高速总线技术则完成处理结果或者采样数据的快速传输。DSP主要采用TI和ADI公司的产品,高速总线可以采用ISA、PCI、USB等总线技术。其中PCI卡或ISA卡安装麻烦,价格昂贵,受计算机插槽数量、地址、中断资源的限制,可扩展性差,在一些电磁干扰性强的测试现场,无法专门对其做电磁屏蔽,易导致采集的数据失真。通用串行总线USB是为解决传统总线不足而推广的一种新型的通信标准。该总线接口具有安装方便、高带宽、易于扩展等优点,已逐渐成为现代数据发展趋势。基于USB的高速数据采集卡充分利用USB总线的上述优点,有效地克服了传统高速数据采集卡的缺陷。 1 系统硬件设计 本系统主要是基于USB2.O的S1ave FIFO模式,在FPGA控制下完成双通道、不同速率的数据的采集和发送,全兼容USB2.O总线接口标准,其数据的采样率可高达65 Msps;适用于较高速动态信号的实时记录采集,其硬件系统总体结构框图如图1所示。  该系统主要由信号调理模块、A/D转换模块、触发模块、基于FPGA的主控模块、USB收发控制模块、片外存储器及其他辅助电路组成。调理电路与A/D转换器,将传感器采集的模拟信号进行相关的信号调理后送入AD9244芯片转换为数字信号。处理后的数据送往FPGA主控模块,根据相关的控制信息,选择通过直接传输给上位机,或者先存储在外部SDRAM,然后经过相关的数字处理后再传输给上位机。 2 系统模块介绍 2.1 USB2.0专用微处理器CY7C68013A CY7C68013A是Cypress Semiconductor公司生产的一款集成USB2.O的微处理器。它有3种封装形式——56SSOP、100TQFP和128TQFP,其结构框图如图2所示。  CY7C68013集成了USB2.O收发器、SIE、增强的8051微控制器和可编程的外围接口部件。其SIE可在全速(12 Mb/s)和高速(480 Mb/s)两种模式下运行,同样可以使用内部RAM来进行程序和数据的存储。GPIF和Master/Slave端口FIFO为ATA、UTOHA、EPP、PCM—CIA和DSP等提供了简单和无需附加逻辑的连接接口。其编程可以根据设计的需要进行,不需要CPU的干预,只需通过CPU的一些标志和中断即可进行通信。CY7C68013共有7个输入输出端口:EP0、EPlOUT、EPlIN、EP2、EP4、EP6、EP8,其中EP2、EP4、EP6、EP8可以分别被配置为批量/中断/同步传输模式,传输方向均可配置为I/O,端口EP2、EP6的缓冲区大小可编程为512或1 024字节,深度可编程为2/3/4倍大小;端口EP4、EP8的缓冲区大小固定为512字节,深度为2倍,采用不同的配置方式,可实现特定带宽和速率要求的数据传输。 2.2 主控电路FPGA芯片 EP2C8Q208EP2C8Q208主控电路如图3所示。  FPGA芯片也是一种特殊的ASIC芯片,属于可编程逻辑器件,它是在PAL、GAL等逻辑器件的基础上发展起来的。同以往的PAL、GAL等相比,FPGA规模比较大,适合于时序、组合等逻辑电路应用。本文选用A1tera公司的FPGA芯片EP2C8Q208,完成数据采集卡的时序和地址译码电路设计。由于EP2C8Q208有36个M4K RAM,在FPGA内部设计一个16位宽度、4 KB深度的FIFO,使用FIFO提高数据采集卡对多通道信号的采集存储能力。FIFO有半满、全满、空标志位,当检测到半满标志位时,FIFO同时读写;全满时只读不写;空时只写不读。A/D采样控制信号通过FPGA控制;PC机对采集后的数据作进一步处理,以提高精度,其中2选1模块,由主控制模块来控制,选择是直接将采集数据送给PC机处理,还是在内部进行DSP处理后再送给PC机。 由于Nios是一个位于FPGA中的处理器软核,定制其外设就显得比较容易,在SOPC Builder(集成到Quartus II工具中的为建立SOPC系统设计,提供标准化的图形设计环境。其由CPU、存储器接口、标准外围设备和用户自定义的外围设备组成)环境下,其定制逻辑的结构框图如图4所示。  自定制的Avalon外设按照对总线操作的方式可分为:Avalon Slave外设和Avalon Streaming Slave(流模式)外设。在SOPC Builder图形设计界面下添加需要的内核。通过自动分配系统基地址和系统中断向量,手动分配CPU复位地址为外设Flash、CPU溢出地址为片上RAM和CPU调试断点地址为JTAG调试地址,就可由系统报告得知系统是否定制成功,如图5所示。  2.3 ADC芯片及外围电路设计 ADC外围电路框图如图6所示。  信号调理部分选用高精度、低噪声、低输入偏置电流、宽带运算场效应放大器AD8ll进行信号的放大。模拟信号处理是影响系统性能的重要因素之一,设计时必须考虑两个方面:一是要保证信号质量,提高信噪比,尽量减少畸变;二是将信号变换成适合A/D处理的幅度并提供足够的驱动能力。这里选用ADI公司的宽带运放AD811为放大器。AD8ll是一种电流反馈型的放大器,它具有10 MHz的低失真和单位增益带宽很宽的特点,使AD81l成为理想的高分辨率ADC缓冲器。之后针对信号进行档速变换。档速变换选用ADG系列产品。本设计选用的是一款四路独立选择的单片CMOS开关芯片,其设计基于增强的lc2mos进程、可以提供低功耗、高转换速度和低阻抗性,当信号满足A/D变换的要求后,根据采集要求将其由单端输入变换为差分的双端输出,芯片选用AD8138。AD8138具有较宽的模拟带宽(320 MHz,一3dB,增益为1),可以将单端输入变成差分输出。A/D转换的触发则由信号放大芯片AD811采集信号和D/A转换芯片信号进行比较,当有效时,发出ADn_TRIG信号,其中D/A转换芯片的输入标准信号(数字输入端)由FPGA来提供。当ADn_TRIG有效时,FPGA向AD924.4发出控制命令(DIN、FORMAT、MODE、SCLK、sYNC、FSYNC信号),启动A/D转换。 A/D转换器的精密时钟由DDS电路AD9859YSV提供。 3 软件设计及实现 系统软件设计包括3部分:固件程序、USB设备驱动程序和应用程序。整个软件实现的功能包括系统初始化、采样控制、数据传输和波形显示。 3.1 固件程序设计 固件程序辅助硬件实现设备双向交换数据,以完成USB通信,其主要功能是:接收并处理USB驱动程序的请求及应用程序的控制指令,控制A/D转换器的采样。当首次插入USB时,FX2通过USB电缆会自动枚举且下载固件和USB描述符表;接下来,FX2再次枚举,这次主要通过下载的信息来定义设备。这两个步骤叫作重枚举。固件程序流程如图7所示。初始化包含各个初值的设置和关键点的电平检测。  在Cypress公司的网站上,可下载CY7(368013芯片的开发工具包。该开发包提供了一些开发固件程序所需的资源:Keil u Vision2集成开发环境(限制版)、Cypress C51固件框架程序以及一些例子程序。KeilCSl是一种专为8051单片机设计的高效率C语言编译器,符合ANSI标准,生成的程序代码运行速度极高,所需要的存储空间极小,完全可与汇编语言相媲美。同时,C51具有丰富的库函数,多达1O0多种功能函数。因此,采用C语言作为开发语言,以Keil uVision2作为工程开发平台,完成源代码的编写、仿真、调试,将在相当程度上降低固件开发难度,提高开发效率。 3.2 USB设备驱动设计 USB设备驱动程序的设计是基于WDM(WindowsDriver Model,驱动程序模型)的。WDM采用分层驱动程序模型,分为较高级的USB设备驱动程序和较低级的USB函数层。其中USB函数层由两部分组成:较高级的通用串行总线模块(us—BD)和较低级的主控制器驱动程序模块(HCD)。 本设计用WinDK3.O开发了Win2000下的驱动程序,实现了控制传输、中断传输和批传输的标准接口函数。在应用程序开发中,可用VC++编制应用程序。把USB设备当成文件来操作,用Create—File得到USB句柄,用DevieeloControl来进行控制传输,用ReadFile、WriteFile进行批量传输。 3.3 应用程序设计 应用程序流程如图8所示。用户应用程序是数据采集系统的核心,其主要功能为:开启或关闭USB设备、检测USB设备、设置USB数据传输管道、设置A/D状态和数据采集端口、实时从USB接口采集数据、显示并分析数据。  4 结 论 用FPGA作为采集处理部分,可以提高系统处理的速度,大大增强系统的灵活性和适应性。FPGA技术和USB的组合,使得数据处理能力得到了极大的提高,且有利于系统升级。USB芯片采用了Cpyress公司的高性能USB2.0芯片CY7C68013,可以完全胜任大数据量的传送。该实例还可应用于实时数据采集、音频及压缩视频数据传输等领域。 |

网友评论