利用Virtex-5 器件实现QDR II SRAM 接口

发布时间:2010-11-7 20:08

发布者:techshare

|

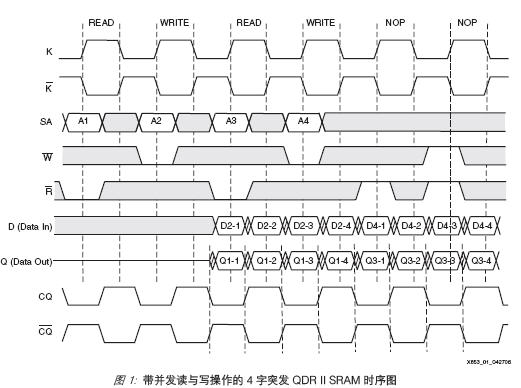

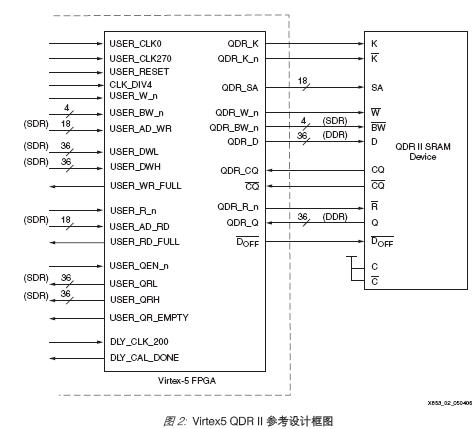

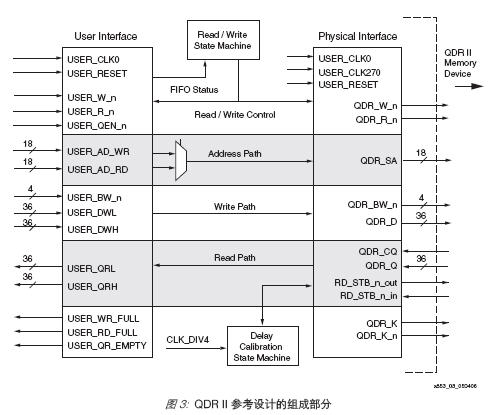

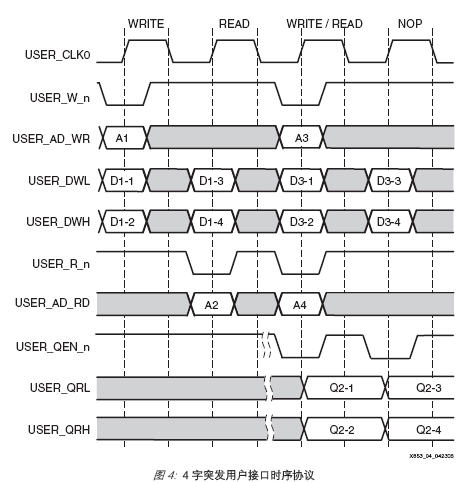

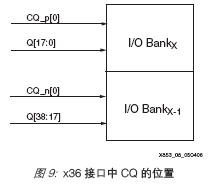

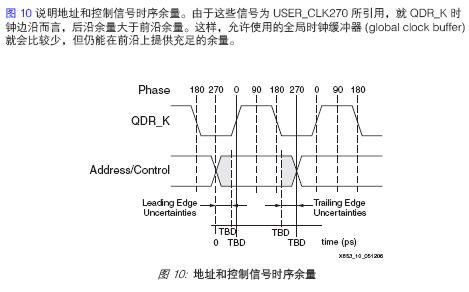

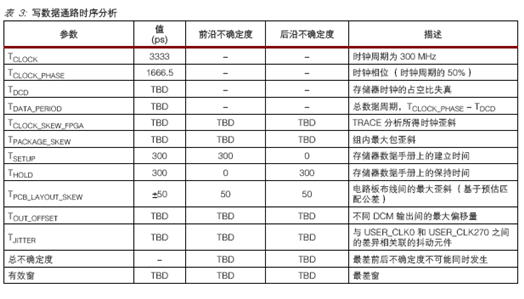

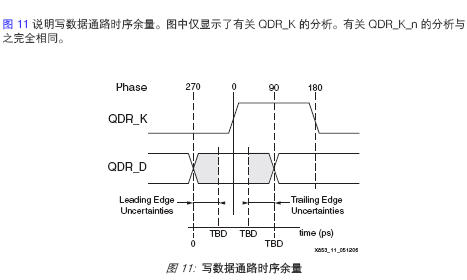

提要 本应用指南说明了利用 Virtex-5 器件实现 4 字突发四倍数据速率 (Quad Data Rate, QDR II)SRAM 接口及其时序的详细信息。此可综合的参考设计利用 Virtex-5 系列独有的 I/O 和时钟控制功能,实现了 300 MHz (600 Mb/s) 的性能水平,使每个 36 位存储器接口的总流量达到 43.2Gb/s。 此设计在最大限度降低资源使用量的同时还大幅简化了在 FPGA 内采集读数据的任务。此方案提供了一个简单的用户接口,可通过利用一个或多个 QDR II 接口简便地集成到一个完整的FPGA 设计中。 简介 QDR SRAM 器件为满足更高的带宽存储要求而开发,以网络和电信应用为目标。基本 QDR 架构具有独立的读、写数据通路,便于同时操作。每个时钟周期内,两个通路均使用双倍数据速率 (DDR) 传输发送两个字,一个在时钟上升沿发送,一个在时钟下降沿发送。结果,在每个时钟周期内会传输四个总线宽度的数据(两个读和两个写),这就是四倍数据速率的由来。 QDR I 和 QDR II 的规范由 QDR 联盟(Cypress、IDT、NEC、Samsung 和 Renesas)共同定义和开发。有关 QDR 规范、QDR 联盟和 QDR 存储器产品的其他信息,请参考第 16 页上的“参考”。 QDR 存储器器件以 2 字突发和 4 字突发架构提供。针对每个读或写请求,2 字突发器件传输两个字。DDR 地址总线用于在前半个时钟周期允许读请求,在后半个时钟周期允许写请求。与之相反,4 字突发器件针对每个读或写请求传输四个字,这样便只需要一个单倍数据速率 (SDR)地址总线,就能最大程度地利用数据带宽。读、写操作请求必须在交替的时钟周期(即不重叠的时钟周期)内进行,以分享地址总线。 本应用指南所讨论的参考设计针对的是 4 字突发 QDR II SRAM 器件。QDR II 架构的独特性能之一是源同步回送时钟 (CQ) 输出,它与器件输入时钟 (K) 频率相同,与通过读通路输出 (Q) 传输的数据边沿对齐。CQ 时钟输出使用 QDR II 存储器器件内的延迟锁定环 (DLL) 电路被重新安排,使其与 Q 数据输出对齐。对于在远端器件上进行的读数据采集操作,此种时钟传输(亦称源同步)接口方法允许较大的时序余量。 第 2 页图1 的时序图表示 4 字突发 QDR II 存储器接口上的并发读/ 写操作。QDR II 存储器的所有输入与输入时钟(K 和 K)同步,传输给存储器时,数据中心通常与输入时钟 K 及 K 边沿对齐。 注: 低有效的读控制 (R) 和写控制 (W) 引脚在时钟周期内交替出现,以实现单独 SDR 地址总线 (SA) 的共享。 写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写控制引脚激活后的下一个K时钟上升沿。读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和 CQ 源同步回送时钟输出边沿对齐。在 CQ 时钟输出的上升沿(紧随 K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送。 在从数据输入 (D) 字中选择要写入存储器的特定字节时,QDR II 存储器还可使用低有效的字节写 (BW) 使能引脚。为清晰起见,图1 中省略了这些信号。  图1 的时序图表示 2 字突发 QDR II 存储器接口上的并发读/ 写操作。在时钟的前半个周期,DDR 地址总线允许读地址被传输给存储器;在时钟的后半个周期,DDR 地址总线允许写地址出现于其中。因此,低有效的读控制 (/R) 和写控制 (/W) 引脚可在同一时钟周期内设定。 两个写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写地址有效前的那个 K 时钟上升沿。读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和 /CQ 源同步回送时钟输出边沿对齐。在 /CQ 时钟输出的上升沿(紧随 /K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送。 设计概述 图2 为 Virtex-5 QDR II 参考设计的高层次框图,表明了 QDR II 存储器器件的外部连接以及用于发送读/ 写命令的 FPGA 内部资源接口。  在图2 中,QDR II 器件的 C 和 C 引脚均被设定为 High。 如第 4 页图3 所示,Virtex-5 QDR II 参考设计由以下四个主要部分组成: 用户接口 物理接口 读/ 写状态机 延迟校准状态机  此用户接口使用完全基于 SDR 信号的简单协议创建读/ 写请求。此模块主要由 FIFO16 基元构成,用于在读/ 写操作执行前后存储相应的地址和数据值。有关用户接口时序协议的详情,请参阅第 5 页“用户接口”。 读/ 写状态机主要负责监控用户接口模块内 FIFO 的状态,调整用户接口和物理接口间的数据流,并向外部存储器器件发送实际读/ 写命令。此状态机确保读/ 写操作按照 QDR II 存储器规范的要求,以并发方式在最短延迟内完成。 物理接口负责生成正确的时序关系和 DDR 信号,以便以符合其命令协议和时序要求的方式与外部存储器器件通信。 延迟校准状态机是物理层中一个不可分割的组成部分,大大简化了在 FPGA 内采集读数据的任务,同时又可实现最佳性能。Virtex-5 器件的每个输入引脚都包含一个可动态调整的可编程延迟元件 (IDELAY),用于控制 5 ns 窗口中输入通路上的延迟时间。延迟校准状态机利用此独特功能调整从存储器器件返回的读数据的时序,因此它无需任何复杂的数据采集技术即可直接与全局 FPGA 系统时钟 (USER_CLK0) 实现同步。 第 5 页表1 总结了 Virtex-5 QDR II 参考设计的规范,包括性能目标和器件应用细节。  实现详情 实现QDR II 参考设计的目的是利用 Virtex-5 系列的独特功能。I/O、时钟控制和存储元件技术方面的发展使此设计的高性能和全承包操作得以实现。以下部分对此设计的实现给出进一步的详细说明。 用户接口 用户接口模块利用六个 FIFO16 模块来存储读/ 写操作的地址和数据值。三个 FIFO16 模块用于写命令,一个用于存储写地址 (USER_AD_WR) 和字节写使能 (USER_BW_n) 信号,另外两个用于存储要写入存储器的 Low (USER_DWL) 和 High (USER_DWH) 36 位数据字。读命令也使用三个 FIFO16 模块,一个用于存储读地址 (USER_AD_RD),另两个用于存储由于执行读而从存储器中返回的 Low (USER_QRL) 和 High (USER_QRH) 36 位数据字。 第 6 页图4 表示使用 4 字突发参考设计时,向用户接口发送读/ 写请求所需的时序协议。如前所述,此接口使用了所有已与主 FPGA 设计系统时钟 (USER_CLK0) 同步的 SDR 信号。  写请求在 USER_CLK0 上升沿期间通过低有效的 USER_W_n 信号创建。此 18 位写地址(USER_AD_WR) 必须在此同一时钟边沿传输。此时,要写入存储器的第一个和第二个 36 位数据字也会分别传输给 36 位 USER_DWL 和 USER_DWH 输入总线。4 字突发的第三个字和第四个字会在下一个 USER_CLK0 上升沿分别传输给 USER_DWL 和 USER_DWH。 读请求在 USER_CLK0 上升沿期间通过低有效的 USER_R_n 信号创建。此 18 位读地址(USER_AD_RD) 必须在此同一时钟边沿传输。执行读命令后,4 字突发值存储于读数据 FIFO中。在 USER_CLK0 上升沿,一个低有效的 USER_QEN_n 信号会检索这些值并将其传输至 36位 USER_QRL 和 USER_QRH 输出。第一和第二个字在首个周期中传输,此时的USER_QEN_n 设置为 Low,紧接着是第三和第四个字在随后一个周期中传输,此时的USER_QEN_n 也设置为 Low。 与 QDR II 存储器本身不同,用户接口在同一时钟周期接受读、写请求(如图4 所示的第三个周期)。读/ 写状态机管理向外部存储器器件所发送的读与写请求的交替,使用户接口免于承担这项职责。 用户接口还提供了一批用于指示读/ 写 FIFO 状态的信号,在图4 中未显示。高有效的 USER_WR_FULL 输出表明写 FIFO 已满。此情况表明,写请求队列缩减之前将不再接受任何写请求。USER_WR_FULL 为 High 时创建的任何写请求都将被直接忽略。类似情况适用于读请求的 USER_RD_FULL 信号。 高有效的 USER_QR_EMPTY 输出表明不再有读数据值存储在读数据 FIFO 中。在此情况下从USER_QRL 和 USER_QRH 总线读值的尝试将被忽略。此情况会一直持续,直到执行其他读命令并且有相关数据值存入读数据 FIFO。 读/ 写状态机 第 8 页图5 为 4 字突发读/ 写状态机的状态图。此状态机负责调节用户接口和物理接口之间的数据流。它根据保存在用户接口 FIFO 中的请求向外部存储器器件发送读/ 写命令。 USER_RESET 每次都会将状态机恢复到 INIT 状态,此时存储器暂停运行,直到延迟校准状态机完成所有 QDR_Q 输入的 IDELAY 模块上的延迟调整,使读通路数据与 FPGA 系统时钟(USER_CLK0) 中心对齐。校准操作完成的信号是一个高有效的 DLY_CAL_DONE 输入,该输入将读/ 写状态机转换到空闲状态,以等候来自用户接口的读/ 写请求。 在空闲状态,写命令首先假设向存储器写数据必须始终发生在任何有效读数据出现之前。当没有待处理的读或写请求时,此状态机将在空闲状态下循环运行。 用户接口 FIFO 中的待处理写请求会使状态机转入写状态,在此状态下,写命令通过内部的WR_INIT_n 选通脉冲发送。此选通脉冲从 FIFO 中取出写地址和数据值,并使外部 QDR_W_n写控制选通脉冲进入存储器器件。 如果包含待处理读请求,此状态机会随之转入读状态,此时内部 RD_INIT_n 选通脉冲被激活。RD_INIT_n 选通脉冲从 FIFO 中取出读地址,并向存储器器件发送一个外部 QDR_R_n 选通脉冲。作为此处理过程的结果之一,对读数据 FIFO 中的返回值也将进行采集。 读/ 写状态机持续监控用户接口 FIFO 状态信号,以确定是否存在待处理读/ 写请求。连续不断的并发读/ 写请求流将导致状态机只在读状态和写状态之间转换,以确保正确无误地将请求交替发送到外部存储器。一串只写请求将导致空闲状态和写状态轮流出现,同样,一串读请求也会在空闲状态和读状态间转换。  物理接口 Virtex-5 QDR II 参考设计的物理接口为读/ 写命令与外部存储器器件之间的通信生成实际的I/O 信号和时序关系,包括 DDR 数据信号。它提供必要的时序余量及为满足整体设计性能规范所需的 I/O 信号标准。QDR II 设计的所有 I/O 信号都使用 HSTL-I 发送。此部分详细介绍物理接口的每个部件。 时钟控制机制 此 QDR II 设计使用的是所有 Virtex-5 I/O 模块中都有的输出 DDR (ODDR) 基元。这些内置DDR 寄存器功能极大地简化了以下任务:生成准确的时钟、地址和数据,以及与 QDR II 存储器器件通信的控制信号。IDDR 和 ODDR 基元都有多种运行模式,可分别确定采集或传输的DDR 数据以怎样的方式出现在 FPGA 内部资源和 I/O 引脚中。 QDR II 设计中的时钟控制机制(第 9 页图6)使用反沿 (opposite-edge) 模式的 ODDR 寄存器来为存储器器件生成 QDR_K 和 QDR_K_n 时钟。因为时钟信号的时序与 QDR II 地址、数据和控制信号几乎相同,此时钟传输机制会有效地从时序余量因素中删除 FPGA 的 clock-to-out参数。因此,就 clock-to-out 参数而言,所有外部传输信号都得以“匹配”。  写通路 QDR II 存储器的写通路包括执行写操作所必需的地址、数据和控制信号。写地址 (QDR_AD_WR)、控制选通脉冲 (QDR_W_n) 和字节写使能 (QDR_BW_n) 信号都使用 SDR 格式。不过,写数据值 (QDR_D) 利用 DDR 信号在规定的时钟周期实现所需的 2 字或 4 字突发。 所有这些写通路信号在传输时都必须与 QDR_K 和 QDR_K_n 时钟边沿中心对齐。因此,这些信号的输出寄存器与 USER_CLK270 时钟同步。信号以同样的频率运行,但对于 USER_CLK0则会出现 270°(时钟周期的 75%)的相差。这能确保对输入 QDR_K 和 QDR_K_n 时钟边沿而言,存储器器件有足够的建立与保持余量。 第 10 页图7 说明了如何使用 USER_CLK270 和 ODDR 寄存器为 QDR_D 写数据通路生成所需的 DDR 信号。ODDR 寄存器配置为同沿 (same-edge) 模式,允许在 USER_CLK270 的同一上升沿从 FPGA 架构中同时采集两个 36 位数据字(FIFO_DWL 和 FIFO_DWH)。FIFO_DWL 值在此上升沿后立即发送到 QDR_D 写数据总线,随后,FIFO_DWH 值在 USER_CLK270 的下一个下降沿从 ODDR 模块发送。对此过程加以重复,以生成一个 4 字写数据突发。 使用 I/O 模块中的单个触发器以类似的方式生成读/ 写地址、字节写使能和读/ 写控制选通脉冲,以创建与 USER_CLK270 同步的 SDR 信号。  读数据通路 基于 CQ 的数据采集机制可以实现以极高的时钟速率从存储器中采集读数据。此数据采集机制使用在每个 I/O 中都提供的 ISERDES 功能。输入时钟 (CQ) 和数据 (Q) 经延迟后与 ISERDES 模块中的系统时钟 (CLK0) 保持同步。 读数据通路包括两个阶段:读数据采集和读数据重新采集。两个阶段均在各个 Virtex-5 I/O 的内置 ISERDES 中实现。途经 BUFIO 的 CQ 信号将采集 ISERDES 模块内首组寄存器中的输入读数据 (Q)。第二组寄存器用来将 CQ 域中的数据传输至系统时钟域。 ISERDES 具有三种时钟输入:CLK、OCLK 和 CLKDIV。读数据 (Q) 在 CLK (CQ) 域经采集完成后,通过 OCLK 和 CLKDIV 传输至系统时钟(图8): CLK:布线通过 BUFIO 的读时钟 (CQ) 提供 CLK 时钟输入。 OCLK 和 CLKDIV:这些时钟负责对输入数据进行串并转换。由于数据以与接口速度相同的频率进行传输,系统时钟 (CLK_0) 提供针对 OCLK 和 CLKDIV 的输入。 在ISERDES 中采集到的数据可以被写入 Virtex-5 FPGA 中的内置 FIFO36 模块。  基于 CQ 的数据采集机制要求将读时钟(CQ 和 CQ)置于 clock-capable I/O (CCIO) 中,时钟从这些位置可以访问各组 (bank) 内可用的 BUFIO。 对于 x36 宽的 QDR II SRAM 接口,CQ_P 和 CQ_N 均用来采集读数据(第 11 页图9)。一个Virtex-5 器件中的每个组都包含 40 个 I/O,因此一个 x36 接口的读数据需要置于两个组中。 CQ_P 用来采集一个组中的首组字节,而 CQ_N 用来采集相邻组中剩余的数据字节。CQ_P 和CQ_N 均需置于相应组中 CCIO 的 P 侧。  延迟校准 延迟校准逻辑负责提供读数据 (Q) 和时钟 (CQ) 所需要的延迟,以便将采集到的数据与 FPGA时钟中心对齐。当来自 IDELAYCTRL 的 IDELAY_READY 信号设定为 High,且存储器初始化所需的时钟周期得到满足时,延迟校准状态机就会启动。校准过程包含单次写,随后向同一位置连续进行读,直到找到 Q 和 CQ 信号正好需要的延迟值。读校准开始后,校准状态机会执行以下步骤: 1. 增加 CQ 和 Q 上的 tap 延迟值。如果在某个 tap 值上初次获取了有效数据,则此 tap 值标志着数据有效窗口的开端。 2. 继续增加 CQ 和 Q 的 tap 延迟值,直到达到有效窗口的终端。 3. 将 CQ 置于此有效窗口的中央。降低 tap 值,直到 CQ 被固定于数据有效窗口的中央。 4. 对于 CQ 和 FPGA 时钟,数据总线 (Q) 将置于中央。重新设置 Q 的 tap 值,即可针对 CQ和系统时钟 (CLK0) 得出 Q 的有效窗口。对于 CQ 和 FPGA 时钟,数据信号 (Q) 将置于中央。 当所有 Q 信号围绕 CQ 固定后,延迟校准过程就结束了,并继之以读使能校准。 读使能逻辑对向存储器发送的读命令进行校准,为已采集到并写入读数据 FIFO 的数据生成写使能。校准逻辑使用 SRL16 构建而成,有助于确定读命令信号所需寄存器级数的数量,以生成正确的写使能信号。 板设计中的考虑因素 尽管 Virtex-5 系列产品提供了许多与 I/O 和时钟控制相关的高级功能,大大简化了存储器接口设计,但为了使接口可靠而高效,仍需注意基本的电路板设计标准。 需特别强调的是,读和写通路接口的源同步特性要求接口时钟、数据及控制信号具有相匹配的电路板布线长度。 例如,QDR II 器件输入信号(QDR_K、QDR_K_n、QDR_W_n、QDR_R_n、QDR_SA、QDR_BW_n 和 QDR_D)的布线长度必须完全匹配,以将控制、地址及数据线接至具备充足建立与保持余量的存储器器件。物理接口的实现可确保这些信号在离开 FPGA 器件输出时与QDR_K 和 QDR_K_n 时钟边沿中心对齐。电路板布线必须确保这种关联状态能持续到存储器器件输入。 同样,QDR II 器件输出信号(QDR_Q、QDR_CQ)必须具备完全匹配的布线长度,以使这些信号在 Virtex-5 器件的输入端实现边沿对齐。要实现直接时钟控制读数据采集方法,这一点非常关键。所有合理的板设计工具都可以在可接受的容错范围内轻松满足这些布线长度。 时序分析 本 Virtex-5 QDR II 参考设计利用该器件的独特 I/O 和时钟控制功能,可最大限度地提高性能与时序余量,同时大大降低对详细布局和管脚分配分析的需求。 本部分针对地址/ 控制通路、写数据通路及读(或采集)数据通路给出一个时序分析示例。 地址/ 控制通路 先前已讨论过,读/ 写地址总线、字节写使能信号和读/ 写控制选通脉冲都与USER_CLK270时钟保持同步。这可以确保,对于来自 USER_CLK0 的输入 QDR_K 和 QDR_K_n 时钟边沿,这些 SDR 信号具备对存储器器件的有充足的建立与保持余量。 表2 根据用一个 Virtex-5 器件实现的 300 MHz 4 字突发 QDR II 存储器器件接口,显示针对这些信号的一个时序分析示例。   写数据通路 写数据 (QDR_D) 也与 USER_CLK270 保持同步。不过,写数据字作为 DDR 进行发送,因此在QDR_K 和 QDR_K_n 上升沿均需具备充足的建立与保持余量。相应地,表3 所示写通路的时序分析包括了存储器时钟的最大占空比失真,并基于 300 MHz 4 字突发 QDR II 存储器器件及速度级别为 -11 的 Virtex-5 器件。   读数据通路(数据采集) 读数据通路 (QDR_Q) 值直接被采集至 SERDES 内的 USER_CLK0 时钟域。表4 显示读数据采集的时序分析。  结论 本应用指南说明了利用 Virtex-5 器件实现 4 字突发 QDR II SRAM 接口及其时序的详细信息。 数据采集机制的应用大大简化了在 FPGA 内采集读数据的任务,且为当前及下一代 QDR IISRAM 存储器器件提供了高效、强大、可扩展的存储器接口解决方案。 此 QDRII 参考设计可从 Xilinx 网站下载:http://www.xilinx.com/cn/bvdocs/appnotes/xapp853.zip |

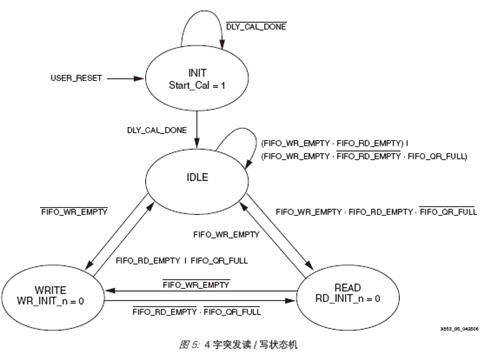

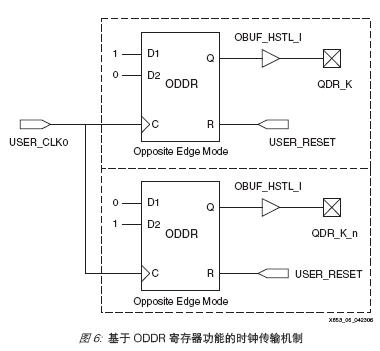

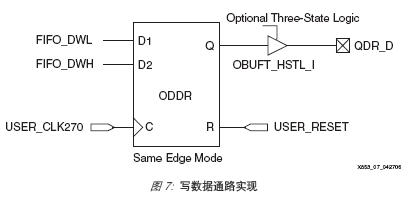

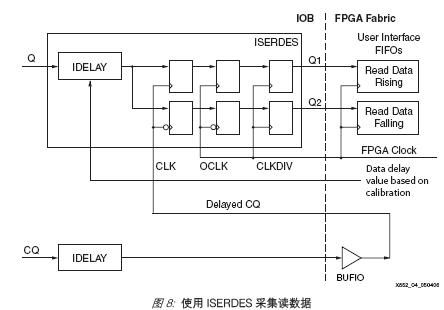

网友评论