30GHz示波器助推高速串行信号测试迈入新时代

发布时间:2009-5-22 14:28

发布者:李宽

|

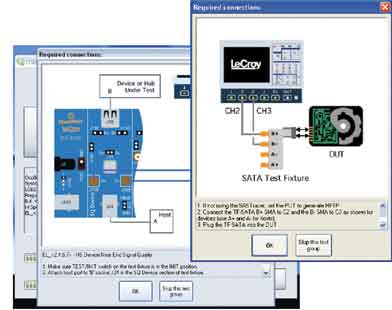

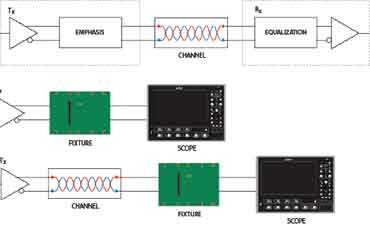

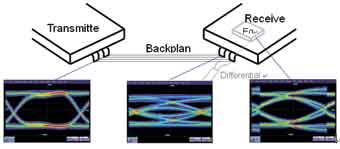

高速串行信号带来的测试挑战 消费者对通信和计算机产品的要求越来越高,不断提升的速度、不断增长的容量,但却不能成正比变化的价格,成为用户决定是否掏钱购买新款产品的基本要求。这些来自终端客户的需求通过产业链逐级传递到产品研发工程师对测试仪器的需求层面。能设计出超高数据传输速率的通信产品,就一定需要性能匹配的信号测试工具,否则无法保证最终产品的性能、质量和一致性。 五年前,数据吞吐率在3.125Gb/s的通信系统背板只是停留在少数顶尖通信设备商预研阶段的概念,2.5Gb/s的PCI-ExpressG1协议也只是售价昂贵的高端通信产品才具备的内部互连总线。而如今,传输能力达6.25Gb/s高速背板已经非常普遍的应用在通信设备上,单对线吞吐率高达12Gb/s的串行背板总线在技艺精湛的工程师手上也即将变为现实。更高传输速率达5.0Gb/s的PCI-ExpressG2也早已是普通PC声卡、显卡的标准配置。而实际上,高达8Gb/s的PCI-ExpressG3总线标准也将在2009年正式面世,还有4.8Gb/s的USB3.0接口、6.4Gb/s的FB-DIMM存储器架构,乃至10Gb/s的Serial Rapid I/O串行协议等。 5Gb/s以上新串行协议层出不穷,面对这么高速的测试信号,需要全新的思维:因为测试仪器本身已经构成了工程师诊断问题的障碍,示波器主机、探头、测试夹具、电缆对被测信号哪怕是一点点的破坏,也可能让你得出与事实完全相反的结论,这不仅需要示波器具备更高放大器带宽和采样性能,而且能够去除由于测试设备的引入而对被测电路带来的负面效应;另一方面串行协议内容越来越复杂,需要更高级的分析软件和仿真模型来深入洞察问题的本质。这两方面催生工程师对测试设备的需求不断提高,同是也给测试仪器厂商带来巨大的挑战。 为工程师提供匹配眼下乃至未来一段时间内高速串行信号测试需求的数字示波器,降低工程师测试信号的难度和复杂度,让他们把主要精力集中在产品设计上,而不是产品测试上,是具有领导地位的测试仪器产商不可推卸的责任。  图1 QualiPHY串行协议一致性测试界面 满足高速串行信号测试的高带宽高采样示波器 WaveMaster8Zi系列示波器及串行数据分析仪,为工程师测试新一代高速串行信号提供了全面的解决方案。这款示波器的基本性能包括:最高达30GHz前端采集带宽、最高达80GS/s的实时采样率、最深达512Mpts的可分析波形内存,大于15GHz的边沿触发带宽、最长达80bit的串行触发能力,以及标配比传统方法更精确的眼图和抖动测量软件包—SDA II,串行协议一致性分析集成化工具—QualiPHY,为分析高速串行链路信号完整性而量身定制的EyeDoctorII软件包,这些示波器行业的多项创新设计为工程师分析从100Mb/s的百兆以太网到12Gb/s的高速通信背板信号质量都提供了坚实的技术基础。由于版面有限,关于该产品的详细介绍请参阅其网站http://www.lecroy.com。 创新的高速串行数据分析方案 SDA 8 Zi串行数据分析仪基于WaveMaster 8 Zi系列示波器,标配存储器提高了一倍,可以捕获眼图中更多的单位间隔。同时拥有增强的高速串行码型触发功能,支持高达80位码型,工作速度高达3.125Gb/s。 SDA8Zi标配的串行数据分析平台——SDAII功能非常全面,包括基于NQ-Scale技术的抖动分解方法及更精确的抖动分类工具,提高了工程师测量高速信号微小抖动的信心,也提供了更全面的洞察力,深存储时的眼图生成速度要比传统示波器快20~100倍,可以在3秒内捕获、分析和显示近100万个PCIExpress单位间隔。其他工具如IsoBER(由已捕获的眼图去推测更长时间的眼图闭合情况)和模板违规定位器,可以简便地了解复杂的问题。电缆补偿功能可以去掉电缆失真影响,在高速眼图上更准确地测量定时和幅度。新推出的SDA 8Zi分析仪同时标配眼图、时间间隔误差、浴盆曲线、抖动直方图及其他抖动分类分析等多个完整的视图。使用QuickView(快速查看)功能,工程师可以快速“一键”了解到串行信号的全貌,包括眼图和抖动的多角度视图。 在一致性测试阶段,可以对各种既定标准使用自动化QualiPHY软件,如PCIe、SAS、SATA、HDMI、DisplayPort和XAUI。图1所示为QualiPHY分析SATA一致性的操作界面,整个操作过程便捷,全面覆盖标准规定的测试项目,并能自动输出美观实用的测试报告。 创新的信号完整性分析方案 为了在最困难的测量环境中测试最快速的新兴技术,需要使用带宽高达30GHz的示波器。在50ps上升时间或2.5Gb/s以下数据速率表现得不太明显的测试挑战,在上升时间接近或变成小于25ps或信息速率超过5Gb/s时成为不可规避的问题。在这些速度下,工程师面临着以前只限于微波频域的信号完整性问题,如不理想的测试夹具和连接电缆的负载效应会从被测电路中汲取能量,从而降低幅度和相位测量的保真度。实现下一代高速串行数据标准的工程师面临着更快速、更复杂的信号挑战,与此同时,串行数据通道(互连、传输线、背板)速度并没有同步提高,导致串行数据通道中的信号劣化问题。另外,新兴串行数据标准如USB3.0,要求模拟(仿真)信号传输路径,在所有用户环境中都保证可靠的性能。最后,串行数据接收机硬件是为平衡信号劣化专门设计的,但工程师没有任何途径直接探测到SerDes接收端芯片内部应用了均衡优化后的被测信号的性能,道理很简单,因为没有任何办法可以将探头伸入到芯片内部。 解决方案是力科Eye Doctor II信号完整性系列工具,它提供了电缆和测试夹具反嵌功能、预加重和去加重建模功能、串行数据通道仿真功能和串行数据接收机均衡功能。Eye Doctor II能够对图2所示典型的串行链路进行建模并仿真各个部分对信号的影响:  图2 Eye Dr II对应的串行链路模型  图3 Eye Doctor II对串行信号均衡仿真效果 WaveMaster8Zi支持对串行通道或测试夹具使用工业标准的S参数描述,支持最多到16端口的信道模型,并将每个S系数以Plot的形式绘制在屏幕上,方便客户多角度观测信道质量。获得S参数文件的方法包括采用矢量网络分析仪或力科WaveExpert取样示波器的TDR模块,或采用专门的EDA仿真软件。对均衡器的描述有两种方法:第一,有经验的工程师可以输入均衡器内部每个抽头的准确参数;第二,只需输入基本的信号参数如数据率、门限判别电平等,EyeDoctorII会训练出一套最优化的抽头系数。图3是对芯片Pin测得已接近闭合的眼图在均衡仿真后的眼图,可以看出,对均衡后的信号做眼图和抖动分析更有意义。 |

网友评论