ДІРэЦїЕФИпаЇТЪЕчдДЙмРэ

ЗЂВМЪБМфЃК2010-10-10 13:30

ЗЂВМепЃКconniede

|

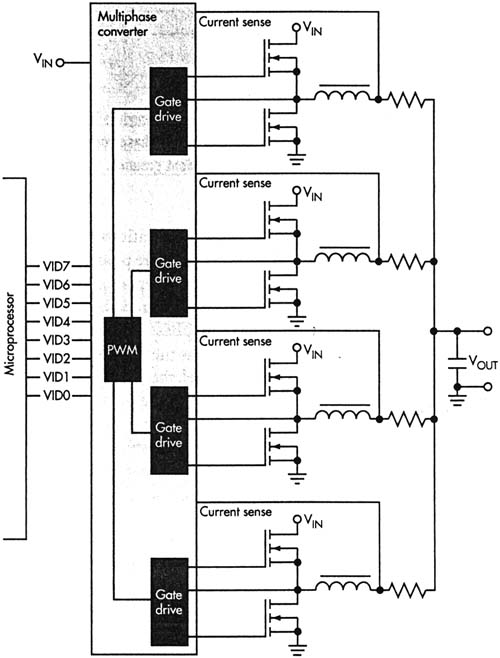

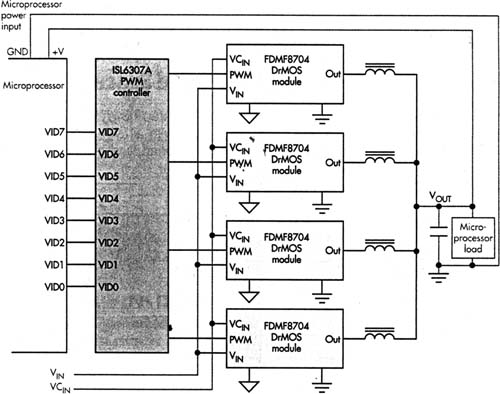

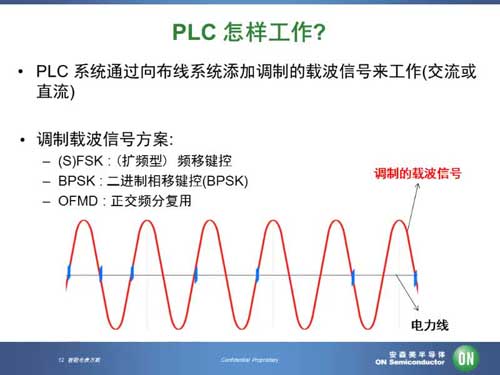

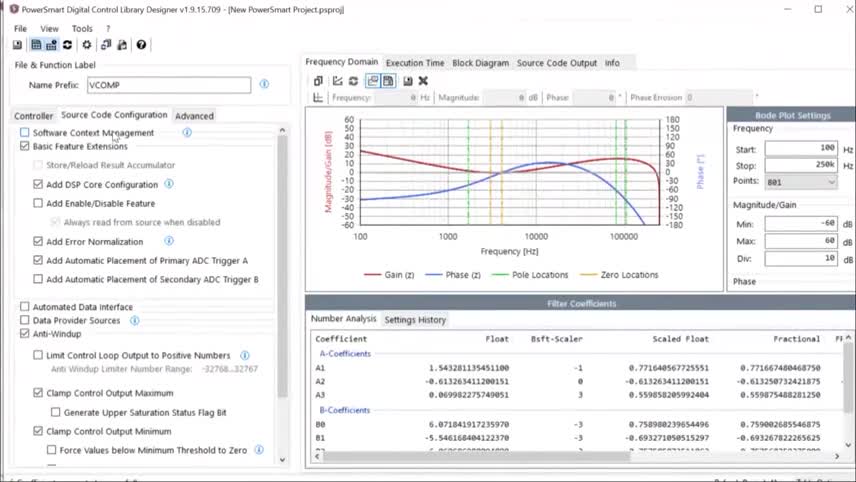

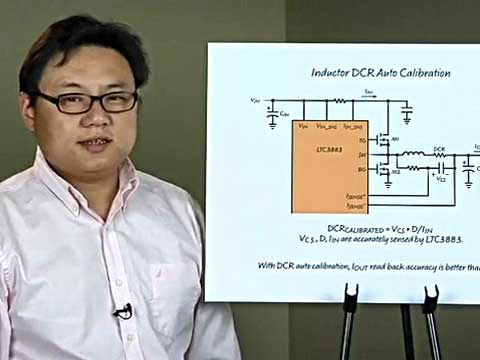

дЄВтЕН2010ФъЃЌДІРэЦїНЋЙЄзїдк1VКЭ100AЕчСїЃЌЕН2020ФъЯЃЭћДІРэЦїЕФЕчдДЕчбЙНЋЪЧ0.7VКЭИќИпЕчСїЁЃДІРэЦїЙЄзїдк1VЃЌ100A(ЛђИќИп)КЭGHzЦЕТЪЪБЕФИпаЇЕчдДЙмРэГЩЮЊЩшМЦШЫдБУцЖдЕФРЇФбШЮЮёЁЃ ЩшМЦШЫдБПЩвдЬсЙЉЕЭЕчбЙЁЂДѓЕчСїЮЂДІРэЦїЕчдДЁЃЕЋдіМгИпаЇТЪ(90%ЛђИќИп)ЕФвЊЧѓЪБЃЌВЩгУЕБНёЕФдЊМўКЭММЪѕПЩДяЕНЕФаЇТЪЮЊ70%~80%ЁЃ 1 VRDХфжУ VRD(Voltage regulator-down)ХфжУАбЫљгадЊМўжБНгАВзАдкМЦЫуЛњФИАхЩЯЃЌЮЊДѓВПЗжДІРэЦїЙЉЕчЁЃДѓВПЗжVRDга8ЮЛЕчбЙЪЖБ№(VID)ТыЃЌЦф8ЮЛЪфШыЯпжБНгСЌНгЕНДІРэЦїЕФЯргІ8ИіVIDв§НХЁЃдкЕчбЙЮШбЙЦїИљОнИаВтЦїЕФЮЂДІРэЦїVIDТыЃЌЩшжУДІРэЦїЫљашЕФЙЄзїЕчбЙЁЃДІРэЦївВПЩвдВЩгУЖЏЬЌЕчбЙЪЖБ№РДИФБфЪБжгЦЕТЪКЭЙЄзїЕчбЙЃЌвдЯьгІДІРэЦїЕФЙЄзїИКдиКЭШШЯьгІЁЃ IntelЙЋЫОVRD11.0ДІРэЦїЕчдДЙЉЕчЩшМЦжИФЯжаЃЌЮЊ5ИіВЛЭЌДІРэЦїИјГіЫљгУЕчдДЩшМЦжИФЯЮЊЃК ЁЄзюИпЕчдДЕчбЙЃК1.4V~1.425V; ЁЄзюДѓЕчСїЃК75A~125 A; ЁЄдкЫљгаЯпТЗЁЂИКдиКЭЛЗОГЬѕМўЯТЃЌбЯИёЕФЪфГіЕчбЙЕїећЁР5%; ЁЄЗЧГЃЕЭЕФЮЦВЈЃЌЭЈГЃаЁгк10mVrmsp-p; ЁЄаЇТЪ75%~80%; ЁЄПьЫйЫВЬЌЯьгІЃЌгыЮЂДІРэЦїЪБжгЦЕТЪвЛжТ; ЁЄЙ§бЙБЃЛЄ; ЁЄЙ§Сї(ЖЬТЗ)БЃЛЄ; ЁЄЙ§ЮТБЃЛЄ; ЁЄЙІКФдЊМўЕФШШЙмРэ; ЁЄЯрЕБаЁЕФЗтзАГпДчЃЌЪЙЕчдДПЩвдАВжУдкППНќЮЂДІРэЦїИКдиДІЁЃ 2 ЖрЯрБфЛЛЦї ПЩвдТњзуЕБНёДІРэЦїЕчдДвЊЧѓЕФЮЈвЛЭиЦЫЪЧЖрЯрПЊЙиФЃЪНБфЛЛЦїЁЃетжжБфЛЛЦїВЩгУСНИіЛђИќЖрЯрЭЌЁЂзщКЯЕЅдЊЃЌАбетаЉЕЅдЊЪфГіСЌНгЦ№РДЃЌЦфЪфГіЪЧЫљгаЕЅдЊЪфГіЕФзмКЭ(ЭМ1)ЁЃ  ЭМ1 ЫФЯрЕчбЙЮШбЙЦїгУЗжРыЕФеЄМЋЧ§ЖЏЦїЁЂЗжСЂЕФЙІТЪMOSFETsКЭ1ИіЗжРыЕФPWMПижЦЦїЃЌгыЮЂДІРэЦїСЌНгПП8ЮЛVIDТы ЮЊСЫРэНтЖрЯрБфЛЛЦїЕФгХЕуЃЌЪзЯШПДПДЕЅЯрБфЛЛЦїЬсЙЉДѓЕчСїКЭЕЭЕчбЙЪБЕФШБЕуЁЃгУвЛАуЕЅЯрБфЛЛЦїЃЌЦфЪфГіуыВЈКЭЖЏЬЌЯьгІЕФИФЩЦЪЧППЬсИпЙЄзїЦЕТЪЁЃ СэЭтЃЌдкНЯИпЦЕТЪЪБЃЌЪфГіЕчИаЦїКЭЪфГіЕчШнЦїЕФЮяРэГпДчКЭЪ§жЕБфаЁЁЃдкЦЕТЪДяЕНвЛЖЈЯожЕКѓЃЌБфЛЛЦїПЊЙиЫ№КФдіДѓЃЌаЇТЪЯТНЕЁЃетЦШЪЙдкЙЄзїЦЕТЪКЭаЇТЪЗНУцзіЩшМЦелждЁЃ ЮЊСЫПЫЗўетаЉЕЅЯрЦЕТЪЯожЦЃЌЖрЯрЕЅдЊЙЄзїдквЛИіЙВЭЌЕФЦЕТЪЃЌЕЋвЦЯрНсЙћЪЧБфЛЛПЊЙиЗЂЩњдкгЩЙВЭЌПижЦаОЦЌПижЦЕФЙцдђМфИєФкЁЃПижЦаОЦЌНЛДэХХСаУПИіБфЛЛЦїЕФПЊЙиЪБМфЃЌЫљвдЃЌУПИіБфЛЛЦїПЊЙижЎМфЕФЯрЮЛНЧЪЧ360?/n(nЪЧБфЛЛЦїЕЅдЊЪ§)ЁЃвђЮЊЕЅдЊЪфГіЪЧВЂСЊЕФЃЌЫљвдЃЌгааЇЕФЪфГіЮЦВЈЦЕТЪЪЧnxf(fЪЧУПИіЕЅдЊЕФЙЄзїЦЕТЪ)ЁЃетжжЗНЗЈОпгаНЯКУЕФЖЏЬЌадФмКЭЯджјаЁЕФШЅёюЕчШн(гыЕЅЯрЯЕЭГЯрБШ)ЁЃ ЕЅдЊЕФЕчСїОљЗжЪЧБиаыЕФЁЃвђДЫЃЌвЛИіЕЅдЊВЛФмЁААдеМЁБДѓЖрЪ§ЕчСїЁЃРэЯыЧщПіЪЧУПИіЖрЯрЕЅдЊгІИУЯћКФЯрЭЌСПЕФЕчСїЁЃЮЊСЫЪЕЯжЯрЕШЕчСїОљЗжЃЌБиаыМрЪгКЭПижЦУПИіЕЅдЊЕФЪфГіЕчСїЁЃ ЖрЯрБфЛЛЦїгаМИИіживЊЕФгХЕуЃКУПИіЕЅдЊЬсЙЉзмЪфГіЙІТЪЕФ1/nЃЌетЪЙЕУУПИіЯрЫљгУЕФЕчИаЦїЕФГпДчЪ§жЕБфаЁ;ШШКФЗжВМгХЕуЃЌвђЮЊУПИіЕЅдЊжаЕФЙІТЪАыЕМЬхжЛашвЊДІРэзмЙІТЪЕФ1/nЃЌетНЕЕЭСЫШЮКЮШШЕуЮТЖШЁЂдіМгСЫПЩППадЃЌВЂдЪаэгаНЯИпЕФзмЙІТЪадФмЁЃ СэЭтЃЌЕШаЇЦЕТЪдіИпВЛЛсеажТНјвЛВНЕФПЊЙиЫ№КФЃЌетПЩвдВЩгУНЯаЁЕФЕШаЇЕчИаЃЌДгЖјЫѕЖЬИКдиЫВЬЌжмЦкЪБМфЁЃЪфГіЕчШнЦїжаНЕЕЭЕФЮЦВЈЕчСїЪЙЪфГіЮЦВЈЕчбЙБфЕЭЃЌетПЩВЩгУИќаЁЛђИќБувЫЕФЪфГіЕчШнЦїЁЃ дкбЁдёЯрЪ§ЪБЃЌгІПМТЧЖрЯрБфЛЛЦїЕФвЛаЉШБЕуЁЃШБЕу1ЃЌашвЊНЯЖрЕФПЊЙиКЭЪфГіЕчИаЦїЃЌетЛсЕМжТНЯИпЕФЯЕЭГГЩБО;ШБЕу2ЃЌашвЊИќИДдгЕФПижЦЃЌетЪЧвђЮЊгаЖрИіБфЛЛЦїЕЅдЊЃЌЯрЛЅжЎМфВЛОљдШЕчСїОљЗжЕФПЩФмадЪЧПЩФмЕФ;ШБЕу3ЃЌдіМгСЫЕчТЗВМЯпЕФИДдгадЁЃ ЫцзХЙЄзїЕчСївЊЧѓЕФдіИпЃЌашвЊгаИќЖрЕФЕЅдЊЯрЁЃвЛИізюМбЕФЩшМЦашвЊелждПМТЧЯрЪ§ЁЂУПИіЯрЕФЕчСїЁЂПЊЙиЦЕТЪЁЂГЩБОЁЂГпДчЕФаЇТЪЁЃИќИпЕФЪфГіЕчСїКЭИќЕЭЕФЕчбЙЃЌашвЊИќбЯИёЕФЪфГіЕчбЙЕїећЁЃЖрЯрЩшМЦПЩВЩгУМИжжЪЕгУЕФЗНЗЈЁЃ вЛжжЗНЗЈЪЧВЩгУДјМЏГЩMOSFETЧ§ЖЏЦїЕФPWM(ТіПэЕїжЦ)ПижЦЦїICЁЃШЛЖјЃЌЦЌЩЯеЄМЋЧ§ЖЏЦїВњЩњЕФШШКЭдыЩљЛсгАЯьПижЦЦїадФмЁЃМЖСЌетРраОЦЌвддіМгИќЖрЯрЪЧВЛЯжЪЕЕФЁЃгУетжжХфжУЪЕЯжОЋШЗЕФЕчСїОљЗжЪЧРЇФбЕФЁЃетжжЗНЗЈ3ЯрЪЧЯожЦЯрЪ§ЁЃ СэвЛжжЗНЗЈЪЧВЩгУЗжРыЕФПижЦЦїКЭЗжРыЕФеЄМЋЧ§ЖЏЦїЃЌЪЙPWMПижЦЦїгыеЄМЋЧ§ЖЏЦїЕФШШКЭдыЩљИєРыЁЃШЛЖјЃЌЕчСїОљЗжЛсИќИДдгЃЌвђЮЊЕчСїИаВтаХКХТЗгЩЕНПижЦЦїЁЃЛЙгаСэЭтЕФПижЦЦї-Ч§ЖЏЦїбгГйЃЌетЪЧвђЮЊЫќУЧЪЧЗжРыЕФICЁЃ СэвЛжжЗНЗЈЪЧВЩгУвЛИіДјМЏГЩеЄМЋЧ§ЖЏЦїКЭФкжУЭЌВНКЭЕчСїОљЗжЕФПижЦЦїЁЃетжжЗНЗЈжЛдЪаэХМЪ§ЯрЪ§ЁЃЫќМђЛЏСЫЩшМЦЃЌЕЋПЩЕМжТЮДгУЛђЖргрЙшЦЌЁЂв§НХКЭЭтВПдЊМўЁЃзюживЊЕФЪЧЦЌЩЯЫљВњЩњЕФЧ§ЖЏЦїШШКЭдыЩљПЩФмЛсНЕЕЭПижЦЦїадФмЁЃ ЫљвдЃЌЯжгаЕФЗНЗЈдкбЁдёЯрЪ§жаВЛФмЬсЙЉЫљашЕФздгЩЖШЁЃРэЯыЕФЗНЗЈЪЧвЛжжПЩЩьЫѕЕФЭиЦЫЃЌЫќФмШнвзЕидіМгЛђШЅГ§ШЮвтЖрЯрЕЅдЊЃЌЖјЧвВЛгАЯьадФмЁЃетжжЗНЗЈБиаыФмЙЛдкЗжВМЕФЯрЕЅдЊжаЯрЕШЕиОљЗжЕчСїЁЃетбљЕФММЪѕЪЙМФЩњаЇгІзюаЁЃЌВЂШнвзАхВМЯпЁЃ 3 DrMOS ХфжУвЛИіМѕаЁГпДчЁЂПЩЩьЫѕЖрЯрБфЛЛЦїЕФвЛжжЗНЗЈЪЧВЩгУDrMOS(Driver-MOSFET)ЙцЗЖ(IntelЙЋЫО2004Фъ11дТЬсГі)ЁЃDrMOSФЃПщАќРЈЧ§ЖЏЦїКЭЙІТЪMOSFET(ЭМ2)ЃЌЩшМЦгУгкЖрЯрБфЛЛЦїЁЃ ЖдгквЛИіDrMOSЦїМўВЩгУЖраОЦЌФЃПщЕФвЛИіжївЊгХЕуЪЧЃЌПЩвдЪЙЕЅЖРMOSFETадФмзюМбЛЏЁЃШЛЖјЃЌЖраОЦЌФЃПщЕФдЊМўГЩБОИпгкЕШаЇЕФЕЅЦЌЗНАИЁЃОЁЙмШчДЫЃЌЩшМЦШЫдБгІДгЯЕЭГЙлЕуПДГЩБОЮЪЬтЁЃ FairchildЙЋЫОЕФFDMF8700ЪЧвЛПюжЇГжIntelЕФDrMOS Vcoredc-dcБфЛЛЦїБъзМЁЂгУгкДѓЕчСїЭЌВННЕбЙгІгУЕФFETМгЧ§ЖЏЦїЕФЖраОЦЌФЃПщЁЃетЪЧвЛИіЭъШЋМЏГЩЕФЙІТЪМЖЗНАИЃЌВЩгУ8ЁС8mm MLPЗтзАЁЃЫќЬцДњвЛИі12VЧ§ЖЏЦїICКЭ3ИіNЙЕMOSFETЃЌгыЗжСЂдЊМўЗНАИЯрБШЃЌНкЪЁАхПеМф50%ЁЃПЊЙиКЭЧ§ЖЏЦїЙмаФЕФВМЯпКЭГпДчЪЧзюМбЛЏЕФЃЌФмЙЄзїдкНЯИпЦЕТЪЁЃ ВЛЯѓЗжСЂЗНАИФЧбљЃЌМФЩњдЊМўгыАхВМЯпвЛЦ№ЯджјЕиНЕЕЭСЫЯЕЭГаЇТЪЃЌFDMF8700ФЃПщЕФШШКЭЕчЦјадФмЃЌЪЙМФЩњаЇгІзюаЁЃЌИФЩЦСЫзмЯЕЭГаЇТЪЁЃдкЙЄзїЪБЃЌИпЖЫMOSFETЖдгкПьЫйПЊЙиЪЧзюМбЕФЃЌЖјЕЭЖЫЦїМўЖдгкЕЭRDS(ON)ЪЧзюМбЕФЁЃетжжХфжУЪЕЯжСЫБфЛЛ12VзмЯпЕНЬсЙЉДІРэЦїаОКЫ1.0V~1.4V(ИпДя30A)ЕчбЙЫљашЧѓЕФЕЭеМПеБШПЊЙиЁЃ FairchildМвзхЕФDrMOSЖраОЦЌФЃПщАќРЈFDMF6700ЃЌFDMF8704ЃЌFDMF8704КЭFDMF8705(МћЭМ3)ЁЃ  ЭМ2 DrMOSФЃПщАќКЌЧ§ЖЏЦїКЭЙІТЪMOSFETsЁЃПижЦЕчТЗКЭЪфГіМЖОпгаЖРСЂЕФЕи Renesas Technology AmericaЙЋЫОЕФRZJ20602NPМЏГЩвЛИіЧ§ЖЏЦїICКЭИпЁЂЕЭЖЫЙІТЪMOSFETдк56в§НХQFNЗтзАжаЁЃетжжЕкЖўДњЧ§ЖЏЦї-MOSFETВњЦЗЙЄзїдкИпДя2MHzПЊЙиЦЕТЪЃЌЦфзюДѓЪфГіЕчСїЮЊ40AЁЃЙЄзїдк1MHzЃЌVIN=12VЃЌVOUT=1.3VЪБЃЌзюИпаЇТЪНгНќ87%ЁЃдк25AЪфГіЕчСїЪБЃЌЙІКФжЛга4.4WЁЃ NXPЙЋЫОЕФNXP PIP212-12MвВТњзуDrMOSЙцЗЖЁЃЫќгЩИпЖЫ(ПижЦFET)ЁЂЕЭЖЫ(ЭЌВНFET)КЭFETЧ§ЖЏЦїзщГЩЁЃЫќПЩвдгУзіНЕбЙЮШбЙЦїЙЙНЈЕЅдЊЃЌУПЯрДѓгк30AЕчСїЁЂЙЄзїЦЕТЪИпДя1MHzЁЃ SemtechЙЋЫОЕФSC2447ЪЧвЛПюИпЦЕТЪЁЂЫЋЯрPWMНЕбЙПижЦЦїЃЌЖдгкPhilipsКЭRenesas DrMOSЪЧзюМбЕФЦїМўЃЌЪЪгУгкЭјТчЯЕЭГЕчдДЁЃЫќВЩгУЙЬЖЈЦЕТЪЁЂСЌајЕМЭЈЗхЕчСїФЃЪНЕФПижЦЃЌОпгаСМКУЕФВЙГЅКЭПьЫйЫВЬЌЯьгІЁЃЫќВњЩњСНИіЖРСЂЕФ180?вьЯрЁЂ30AЪфГіЁЃУПИіЯрОпгаЕЅЖРЕФБеЛЗШэЦєЖЏКЭЙ§диЭЃЛњЖЈЪБЦїЁЃ IntersilЙЋЫОЕФISL6307AПижЦЮЂДІРэЦїаОКЫЕчбЙЕїећ(ЭМ3)ЁЃЮЂДІРэЦїИКдиПЩВњЩњЗЧГЃПьбиТЪЕФИКдиЫВЬЌЁЃISL6307AОпгаПэДјПижЦЛЗКЭИпДя12MHzЕФЮЦВЈЦЕТЪЃЌФмЮЊЫВЬЌЬсЙЉзюМбЯьгІЁЃISL6307AРћгУзЈРћММЪѕИаВтЕчСїЃЌРДВтСПЕЭЖЫMOSFETЕМЭЈЦкМфПчНгдкЕЭЖЫMOSFETЕФRDS(ON)ЛђЪфГіЕчИаЦїdcЕчзш(DCR)ЩЯЕФЕчбЙЁЃЕчСїИаВтЦїЮЊОЋШЗЕчбЙНЕЁЂЭЈЕРЕчСїЦНКтКЭЙ§СїБЃЛЄЬсЙЉЫљашЕФаХКХЁЃПЩБрГЬФкВПЮТЖШВЙГЅЙІФмВЙГЅЕчСїИаВтдЊМўЕФЮТЖШЯЕЪ§ЁЃ  ЭМ3 гЩ4ИіFair child FDMF 8704DrMOSФЃПщКЭ1ИіЗжРыЕФЫФЯрIntersil ISL8307A PWMПижЦЦїзщГЩЕФМђЛЏЫФЯрЕчбЙЮШбЙЦїЕчТЗЁЁ |

ЭјгбЦРТл