负载点降压稳压器及其稳定性检查方法

发布时间:2009-7-19 13:38

发布者:李宽

|

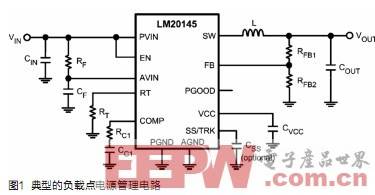

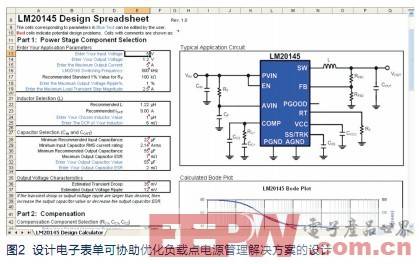

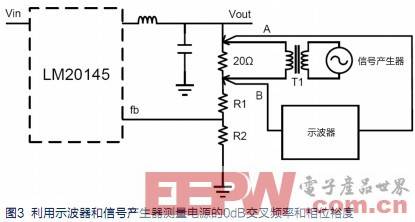

即使拥有简单易用的器件配合,但有时候仍然很难单凭计算去预计控制环路的稳定性。然而,有一个简单的方法可以在无需使用昂贵的网络分析仪下,计算出任何开关电源的0dB交叉频率及相位裕度。下面,我们将解释设立测试电路的方法,以及除了负载瞬态测试外,还有什么方法可更深入了解某设计的控制环路稳定性。 负载点稳压器的特性 一般的负载点电压调节都会把诸如是5V的低输入电压降低至2.5V、1.8V、1.1V或甚至更低的输出电压,而不少要求低输入电压的应用均倾向使用大电流。FPGA及ASIC这两种电路是设有负载点稳压器的典型电源负载的例子,它们均具有特殊的电源管理要求,尤其是高性能的FPGA,一般均要求多个电源轨,例如芯核和输入/输出需要两个电源轨是很常见的情况。可是,有些FPGA需要的电源轨数量更多,其真正的电流要求则视FPGA的实际用途而定。对于某些FPGA来说,其他需要注意的地方包括供电电压的单调启动及各电源轨的上电定序。 基于以上的要求,单靠一个电源管理电路实不足担当FPGA或类似负载的负载点电源。美国国家半导体的LM20000负载点稳压器系列具备各种规格,能够在设计过程中互相替换。假如FPGA的最终代码在开发期间被修改或被要求需要更大的电流时,可以改用LM20000系列中具备更大电流额定的成员,而此期间无需再花时间重新设计,因为系列中所有成员的特性均相互近似。假如一个系统采用多个不同的开关频率,便很容易产生诸如差拍现象等频率问题,而通过将多个负载点稳压器同步化便可解决这一问题。这些稳压器将会起动进入一个具备单调斜波特性的预偏置负载,以防止出现某些FPGA或ASIC的锁存或类似行为。配合软启动及追踪功能,便能够根据个别FPGA或ASIC的类型来紧密控制起动。图1所示为一个典型的大电流负载点电源的例子。由于电源管理电路内同时包含了高边及低边功率晶体管,因此只需选用少量的外置元件及进行简单的优化程序便可。  对于一些不擅长电源管理的设计人员来说,他们确实需要一些支持去优化电源的设计。例如,仿真工具可协助展现电源系统的实际特性,但由于仿真工具一般都不能够直接地提供元件间的折衷建议。由此,比仿真能力更重要的设计支持是要协助设计人员找出最合适的外置元件。LM20000稳压器系列可提供一个 Excel格式的设计指导,可帮助设计人员迅速地挑选出最合适的外置元件并可计算出其可预测的稳定性。图2表示出由美国国家半导体设计网站所提供的免费精简设计电子表单。  通过利用数学电子表单的方法可轻易地找出开关电源的稳定性,尤其当设计人员拥有上述提及的工具时更是如此。可是,设计人员如何确定实际的硬件也拥有足够的稳定性裕度?电子表格反映的只是用户输入变量的结果,但假如探讨的是输出电容器的等效串联电阻(ESR),那么便很难从生产商获得正确的数值,尤其当设计中有多个不同或相同ESR的电容器并联在一起。如此,究竟作用在控制环路的总输出电容器ESR是多少? 毫无疑问,检查电源设计稳定性的最佳方法是在实际环境中进行测量。测量的方法是采用一个普通的信号产生器和示波器去测量调节环路转换函数的0dB交叉频率及0dB交叉频率的相位裕度。图3所示为测量的设置。  将信号产生器的频率设置在电源电路的开关频率以下,而波形应被设置成正弦波,其波幅位置则应被设置于变压器T1后面(即位于A及B点),正弦波的波幅应大约介乎30mV到100mV。接着,将示波品的一个频道连接到A点,而另一个则连接到B点,并将示波器设置成带宽限制模式以防止开关噪声影响敏感的测量结果。最后,将示波器的单位设定到最小幅度,例如是每单位10 mV或20mV。 完成上述设置后便可启动LM20145或其他电源管理电路的电源并观察示波器的屏幕。这时可看到一个正弦波出现在其中一个频道上,而另外一个则可能是一条直线。接着,把信号产生器的频率从几赫兹扫频至电源开关频率的一半,视所采用的变压器T1,正弦波的波幅会稍微地出现变化,这是由于变压器的增益会随频率而改变。因此,当进行扫频时,有必要调节信号产生器的波幅以把注入信号的波幅维持在30mV 至 100mV的范围内。 此外,当扫频信号产生器的频率时,应该可发现在某一个频率下,示波器上的频道A和频道B会同时出现一个波幅一样的正弦波,而在这个频率下,电源控制环路的增益便等于1dB或 0dB。这一个点就得出了电源系统的带宽。在这个频率下,可以看见频道A和频道B之间发生了一个位移。利用示波器作绘图,并将一个时间标记放到其中一条频道的正弦波波峰上,同样也把另一个时间标记放在另一个正弦波的波峰上。如此一来,测量出来的相位差角度便是电源转换器转换函数的相位裕度。 结论 现代的负载点稳压器在建立FPGA和ASIC电源方面提供了很多出色的功能,有赖于这些先进的部件,使得设计人员能够轻松地对基本的电源管理设计作出改动,而无需花时间重新设计整个电路。电子表单在筛选外置元件的过程中发挥了很大的作用,而对于检查实际设计的稳定性,本文也展示了相关的简单测试步骤和低成本的标准测试装备。 |

网友评论