软微控制器开放式架构

发布时间:2010-10-7 21:39

发布者:eetech

|

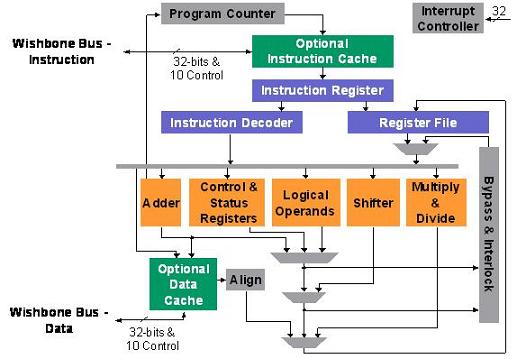

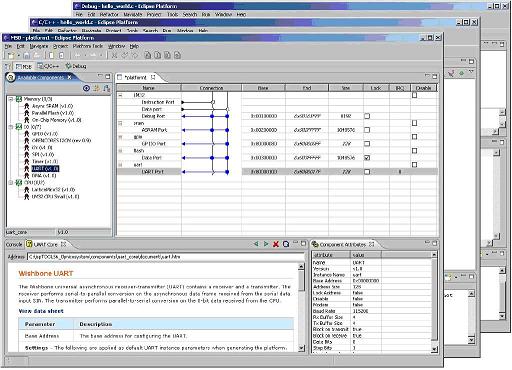

“软”微控制器是一个在FPGA的可编程结构中实现的处理器、存储器和外设的平台。过去,现成的微控制器的价格大大低于软处理器的价格。如今随着90纳米或采用更小工艺的最新低成本现场可编程门阵列(FPGA)的出现,它们的整体成本已具有可比性。设计人员可以对软微控制器进行调整,以便符合目标应用所需的功能和性能。有些通用微控制器附加了一些不必要的功能,与这些通用微控制器相比较,使用软微控制器可能会导致更低的成本。因此,对成本敏感的应用,如那些针对消费产品的设计,现在用软微控制器是一个可行的办法。已经证明,低成本FPGA是一种节省成本的解决方案,因为它们可以取代大量的器件。如果设计中已使用了FPGA ,微控制器可集成到这个FPGA之中,节省了使用分立元件或一个额外FPGA 的成本。 LatticeMico32微控制器 莱迪思的软微控制器的核是LatticeMico32处理器。LatticeMico32是采用哈佛存储器架构的RISC设计。哈佛架构允许执行单周期指令,因为允许同时访问独立的32位指令和数据总线。LatticeMico32有32个通用寄存器,可处理多达32个外部中断。有两个可选方法来改善吞吐量,以避免Wishbone总线访问指令和数据存储器。第一种方法是使用高速缓存(图1 ) 。第二种方法是使用“内联”存储器(图中未显示) 。内联存储器是直接与指令和/或数据流水线相连的存储器,而不是通过WISHBONE 来访问。这两种方法可在一起使用。图1中突出展示了这些特点,并展示了一些其它元件。  图1 LatticeMico32的结构图 为了加快微控制器平台的开发,几个外围元件可与LatticeMico32微处理器一起使用。通过Wishbone总线接口把这些元件连接到处理器,这是一个由OpenCores组织制定的免费开放协议。通过使用这个开放源总线接口,用户可以把自己的WISHBONE元件放入其嵌入式设计。 除了外设可用Wishbone总线之外,还可以构建一个总线互连结构,这样不但能使元件之间能够互相通信,而且还可以进行调整,从而满足了系统的吞吐量需求。 设计流程 LatticeMico32 System软件开发工具提供了一个快速简便的方法来实现微控制器设计。包括从微控制器的定义到软件的开发和调试。该工具基于Eclipse C / C + +开发工具( CDT )环境,这是一个业界标准的开放源代码软件开发架构(图2 )。  图2 易于使用的图形用户界面开发工具 LatticeMico32 System有3个集成工具:

MSB生成微控制器的结构,以及针对硬件实现的相关硬件描述语言(HDL)代码。设计者可以选择外围元件,把它们连接到微处理器,并指定它们之间的连接。其它工具要使用微控制器的结构信息,以便使代码完全针对微控制器。例如,UART可移入微控制器的存储器空间(从而更新微控制器的结构) ,针对这一更新微控制器的软件将通过新的空间来访问UART。MSB还能构建处理器(和其它主元件,如DMA )和从外设之间的互连,从外设用来调整吞吐量的需求。例如,当多个主元件与不同的外设通信时,多个主元件可以共享一个总线来访问所有的外设。或者每个主元件可以直接以非共享的形式访问任何一个外设,该外设只与那个主元件通信。这需要用更多互连的总线,但允许两个主元件同时访问不同的外围设备。最合适的总线互连将取决于该系统的通信模式和吞吐量的需求。

C / C + + SPE是一个集成的软件开发环境。它包括一个制作系统,针对用MSB构建的某一微控制器、调用编译器、汇编器和创建代码的连接器。

C / C + +源代码级调试器提供了软件调试功能,调试可以是源代码级或汇编级,这些代码在软微控制器/ FPGA中运行。支持标准的调试任务,如设置断点、步进,并允许用户观察处理器中的寄存器和存储器的状态。

Reveal硬件调试器是一个片上调试器,它有别于LatticeMico32软件调试器。然而,LatticeMico32调试器能深入观察微控制器的状态(如寄存器,存储器的内容) ,而Reveal则能够深入观察硬件。有了Reveal,用户可以“跟踪”任何一组设计信号。当启动和停止跟踪时,可设定复杂跟踪触发条件来加以控制。调试一个含有软微控制器的系统时,可将Reveal和LatticeMico32调试器一起使用,这样就有了高度的可见性和可用性。 支持Windows和Linux的工具链提供以下几个方面的支持:

操作系统 LatticeMico32支持以下操作系统:

资源利用率和性能 LatticeMico32具有很高的性能并占用最小的资源。对那些关心资源的设计者来说,基本配置不使用指令或数据高速缓存、单周期移位器,也没有乘法器。对于那些更加关心性能的设计人员而言,全面配置使用8K字节指令高速缓存、8K字节的数据高速缓存、3个周期的移位器和乘法器。对需要考虑折衷方案的用户,标准配置类似于全面配置,但没有8K字节的数据高速缓存。 开放源代码方法 在各种软件领域,开放源代码越来越受欢迎了,并已被台式机/服务器软件所接受。采用开放源代码IP的好处包括更多的可见性、更大的灵活性,以及提高可移植性。 开放源代码能够观察微处理器的细节。通过访问源代码,设计人员对这个核的细节会有一个全面的了解。此外,开放源码对这个IP提供了更大的灵活性,并且对每个人都开放,因此设计人员可以对它进行核查,并对此IP作出改进。这种采用开放源代码的方法使整个用户群体帮助查明问题所在,并制定解决方案。这意味着,不仅允许用户修改源代码,还鼓励他们这样做。这种用户群体相互促进导致开放源代码的IP往往比传统的专有IP更加稳健和可靠。最终,开放源码提供了改进的可移植性。用户赞赏独立的架构,因为一个开放源代码的IP核可用于任何FPGA ,甚至可以迁移到一个更高批量,成熟设计的ASIC中。独立的架构是很有价值的,因为它能够确保在最后一分钟对器件做出修改的情况。应该认识到,开放源代码IP最常见的好处是:它是免费的。 |

网友评论