模拟设计与验证工具现状

发布时间:2010-9-26 14:21

发布者:eetech

|

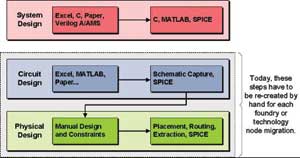

大约从20世纪80年代起,就有许多业内专家宣称模拟电路已走进死胡同,而数字应用将在电子世界中大放异彩,包括用在通信上的集成电路(integrated circuits,ICs)。在现实中,当然,现代化的通信系统同时需要将模拟及数字功能复杂地融合在一起。 不过有一个问题,比起它的数字同胞,在支持自动化能力这方面,模拟设计及验证工具却远远落后。其结果,模拟设计工程师的生产力远不及数字搭档来得强。 就以数字集成电路设计为例,现代最先进的设计环境提供了高阶的自动化,即使是包含上亿个晶体管的最复杂设计,也能在短短几天内重新转给新的代工厂、同一座代工厂但不同的制程、甚至全新的技术节点。 相对地,缺乏自动化支持的传统式模拟设计环境,代表模拟电路的制作及修改几乎全靠人工。这样的结果,即使把相当简单的模拟功能转向新的代工厂、制程或技术节点,也要耗费6~12个月的时间。换言之,虽然尖端的数字设计已经达到32nm的技术节点,绝大多数的模拟设计仍深陷在130nm及250nm节点的泥沼之中,那算是5~10年前的老旧技术了。 首先,本文先提出数字设计及验证技术演进的概观,并说明现代最先进数字设计环境在支持高阶自动化上的生产力优势。本文接着提出模拟设计及验证技术演进的概观,并且拿来跟数字的自动化能力做对比。 最后,本文讨论了模拟工具必须予以强化以支持更高阶自动化的方法;同时也阐述了现代化IC设计环境必须强化的方法,以具备足以支持真正的、统一的、全芯片混合信号设计、验证、及实现的能力。 数字工具的演进 早期的数字IC设计,约20世纪60年代初期,电子电路皆以手工建立。电路图(原理图)都是用纸笔及印刷模板以手绘制。这些图面显示逻辑门与功能的各式符号,并且用来实现符号之间连线的设计。 执行“功能验证”时,通常是一群工程师围坐在桌子旁,通过原理图兢兢业业地讨论:“这部分我看应该没问题!”同样地,进行“时序验证”时,典型的做法也是靠着纸和笔。最后,用来组成晶体管、电阻器及彼此之间互连的架构都是以人工绘制而成的。 毫无疑问,这种手工艺品方式的设计极为耗时,而且很容易出错。这种情形必须要有解决之道,于是有些公司及大学就率先跳出来,采用各种不同的研究方向。就设计获取(design capture)而言,门级(gate-level)的“原理图获取”套件即在市场上开始出现,至于功能及时序验证,在20世纪60~70年代初期所看到的,则是先出现以“事件驱动逻辑仿真器”及“静态时序分析器”为形式的专门程序。 以抽象的门级建立数字设计,就如同使用汇编语言撰写软件程序一般。就执行效率及所需的计算机内存数量而言,汇编语言的程序或许是不错的实施,但它需要很长时间的获取及确认,而且不容易转到另一台计算机上。同样,门级的表示方式也需要很长的时间获取及确认,转移到新的代工厂或制程/技术节点也相当困难。 至于软件方面,开发者的解决方案则以程序语言(如C语言)的形式,提升至另一个更高层次的抽象概念。然后,这些高级表达式可以编译成计算机所需的机器级指令。这些高级表达式的优点是,可容许软件开发者迅速而精准地捕捉到程序的含义,确认其功能。同时,以C语言撰写的程序可以很容易地转移到其他的计算机平台。 同样,对于数字逻辑而言,设计工程师也开始提升至更高阶的抽象概念,称之为“寄存器传输层”(Register Transfer Level,RTL)。在20世纪80~90年代初期登场的“逻辑综合”(logic synthesis)则用来将RTL表示式编译成对应的门级网表(netlist)。这项“前端”综合技术另以“后端”的自动布局布线(place-and-route)引擎补其不足之处,后者可从门级网表,执行设计的物理实现。 循着C语言程序在编译后能用在不同计算机上的足迹,RTL与逻辑综合的组合让数字设计能更轻易地移植到新的代工厂或制程/技术节点。 模拟工具的演进 实际上,模拟电路的计算机辅助设计与验证工具,在早期是优于数字电路的。模拟电子系统设计在刚起步的时候,电子电路完全靠人工绘制。晶体管层的电路图完全用纸笔及印刷模板以手工绘制,再搭配基本的“纸笔”分析及验证。 在设计由离散(独立封装)的元器件例如晶体管、电阻器、电容器及电感组成时,通常是建立设计的实体原型,将它放上测试平台(test bench),测量实际的数值,以判定性能优异,然后参考元器件所得的数值,新增或移除所需的元器件,以达到期望的效果。 很显然,这种方法在开始建立第一片模拟IC时并不可行,因为IC设计的工程变更代价非常昂贵。在20世纪60~70年代初期,有几所大学及商业公司着手开发模拟仿真器。这些程序让学生及工程师得以仿真模拟电路,而无须实际付诸行动制造。早期的几个仿真器中,最有名的大概就是“SPICE”(Simulation Program with Integrated Circuit Emphasis),这套程序是由加州大学柏克莱分校所开发,并在70年代初期广为流传供大家使用。 随着时间的演进,模拟仿真在基本模型及算法的复杂度,以及仿真引擎的能力与表现上,有显著的发展。多数今日所使用的模拟工具都发祥成形于20世纪90年代的初期与中期。和其他不同的是,这些工具的基本结构从未试图支持混合信号设计环境的复杂需求,一如本文稍后章节的讨论。 或许更重要的是,现今的模拟设计及验证工具在实质上仅限于捕捉及模拟晶体管级的单线图。到目前为止,有关自动化的成功案例仍属凤毛麟爪,例如: ● 在高阶抽象概念上描述模拟功能,然后用来生成等效的晶体管级电路。 ● 自动优化模拟电路。 ● 自动布局布线模拟电路。  图1 每道制程/技术节点以人工重新设计需要耗费9~12个月 最终的结局是,模拟集成电路仍旧大多处于全定制,并以人工方式费心费力绘制。除了非常昂贵、耗时、容易出错以外,这类晶体管级的设计型态并不容许现有的设计简简单单地就能转换到新的代工厂或制程/技术节点。相反的是,欲移植这类型的设计需要将电路重头开始,重新实施,耗时9~12个月是常有的事。 这也有助于说明为何最尖端的数字设计目前已迈入32nm的技术节点,但最先进的模拟设计只在90nm节点,而且大部分的模拟设计依然深陷在130nm及250nm节点的泥沼中,那算是5~10年前的老旧技术了。 模拟自动化的要求 此处所说的要求可以简要地说明之;如何实际达成可说非常地复杂。最低限度,强化后的模拟设计工具必须能提供与数字设计相类似的自动化及生产力能力。这些自动化能力应包括但不限于以下: ● 在高阶抽象概念下确认模拟功能的能力,然后自动将表示式编译成等价的晶体管层级。 ● 自动执行模拟精细改进及优化的能力。 ● 自动在IC上布局模拟零组件的能力。 ● 自动在IC上布线模拟零组件的能力。 ● 从某制程/技术节点自动移植模拟设计制程至另一个,以及从某代工厂移植至另一家的能力。 从某方面来说,需考虑的最后一点就是所有其他点的叠合。老实说,需耗费6~12个月才能将模拟设计转移到新的技术节点早已令人无法接受。若能透过自动化将此过程降低到仅需数天的时间,模拟功能即可享受到功耗及最新技术节点性能特征的完全优势。 混合信号的考虑 直到最近,大部分的集成电路在性质上若不是纯数字,就是纯模拟。因此,很自然地,任何用来设计或验证这些器件所使用的计算机辅助设计工具,都是只为数字或只为模拟的领域单独设计的。  图2 模拟/全定制的生产力依靠集成化和自动化的提高可以显著地增加 初期的通信系统是由一大堆相当简单的模拟及数字IC所组成。随着时间的历程,为了满足多样化的要求,例如尺寸、成本、功率、性能及可靠度,越来越多的功能结合在越来越少的芯片上。开始只是将多种模拟功能合并在特定的模拟芯片上,将多种数字功能合并在数字芯片上。直到最近,终于将模拟及数字功能结合在单一的混合信号装置上。 经过这些年的发展,虽然传统的模拟与数字设计及验证工具,在容量及性能上已有长足地进步,但其最基本的底层架构大部分仍是以20世纪90年代中期的技术为基础,而这些工具依旧专注在模拟或数字的领域。举一个简单的例子,模拟与数字的工具及流程使用不同的数据库,因此这两个领域之间的交互非常困难。其结果是数字及模拟的设计团队向来都是井水不犯河水,甚少关注对方倒底是在研究什么。 即使是现代“最先进”的混合信号及全定制设计环境,数字与模拟团队大多还是各自独立作业,甚少涉足到对方的领域中。在芯片最后整合(chip finishing)的阶段,也就是将模拟模块和数字模块摆放在一起并走线的时候,两个团队才首次见面并互相介绍认识,这种情况并不罕见。 芯片最后整合通常是以人工的方式执行,其中发生在芯片投片之前的就有许多工作。由于缺少自动化,芯片最后整合活动及动作常常不能反馈回原来的模块设计,这有可能导致成为下一代芯片在设计重用上产生问题。 总结 最近几年,市场上的需求着眼在通信系统日益增加的性能上,而且带宽正以倍数的速度成长,然而许多产业观察家相信,目前所看到的只不过是“冰山一角”。为了满足目前及未来的需求,进入21世纪,模拟设计与验证工具必须在本文前述的自动化能力上努力奋进。然而,靠着孤立的方式强化模拟工具是不够的;真正的要求将是一个真实、统一、全芯片的混合信号设计,以及验证的环境。首先,所有的模拟与数字设计,以及验证引擎应使用统一的数据库。其次,环境必须提供最大的容量及性能,例如将整个全芯片的数据在一分钟之内加载,并在短短数秒之内重新绘制所有的模拟及数字层。第三,环境必须支持极为精确的寄生参数提取及全芯片混合信号仿真与分析。第四,在芯片最后整合阶段,环境必须支持自动全域布线。 通信业正在迅速接近这样一个危机,就是需要快速设计和制造大型复杂的混合信号器件方面的能力。当今最先进集成电路的设计师需要所有这些能力,他们现在就需要! |

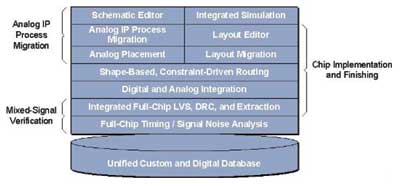

网友评论