不同电源供电的器件间的桥接

发布时间:2010-9-25 11:10

发布者:eetech

|

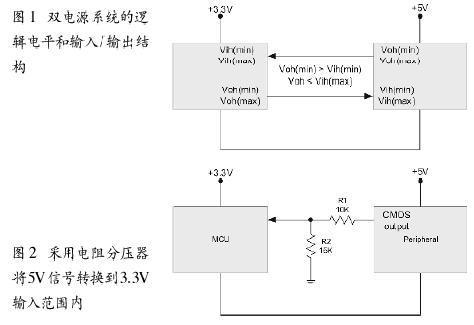

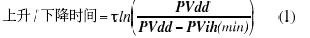

半导体行业从一开始就以“更小、更快、更便宜、更好”为宗旨。当前的掌上电脑(Pocket PC)比占地整整一幢楼的第一台电脑功能更强大。然而,到目前为止,实现这一目标的方法都是减小组成半导体器件的单个晶体管的体积。这也带来了有趣的副作用。随着晶体管变得越来越小,工作电压也越来越低。在过去的嵌入式系统中应用最普遍的就是5V电源。但典型嵌入式系统中的大多数元器件也转而采用更低的电源电压,以充分利用行业最新趋势带来的好处。另一方面,系统中的某些元器件需要更长的时间才能完成转变。因此,在转变过程中,系统中的某些元器件可能需要不同的供电电压(如,在3.3V系统中存在5V器件,反之亦然)。这给嵌入式设计人员带来了一些设计方面的挑战。一种解决方案是采用逻辑电平转换器,但采用电平转换器并非成本效益最高的解决方案。本文将讨论3.3V单片机(MCU)与5V外设接口的一些低成本设计思路。 如果要将5V设计转为3.3V,第一件事就是寻求电源为3.3V但其他性能相同的单片机。大多数情况下,都能找到支持3.3V电压的同等器件。而且,基本上,3.3V器件的成本与之持平,甚至更低。如果找不到可运行在3.3V条件下的替代器件,那么就必须采用双电源了。本文的重点就是讨论采用双电源供电的设计。 对于5V和3V器件共存的设计,首先必须理解逻辑电平和输入/输出结构。对于输入,需要考虑VIH(保证被检测为高输入的电压)和VIL(保证被检测为低输入的电压)。将3.3V系统连接到5V器件时,VIH 通常会比VIL带来更大的问题。当然,这并不是说可以忽略VIL 参数。驱动器件必须输出高于接收器件VIH(min)值的电压才能保证正确的逻辑检测。但是,如果电压太高也不好。 几乎所有CMOS器件在所有I/O引脚都采用了某种形式的ESD保护。实现ESD保护最常见的方法是采用箝位二极管将这些引脚连接到Vdd 和 Vss。这通常意味着最大输入电压为Vdd +0.3V,最小输入电压为Vss - 0.3V。如果电压超出这一范围,保护二极管就会导通。如果输入端没有串联电阻,就会导致这些二极管通过极大电流,并有可能造成器件锁死。这肯定不是所希望发生的。如果电压足够高(如3.3V系统中的5V输入),那么串联电阻必须非常大才能保证箝位电流处于安全范围内。如果电阻足够大,那么由于引脚电容和PCB布线而引起的低输入容抗可能就会变得重要起来。RC时间常数会导致信号延迟。许多生产商都建议不要使用箝位二极管实现ESD保护。因此,采用串联电阻并非将5V信号馈送到3.3V器件的最好方法。 让我们看一下标准CMOS器件的逻辑电平,大多数器件的VIH (min)都是0.7 Vdd或 0.8 Vdd。而 VIL(max) 大致在0.2 Vdd或0.3 Vdd。对于5V逻辑,对应的VIH 为 3.5V或4.0V,VIL(max) 为1.0V或1.5V。在低负载时,大多数CMOS器件的输出都接近于电源电压(0.1 或 0.2V)。随着负载电流增加,VOH 会变低。此时,确定VOH必须要考虑负载电流。  与串联输入电阻相比,更好的方法是采用电阻分压器将5V信号转换到3.3V输入范围内(见图2)。电阻值的选择必须考虑到所有公差。计算时可参考下面的公式: R2/(R1 + R2)×VOH (min)>VIH(min) (输入电压为标称值5 V与最大负公差之和) R2/(R1 + R2)×VOH (max) 在上述计算过程中还应当考虑到电阻值本身的公差。 另一种更简单的解决方案是采用兼容TTL输入的5V器件。TTL器件的VIH(min)是2.1V(Vdd为5V时)。在大负载值条件下,大多数3.3V器件可以支持更高的VOH电平。此时,解决方案是将外设器件更换为兼容TTL输入的同等器件。 应该很容易就可以发现带有TTL输入的类似器件。表1给出了一些例子。  如果正在使用必须采用5V供电的标准数字逻辑系列器件,那么可以寻找支持TTL输入的同等器件。(如,可使用74HCT 系列代替74HC 系列。)如果需要使用电平转换器,那么可使用“HCT”或“VHCT”型的数字缓冲器。在大多数情况下,这一TTL输入解决方案都比采用专用电平转换器便宜。  3.3V器件的VOH 电平一般比5V CMOS器件的VIH(0.7Vdd = 3.5V)稍低。一种简单的解决方案是使用二极管来实现电压转换。 上面的电路将输出电压增大了约0.6V。从而正好将3.3V CMOS输出电压转换到了5V CMOS输入范围内。对于逻辑低电压信号也进行了同样大小的转换。但,CMOS输入的 VIL (max)约为1.5V,因此电压转换后的信号仍然满足 VIL 参数的要求。对于这一配置,需要考虑几件事。当3.3V器件输出0逻辑电平时,电路的汲取电流也将增加。因此应当仔细研究一下3.3V器件VOL 规范对电路灌电流的限制。通常,灌电流越大,VIL就越高。因此需要小心不要违反VIL参数要求。如果CMOS 输出VOL过高,则必须考虑加大上拉电阻值。如果电阻太大,二极管偏置电流会变低,从而导致二极管的开关速率降低。 Microchip新推出的16位PIC24系列单片机提供了可简化5V接口的独特功能。该系列单片机的输入引脚可承受 5V(或 5.5V)电压,即使器件正常情况下运行在3.3V或更低的Vdd电压下。这些输入引脚不需要连接到Vdd的箝位二极管,而是采用了不同的ESD保护机制。对于5V接口来说,这是非常重要的特性,因为这样不需要电阻分压器就可以直接将5V输出连接到3.3V器件。让我们回到图3的例子,可见添加了这一功能即可实现无缝的5V接口。 有些单片机产品还进一步增强了这一功能,提供了通过外部5V上拉电阻产生5V输出的能力。3.3V器件驱动3.3V输出,但能承受5V的输入。这些引脚提供数字控制的漏极开路输出,使您可以选择将引脚上拉到5V,而不会违反任何规范。这一功能支持通过CMOS输入与5V器件方便地接口。  当采用上拉电阻配置(见图6)时,需要考虑两个器件间的连接电容,从而确定端口引脚处信号的上升/下降速率(和最大开关频率),以及适用的电阻值。考虑下面的公式:  其中 τ = RC 时间常数,R×C PVdd = 外设电压Vdd PVih(min) = 外设的 Vih(min) 值 如果使用下述典型值: 上拉电阻 R = 1K 电容 C(由于引脚和PCB电容) = 10pF PVdd = 5V PVih(min) = 0.7×Vdd = 3.5V 则上升/下降时间≈12nS 如果可接受的最小上升/下降脉冲的时间宽度50nS,那么最大的输出频率为20MHz。对于大多数外设互连来说,这已经足够了。 这种方法有一个缺点就是当MCU驱动逻辑低电平时,会通过上拉电阻消耗额外的电流。因此设计时需要考虑速度和电流大小两个因素折衷选择上拉电阻。需要为您的应用选择一个折衷的电阻值来提供所需的速度并且确保消耗的电流不超出规范。 有些人可能认为不能采用这类配置来驱动低阻抗负载。如果希望驱动一个5V的继电器,那么应当怎么做?幸运的是,对于驱动继电器这样的低阻抗负载,上述特性也有帮助。从图7了解电路配置信息。要驱动此类负载,需要将引脚定义为输出并驱动为低电平。这里,唯一的限制因素是器件的灌电流能力。要关断负载,将引脚定义为输入就可以了。关断负载会将5V电压直接馈入输入引脚。由于引脚可以承受5V电压,因此这一操作是正确的。换句话说,需要保持输出锁存器为逻辑低,并通过切换TRIS(输入/输出控制寄存器)来使负载接通/关断。 本文介绍了桥接由5V和3.3V供电的电路的有效方法。这些方法完全可以和转换阶段桥接由不同电压供电的电路的低成本智能解决方案媲美。同时,大多数器件很可能会很快转向使用更低的电源,从而不再需要进行电路桥接。本文给出的方法对于充分利用半导体行业的最新发展趋势以及降低系统成本肯定会有所帮助。 |

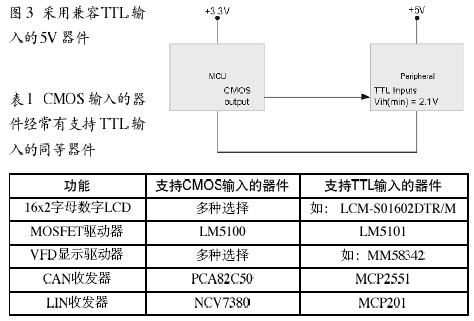

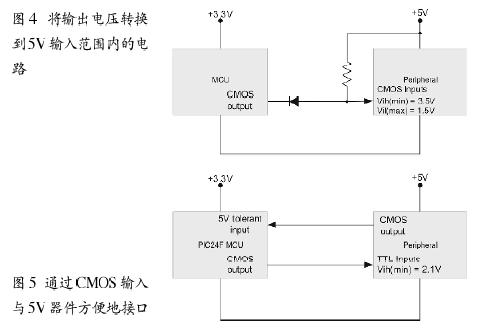

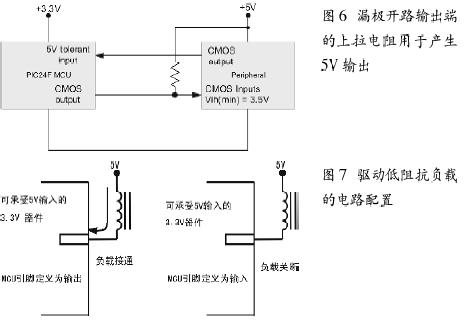

网友评论