无绝缘移频自动闭塞系统中采集系统设计

发布时间:2010-8-20 14:30

发布者:lavida

|

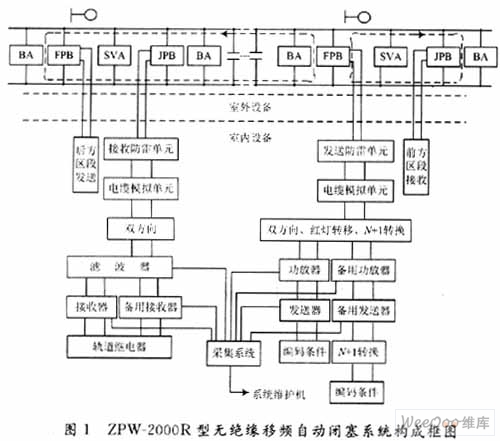

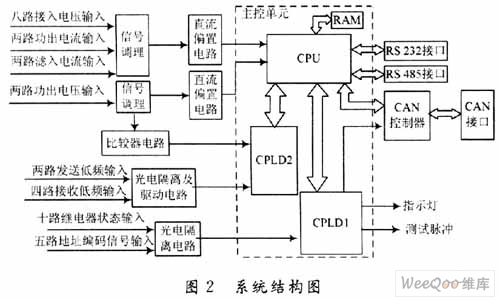

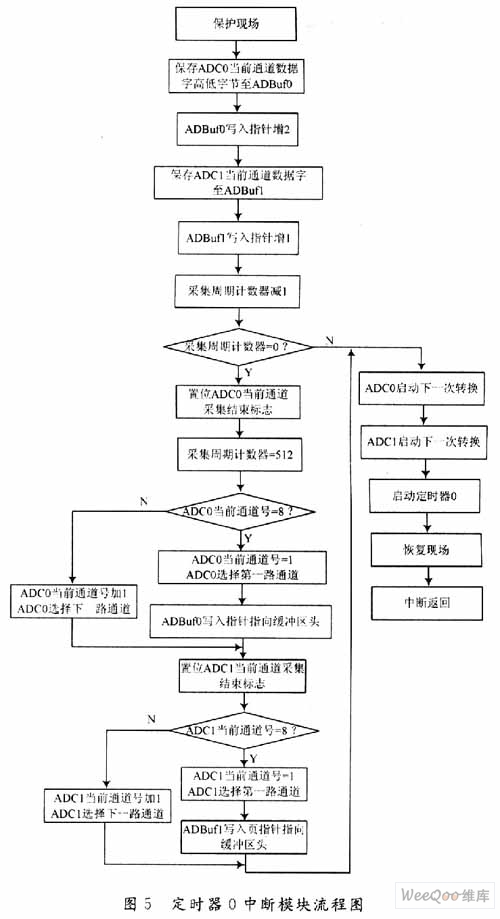

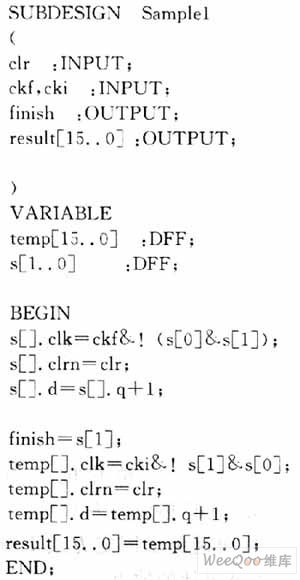

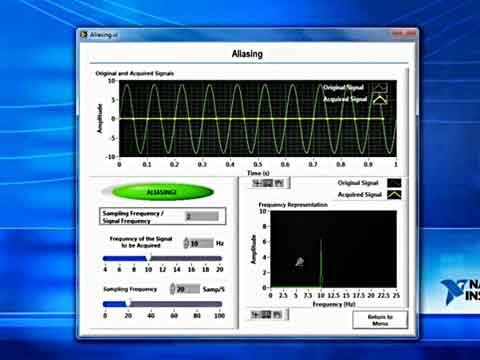

随着我国铁路向高速、高密、重载、电气化方向迈进,区间闭塞设备尤其是移频自动闭塞系统得到了迅速的发展,ZPW-2000R型无绝缘移频自动闭塞系统也因此得到了广泛的推广应用。为保证ZPW-2000R型无绝缘移频自动闭塞系统能可靠安全的运行,随移频自动闭塞系统配套,提供了系统维护机,以对系统的运行状态进行全天候监视,方便维护人员及时发现故障,并尽快排除故障,保证安全。本文介绍的采集系统正是为监测ZPW-2000R型无绝缘移频自动闭塞系统维护机的主要设备提供接口。 1 ZPW-2000R型无绝缘移频自动闭塞系统简介 ZPW-2000R型无绝缘移频自动闭塞系统分室内设备和室外设备两部分。室内设备包括发送器、功放器、接收器、滤波器、电缆模拟单元、采集系统、防雷单元、系统维护机;室外设备包括匹配单元(PB)、调谐单元(BA)、平衡线圈(SVA)、补偿电容等。系统构成框图见图1,其主要工作方式为:  发送器根据前方闭塞分区执行继电器构成的编码条件,输出相应编码移频信号。先经“N+1”转换、方向电路、红灯转换条件及发送通道设备送至室外电缆,再经轨道匹配单元发送到轨道,并分别向两个方向传输。正向信号经主轨道传送到本区段调谐区的接收侧,并在调谐区发送侧BA处以其对接收信号呈低阻而实现隔离,不再向下一个区段继续传输;反向信号经调谐区传输送至相邻区段的接收侧,同时以调谐区接收侧BA对发送信号呈低阻而实现隔离,不再向相邻区段继续传输。 经主轨道传输的本区段信号和经调谐区传输的邻区段反向信号都送入本区段的接收匹配单元端,再经电缆和通道设备传输,将两种信号送至接收滤波端,由滤波器两路混合分离,分出主轨道信号和调谐区信号这两路输出,分别送至接收器解调、译码,并输出动作执行继电器,控制区间信号灯显示,反映列车占用情况,同时控制后方闭塞分区发送的信息,实现自动控制。 系统轨道电路采用调频方式。载频频率为:1 698.7Hz(1700—1),1 701.4 Hz(1700—1),1 998.7 Hz(2000—2),2 001.4 Hz(2000—1),2 298.7 Hz(2 300—2),2 301.4 Hz(1700—1),2 598.7 Hz(2600—2),2 601.4 Hz(2600—1);频偏为±11 Hz;低频调制频率为10.3 Hz,11.4 Hz,12.5 Hz,13.6 Hz.14.7 Hz,15.8 Hz,16.9 Hz,18 Hz,19.1 Hz。20.2 Hz,21.3 Hz,22.4 Hz,23.5 Hz,24.6 Hz,25.7 Hz,26.8 Hz,27.9 Hz,29 Hz,共18个信息。发送器、功放器、接收器、滤波器的工作状态由采集系统实时采集.并上传至系统维护机。 2 系统架构设计 该系统由输入信号处理、主控单元、外部通信接口三大模块组成,系统结构如图2所示。  主要采集ZPW-2000R型无绝缘移频自动闭塞系统的接收器、发送器、功放器等单元设备的电压、电流、低频、载频及继电器状态等数据,并与系统维护机等上位机进行数据通信。如图2所示,采集的模拟量数据包括两路功出电压、八路接入电压、两路功出电流、两路滤入电流等;采集的频率信息包括两路载频信息、六路低频信息等。其中,接入电压及功出电流输入均为毫伏级交流信号;功出电压输入为高压交流信号;发送低频及接收低频输入为交流数字信号;地址编码输入为电平信号;继电器状态输入为数字脉冲信号。 3 C805lF020简介 C8051F020(F020)是美国德州Cygnal公司推出的完全集成混合信号系统级MCU芯片。具有64个数字I/O引脚。其主要特征为: (1)高速、流水线结构的8051兼容的CIP-51内核; (2)全速、非侵入式的在系统调试接口(片内); (3)真正12位100 kS/s的8通道ADC,带PGA和模拟多路开关; (4)真正8位500 kS/sADC,带PGA和8通道模拟多路开关; (5)两个12位DAC,具有可编程数据更新方式; (6)64 KB可在系统编程的FLASH存储器; (7)4 352(4 096+256)B的片内RAM; (8)可寻址64 KB地址空间的外部数据存储器接口; (9)硬件实现的SPI,SMBus/I2C和两个UART串行接口; (10)通用的16位定时器; (11)具有五个捕捉/比较模块的可编程计数器/定时器阵列; (12)片内看门狗定时器、VDD监视器和温度传感器。 C8051F020单片机的所有模拟和数字外设均可由用户固件使能/禁止和配置。FLASH存储器还具有在系统重新编程能力,可用于非易失性数据存储,并允许现场更新805l固件。片内JTAG调试电路允许使用安装在最终应用系统上的产品MCU进行非侵入式(不占用片内资源)、全速的在系统调试。该调试系统支持观察和修改存储器和寄存器,支持断点、观察点、单步及运行和停机命令。在使用JTAG调试时,所有的模拟和数字外设都可全功能运行。 采用开关网络以硬件方式实现I/O端口的灵活配置,外设电路单元通过相应的配置寄存器控制交叉开关配置到所选择的端口上,从而避免了固定方式I/O端口既占用引脚多,配置又不够灵活的缺点。 4 EPM3256ATCl44-10简介 EPM3256ATCl44-10是Altera公司MAX3000系列的CPLD芯片,其特点:是以多阵列矩阵(MAX)结构为基础的高性能、低功耗的CMOS E2PROM器件,通过内置的JTAG(IEEE 1149.1)可实现在系统编程;内置符合IEEE 1149.1-1990标准的JTAG BST电路;是一款高密度器件,能提供5 000个可用门,256个宏单元,16个逻辑阵列块,116个用户I/O;引脚到引脚的逻辑延迟为5.5 ns,计数器工作频率达172.4 MHz;多电压I/O接口,使得核心工作在3.3 V时,I/0管脚可同时兼容5.0 V,3.3 V及2.5 V三种逻辑电平;遵守PCI规定,具有一10速度等级。 5 硬件设计原理 5.1 电源设计 该系统外部输入电源为DC 48 V。DC 48 V电源经开关、防止接反二极管、滤波电容、熔断电阻至电源滤波器,经滤波器滤波后送到两个电源块(48 V输入,5 V输出)。一个为输入接口电路及通信接口电路供电,另一个经三端稳压片(5 V输入,3.3 V输出)为内部执行电路及指示灯电路提供5 V及3.3 V电源。由于外围接口电路采用单独电源,与内部电路分开供电,实现了内部电路与接口电路的电源隔离,有效保护内部电路器件,提高了可靠性。 5.2 输入信号处理 低频、继电器状态及地址编码等信号经光耦隔离后变为3.3 V方波或电平信号,送入主控单元。输入模拟信号经变压器隔离或升降压、滤波、降压电阻、瞬时过电压保护等信号调理后,输出信号为交变信号,而本系统中单片机内置ADC转换输入电压范围为0~3.3 V,因此在送入ADC之前,还需进行电平抬升,变为满足ADC输入电压测量范围要求的信号。其中,功出电压信号经信号调理后还送至比较器电路,经过波形变换后由原来的正弦移频信号变为3.3 V的方波信号,作为载频信号的输入源。比较器电路如图3所示。电路由分压电阻(R56,R59)、直流分压电阻(R61,R62)、箝位二极管(V7,8V)、比较器N25A(LM393P)、上拉电阻R63及滤波电容等组成。  5.3 主控单元 主控单元包括CPU及两片CPLD。 CPU采用C8051F020单片机。由于F020内部集成有两个ADC,所以在该系统中利用它的第18~25脚及29~34脚共14个端口作为多路模拟信号的输入端口,由单片机完成所有模拟量的A/D转换。在采集各路模拟信号的同时,F020还要从两片CPLD读取频率、地址编码及继电器状态数据,并对所有采样数据进行实时计算处理,将所有转换结果存入32 KB的外部存储器。对于地址编码信息,CPU只在每次上电后读取1次,若有效,则保存,用作与微机监测通信的CAN节点地址,之后不再检查地址编码信息的变化。由F020的交叉开关优先权表可知,两个UART的TX和RX可连到端口引脚。P0.O~P0.3,该系统中利用一组TX0和RX0接RS 232接口,另一组TXl和RXl接RS 485接口。 两片CPLD均采用Altera公司的EPM3256ATCl44-lO芯片,数据采集及指示灯控制所需的控制时序及地址译码等电路均由CPLD产生。其中,CPLDl对48 MHz高精度一体化晶体振荡器分频,得到24 MHz及12 MHz同步时钟信号,分别作为单片机及CAN控制器的系统时钟。由于要采集的开关量路数较多,该系统将所有继电器状态输入及五路地址编码输入均接至CPLDl,再由单片机通过数据总线从CPLDl分别进行读取。CPLDl同时还生成两路不同频率的低频测试脉冲,供生产调试时使用。CPLD2则负责完成所有低频、载频信息的采集。 5.4 与计算机通信接口 该系统提供RS 232或RS 485串行通信接口及CAN通信接口,其中串行通信接口主要用于生产调试,而现场应用中使用CAN总线与系统维护机交换数据。由于一条CAN总线上需挂接多个设备,该系统运用外部端子封线的方式为每个设备定义节点地址,地址编码范围为0~31。当节点地址为O时,CPU将工作于测试状态,运行测试程序代码,供设备调试时使用。  6 软件设计 6.1 单片机程序设计 单片机程序固化在C38051F020单片机的内部FLASH存储器中,在Cygnal IDE集成开发环境下,采用模块化程序的设计方法,将软件分为一个主程序和若干个子程序模块,主程序流程见图4。系统采用定时器O中断方式,每0.1 ms分别对两个ADC的某一通道采集一次,每通道连续采集512次,并将采集到的数据分别存入外部存储器内的两个连续缓冲区ADBufO和ADBufl中,再利用采集到的512个点的电压瞬时值计算交流模拟输入的电压有效值。定时器0中断模块流程见图5。  6.2 CPLD程序设计 CPLD程序是在MaxPlusⅡ开发环境下采用AHDL硬件描述语言和图形混合编写,限于篇幅,这里只给出其中一路低频采集的AHDL代码。  7 结语 该系统采用单片机内部集成ADC实现交流模拟量采集,同时利用C2PLD强大的数字处理功能和高密度集成的特点,降低了硬件成本,简化了电路设计,配合软件编程的灵活性和可扩充性,在实际生产和现场运用中带来了很好的经济和社会效益。在对测量精度要求不高的其他应用中,也不失为较好的选择。 |

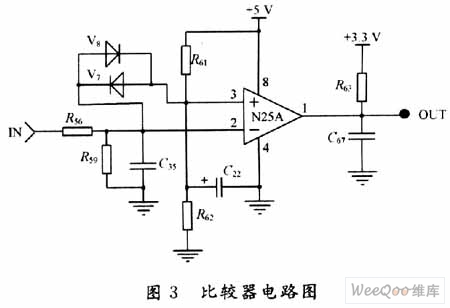

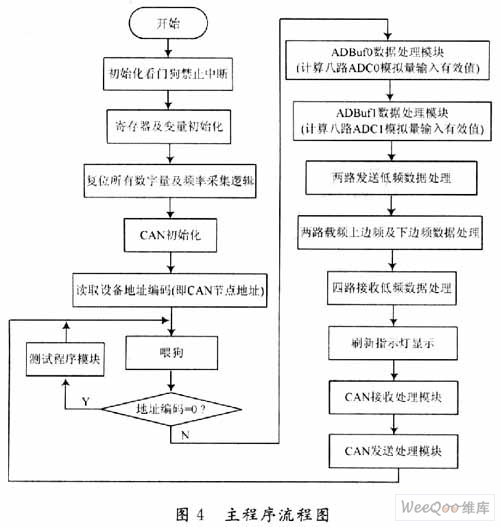

网友评论