ИДдгЕчТЗЯЕЭГЕчдДМАPDSЩшМЦ

ЗЂВМЪБМфЃК2010-8-20 14:30

ЗЂВМепЃКlavida

|

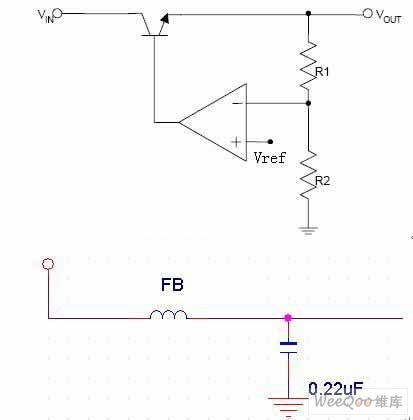

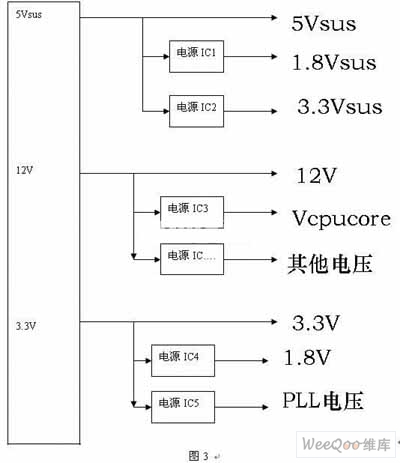

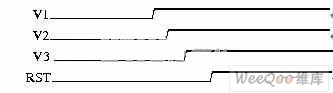

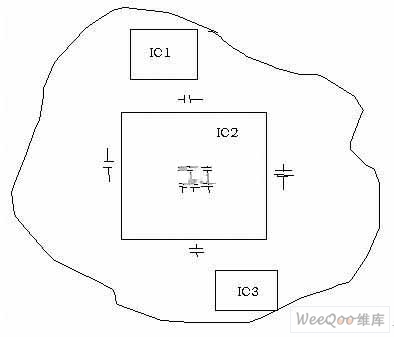

ЯжДњДѓаЭМЏГЩЕчТЗЃЌБШШчCPUЁЂДѓаЭFPGAЕШЯћКФЕФЕчСїЭљЭљДяЕНЪ§АВЕНМИЪЎAЃЌВЂЧввЛаЉИДдгЯЕЭГЕчдДжжРрЗБЖрЃЌвђДЫЕчдДЯЕЭГЕФЩшМЦЪЧЗёКЯРэЭљЭљГЩЮЊЯЕЭГФмЗёЮШЖЈЙЄзїЕФЙиМќЁЃЕчдДЯЕЭГЕФЩшМЦгІИУАќКЌЕчдДЦРЙРЁЂЕчдДЙЉЕчЕчТЗЩшМЦКЭЙІТЪЗжВМЯЕЭГЃЈPower distribution system МђГЦPDSЃЉШ§ИіЗНУцЁЃБОЮФЗжБ№ЬНЬжетШ§ИіЗНУцЕФвЛАуЩшМЦЗНЗЈКЭЫМТЗЁЃ вЛЁЂЕчдДЦРЙР ЦРЙРЕчдДЪЧЕчдДЯЕЭГЩшМЦЕФЕквЛВНЃЌвВЪЧзюживЊЕФвЛВНЃЌОіЖЈСЫЕчдДЩшМЦЕФГЩАмЁЃдкЩшМЦЕчдДЕФЪБКђгІИУвбОЭъГЩСЫећИіЯЕЭГЕФПђЭМЩшМЦВЂЛљБОбЁЖЈСЫЦфжаживЊЕФICаОЦЌЃЌетЪБЮвУЧашвЊВЮПМЪ§ОнЪжВсDatasheetЛёЕУУПвЛИіICЕФЙЄзїЕчбЙМАЯћКФЕчСїЃЌВЂЛцжЦЯТУцетбљвЛеХБэЃК БэвЛЁЂ ICЕчдДЦРЙРБэ  1. ЕчдДРраЭ ЕчдДРраЭПЩвдЗжЮЊФЃФтКЭЪ§зжСНДѓРрЃЌФЃФтЕчдДЪЧжИЮЊPLLЁЂADC/DACЕШФЃФтЕчТЗЙЉЕчЕФЕчдДЃЛЖјЪ§зжЕчдДжївЊЪЧЮЊЪ§зжЕчТЗЙЉЕчЃЌЫќгжПЩвдЗжЮЊКЫаФЕчдДЃЈжївЊЮЊМЏГЩЕчТЗЕФКЫаФТпМЕчТЗЙЉЕчЃЌБШШчFPGA КЫаФЕчЁЂбЙдДЃЉКЭI/OЕчдДЃЈжївЊЮЊI/OНгПкЙЉЕчЃЉЃЌЯжДњДѓаЭICЕФЙЉЕчвЛАуКЫаФЕчбЙКЭI/OЕчдДЪЧЗжПЊЙЉЕчЁЃ 2. ЕчбЙжЕ ЕчбЙжЕвЛАуАќКЌзюаЁЁЂЕфаЭКЭзюДѓжЕЃЌвЛАуЩшМЦЕФЕчТЗЕчдДгІИУЙЄзїдкЕфаЭЙЄзїЕчбЙЩЯЃЌВЂЧвЕчдДВЈЖЏЗЖЮЇВЛгІИУГЌЙ§зюаЁКЭзюДѓжЕЕФЗЖЮЇЁЃ 3. ЕчСї дкЩшМЦЕчдДЪБЕчСїжЕгІИУПМТЧзюWorstЕФЧщПіЃЌБШШчДѓаЭFPGAЯЕЭГЕчСїПЩФмЛсЫцзХЪЙгУТпМУХЕФЖрЩйЖјЯрВюКмЖрЃЛдкЩшМЦЙЉЕчЕчТЗЪБдкЦРЙРЕФзюДѓЕчСїЛљДЁЩЯвЊЬсЙЉвЛЖЈЕФЩшМЦгрСПЁЃ 4. ЙІКФ ЭГМЦУПИіЕчдДЕФЙІКФЪЧЮЊСЫИќКЯРэЕФЗжВМЕчдДTreeЃЌВЮПМЕчдДЪївЛНкЁЃ дкЛёШЁУПИіICЕФЕчдДВЮЪ§КѓЃЌЮвУЧашвЊЛцжЦЯТУцетбљвЛеХЭГМЦБэЃЌетвЛВНЪЧЮЊСЫЕчдДЕчТЗЕФЩшМЦКЭЙцЛЎЕчдДTreeзізМБИЁЃ ЖўЁЂЕчдДЕчТЗЩшМЦ 1. ФЃФтЕчдД ФЃФтЕчдДЭљЭљЮЊPLLЁЂADC/DACЁЂЕчСїдДЕШЕШФЃФтЕчТЗЙЉЕчЃЌЫќУЧЕФЬиЕуЪЧЕчСїНЯаЁЃЌвЛАудкМИЪЎmAЕНМИАйmAжЎМфЃЌВЂЧвЖдЕчдДЮЦВЈУєИаЁЃвђДЫФЃФтЕчдДЕчТЗЕФЩшМЦЭљЭљбЁдёLDOЕШЃЌЮвУЧГЦЮЊЯпадЕчдДЃЛВЂЧвЖдЕчдДдкICв§НХЪфШыДІвЊВЩШЁLCЛђЬњбѕЬхНјааТЫВЈвдНјвЛВНМѕаЁЕчдДЮЦВЈЁЃЦфЕфаЭдРэШчЭМ1ЫљЪОЃК  ЭМ1 2. Ъ§зжЕчдД Ъ§зжЕчдДвЛАуЮЊТпМЕчТЗЙЉЕчЃЌЫќУЧвЊЧѓЭљЭљЕчбЙНЯаЁЃЌЕЋЪЧЕчСїКмДѓЁЃБШШчЯжДњX86 CPUЕФКЫаФЕчдДвЛАудк1VзѓгвЃЌЕЋЪЧЙЉЕчЕчСїПЩвдДяЕНМИЪЎАВЁЃВЂЧвгЩгкCPUФкВПЕФЪЁЕчзДЬЌЕФЧаЛЛЃЌЕчСїЕФБфЛЏвВКмДѓЃЈзюЪЁЕчКЭШЋЫйзДЬЌЙЄзїЕчСїПЩФмЯрВюМИЪЎБЖЃЉЁЃ етРрЕчдДЕФЩшМЦвЛАубЁгУЪ§зжЕїжЦЕФПЊЙиЕчдДЃЌетРрЕчдДвЛАугЩвЛИіPWMПижЦЦїКЭЭтВПЪфГіMOSЙмЁЂBOOTЕчТЗЁЂЗДРЁЭјТчЁЂLCТЫВЈЕчТЗзщГЩЃЛСэЭтвВгааЉПЩвдЬсЙЉНЯДѓЕчСїЕФLDOЕчдДПЩвдбЁгУЁЃЖдгкГЌДѓЕчСїЙЉЕчЪБЛЙашвЊПМТЧЪЙгУЖрЯюЙЉЕчЁЃЯТЭМЪЧвЛИіЕЅЯрPWMЙЉЕчЕчТЗЕФдРэЭМЃК  ЭМ2 3. ЕчдДTreeЕФЛцжЦ дкбЁдёКУЕчдДЕФЙЉЕчаОЦЌКѓПЩвдПЊЪМЕчдДTreeЕФЛцжЦЃЌЮвУЧвдЕфаЭЕФжїАхЙЉЕчЕчТЗЮЊР§НщЩмЁЃЪзЯШжїАхВЩгУЕФЭтВПЙЉЕчЕчдДРДздвЛИі350WЕчдДЃЌЫќЗжЮЊ12VЁЂ5VЁЂ5VsusКЭ3.3VЪфШыЃЌЖјжїАхЩЯЪЙгУЕФЕчдДга12VЁЂ5VЃЈД§ЛњЕчбЙ5VsusЃЉЁЂ3.3VЃЈД§ЛњЕчбЙ3.3VsusЃЉЁЂCPUКЫаФЕчбЙVcore_cpuЁЂCPUЕФPLLФЃФтЕчдДЁЂЧАЖЫзмЯпЕчдДЁЂФкДц1.8VЕчдДЃЈД§ЛњЕчбЙ1.8VsusЃЉЕШЕШЁЃЦфЪЕвЛИіжїАхЩЯЛЙгаИќЖрЦфЫћЕФЕчдДЃЌБШШчаОЦЌзщЕчдДЕШЕШЁЃЮвУЧашвЊКЯРэЕФЗжХфУПТЗЕчдДЃЌБЃжЄУПЬѕЕчдДТЗОЖФЉЖЫЕФзмЙІТЪВЛвЊГЌЙ§ЧАЖЫЕчдДЕФЙЉЕчФмСІЁЃзюжеЮвУЧгІИУЛцжЦГівЛЗљРрЫЦШчЭМ3ЫљЪОЕФЕчдДTreeЃЈНіЮЊЪОвтЭМЃЉЃК  ЭМ3 ЕБШЛЃЌЖдгквЛИіМђЕЅЕФЯЕЭГЩшМЦЦ№ЕчдДПЩФмУЛгаетУДИДдгЁЃ 4. ЕчдДЩЯЕчЪБађ ЖдгкНЯЮЊИДдгЕФЯЕЭГЃЌдкЛцжЦЭъЕчдДTreeЕФЛљДЁЩЯЮвУЧгІИУИљОнЕчдДЕФЩЯЕчЫГађКЭЯЕЭГИДЮЛЕШаХКХЕФвЊЧѓЛцжЦГіОпЬхЖјУїШЗЕФЩЯЕчЪБађЭМЃЌШчЭМ4ЫљЪОЁЃВЂИљОнИУЩЯЕчЪБађЭМжИЕМЕчдДЩшМЦЪБЕчдДICЕФЩЯЕчЯШКѓЫГађЁЃ  ЭМ4 Ш§ЁЂ PDSЯЕЭГЩшМЦ PDSЯЕЭГЕФЩшМЦзюживЊЕФВПЗжОЭЪЧЭЫёюКЭХдТЗЕчШнбЁдёКЭЗжВМЃЌКмЖрШЫШЯЮЊХдТЗКЭЭЫёюЕФзїгУЪЧвЛбљЕФЃЌЖјЪЕМЪЩЯЪЧВЛЭЌЕФЁЃ 1. ЭЫёюКЭХдТЗЕчШнЙЄзїдРэ 1ЃЉ ХдТЗЕФФЃаЭШчЭМ ЕБICФкВПГіЯжИпЦЕЕФЕчСїВЈЖЏЃЌБШШчI/OЛђУХЕФПЊЙиЃЌетаЉИпЦЕЕФЫВЬЌЕчСїБфЛЏШчЙћДгЕчдДЮќШЁЕчСїЛсв§Ц№ЕчСїЕФИпЦЕВЈЖЏЃЌЖјЕчСїдДЕФФкзшКЭЕчдДзпЯпдкИпЦЕЪБГЪИаадзшПЙLЃЌЦЕТЪдНИпзшПЙдНДѓЃЌДгЖјв§Ц№ICЕчдДв§НХДІНЯДѓЕФбЙНЕЁЃвђДЫдкППНќICЕчдДв§НХЗХжУЕчШнCbpЮЊICЬсЙЉЫВЬЌЕчСїЃЌдкЫВЬЌЕчСїБфЛЏЪБICв§НХЛсДгЕЭзшПЙЕФЕчШнCЩЯЮќШЁЕчСїЃЈРэТлЩЯЕчСїПЩвдДгЕчдДЯпКЭЕчШнСНЬѕЭООЖСїЖЏЃЌЕЋЪЧЕчШнзшПЙЕЭЃЌЫљвдЕчСїЛсжївЊбизХЕчШнСїЖЏЃЉЁЃЕчШнЕчбЙЯТНЕКѓЛсДгЕчдДЯпЩЯВЙГфЕчКЩЁЃБОжЪЩЯХдТЗЕчШнЕФзїгУМѕЩйЕчдДЯпЩЯЕФЫВЬЌЃЈИпЦЕЃЉЕчСїВЈЖЏЁЃ ХдТЗЕчШнЮЊИпЦЕГфЗХЕчЬсЙЉЕчКЩЃЌвђДЫЫќЕФESRКЭESLЃЈАќКЌЕНЕчдДв§НХв§ЯпЕчИаЃЉгІИУОЁСПЕЭЃЌОЁСПППНќЕчдДв§НХЃЌГЃгУЕФХдТЗЕчШнЪЧаЁШнСПЕФЃЈ0.1uFЁЂ0.01uFЕШЃЉЬеДЩЕчШнЁЃ 2ЃЉ ЭЫёюЕФФЃаЭШчЭМ ЕчТЗIC1ЩЯВЛПЩБмУтЕФЛсдкЕчдДЯпЩЯВњЩњвЛаЉдыЩљЛђепЕчСїВЈЖЏЃЈжївЊЪЧНЯЕЭЦЕЖЮЃЌвђЮЊИпЦЕЕФЕчСїВЈЖЏПЩвдБЛЫќЕФХдТЗЕчШнЯћГ§ЃЉЃЌШчЙћвЛИіЕчдДЭЌЪБЮЊЖрИіICФЃПщЙЉЕчЃЌЦфжавЛИіICЩЯЕФдыЩљОЭЛсДЋЕнЕНСэЭтвЛИіICЕчТЗЁЃЮЊСЫМѕЩйФЃПщжЎМфЕФдыЩљёюКЯЗХжУЕчШнCdecЃЌЫќКЭЕчдДЯпЩЯЕФЕчИазщГЩвЛИіLCЕЭЭЈТЫВЈЕчТЗЃЌЕБдыЩљЃЈРДздСэЭтвЛИіЕчТЗФЃПщЃЌЛђепРДздЕчдДБОЩэЃЌБШШчПЊЙиЕчдДБОЩэЪфГіЕчбЙОЭКЌгаДѓСПдыЩљЃЉбизХЕчдДЯпДЋЕнЕНФГвЛИіICЪБОЭЛсБЛетИіLCЕЭЭЈТЫВЈЦїЯћГ§ЁЃБОжЪЩЯЭЫёюЕчШнЕФзїгУЪЧБмУтЕчдДдыЩљДгвЛИіЕчТЗФЃПщДЋЕнЕНСэЭтвЛИіФЃПщЁЃЭЫёюЕчШнвЊТЫГ§ЕчдДЯпЩЯЕФНЯЕЭЦЕЕФдыЩљЃЌвђДЫLCЕЭЭЈТЫВЈЕФНижЙЦЕТЪвЊЕЭвЛаЉЃЌЭЌЪБCdecЕчШнЛЙгаЮЊКѓајЕчТЗЃЈАќКЌКмЖрХдТЗЕчШнЃЉЬсЙЉЕчКЩЁЂЮШЖЈЕчбЙЕФзїгУЃЌвђДЫЕчШнCdecШнСПНЯДѓЃЌГЃВЩгУДѓШнСПЃЈМИЪЎЕНМИАйuFЃЉЕФЬЙЕчШнЁЃ 2. ЭЫёюКЭХдТЗЕчШнЕФДѓаЁМАЮЛжУ ЭЫёюКЭХдТЗЕФзюжеФПЕФЪЧвЊдкICЕФЕчдДв§НХДІВњЩњЮШЖЈЕФЕчбЙЃЌЫќУЧЖМвЊЧѓОЁСПППНќICЕФЕчдДв§НХЃЌдкЪЕМЪЕФЯЕЭГжагаЪБВЂВЛашвЊПЬвтЧјЗжЭЫёюЕчШнКЭХдТЗЕчШнЃЌЖјЭГГЦЮЊЭЫёюЕчШнЁЃ 1ЃЉ аЁШнСПЬеДЩЕчШнЃЈвЛАу0.01uF"0.22uFЃЉзїЮЊХдТЗЕчШнЃЌЫќЕФЗХжУддђЪЧОЁСПМѕаЁESLЃЌвЛАуВЩгУ0402ЗтзАЃЌгІИУЗХжУдкзюППНќЕчдДв§НХЕФЕиЗНЁЃЯждкДѓСПЕФИпУмЖШМЏГЩЕчТЗВЩгУЕФЖМЪЧBGAЕФЗтзАЃЌЫќЕФЫљгав§НХЖМдкChipЯТВПЃЌЭЈЙ§в§НХballКЭPCBАцЕФTopВуКИХЬЯрСЌЃЌЕчдДзмЯпЛђЦНУцвЛАуЭЈЙ§ViaЙ§ПзбгЩьЕНаОЦЌЗтзАЯТВПЕФЕчдДв§НХЁЃЫљвдзюППНќЕчдДв§НХЕФЮЛжУОЭЪЧаОЦЌЗтзАЕФЯТВПPCBЕФБГУцЃЌЕчШнЕФPADзюКУКЭЙ§ПзviaжБНгЯрСЌЁЃгааЉаОЦЌвВЛсжБНгдкЗтзАЬхsubstrateЩЯКИгаЕчШнЃЌетбљОЭПЩвдМѕЩйдкPCBАхЩЯЕФХдТЗЕчШнЪ§СПЁЃ  2ЃЉ ДѓШнСПЕФЭЫёюЕчШнЃЈвЛАу>33uFЃЉЃЌвЛАуЗтзАБШНЯДѓЃЌВЛПЩФмЬиБ№ППНќаОЦЌЕФв§НХЃЌВЛЙ§етРрЕчШнгУгкТЫГ§НЯЕЭЦЕТЪЕФдыЩљЃЌЖдЗХжУЕФЮЛжУВЛЪЧЬиБ№УєИаЃЌЫљвдзюКЯЪЪЕФЮЛжУПЩФмдкаОЦЌЕФБпдЕППНќаОЦЌЕФЮЛжУЁЃ 3ЃЉ гаЪБвВЛсдкЭЫёюCdecКЭХдТЗЕчШнCbpжаМфЗХжУвЛаЉШнСПдкМИИіuFЃЈ2.2uFЕШЃЉЕФЬеДЩЕчШнзїЮЊжаМфМЖЃЌвЛАуШЯЮЊЫќУЧЪЧгУРДТЫГ§вЛаЉжаМфЦЕТЪЕФдыЩљЃЌВЂЮЊИННќЕФХдТЗЕчШнЬсЙЉЕчКЩЃЌетаЉЕчШнвЛАуВЩгУ0805ЕФЗтзАЃЌвВгІИУОЁСПППНќЕчдДЕФв§НХДІЁЃ дкбЁдёОпЬхЕФЕчШнЪБЛЙвЊПМТЧЕНЦфESRЕФДѓаЁЁЂдыЩљЕФЦЕТЪИпЕЭЕШвђЫиЃЌВЂШЗЖЈЕчШнЕФЪ§СПЃЌгаЪБЛЙашвЊЭЈЙ§ЪЪЕБЕФЗТецsimulationРДАяжњЩшМЦЁЃ 3. PDSЗжВМЩшМЦЪЕР§ Р§зг1 BGAЗтзАаОЦЌЕФЕчдДв§НХМЏжадкаОЦЌЕФжааФИННќЃЌЕчдДЭЈЙ§РрЫЦbusЕФЗНЪНСЌНгЕНаОЦЌЕФжааФЧјЃЌПЩФмЕФЕчШнВМОжШчЭМЃЌЩЯЯТСНБпЮЊ0.1uFКЭ0.01uFЕФаЁЕчШнЃЌжааФЮЊ2.2uFЕФЬеДЩЕчШнЃЌЬЙЕчШнЗХжУдкаОЦЌБпдЕЃЌОпЬхЕФВМОжКЭЙ§ПзЕФЮЛжУашвЊИљОнЕчдДв§НХЕФЗжВМОпЬхЕФЕїећЃЌддђЩЯгІИУЪЧвЛДѓвЛЃЈЛђМИЃЉаЁНјааХфЖдЁЃ Р§зг2 ВЩгУЕчдДЦНУцЕФЗНЪНЃЌЭЫёюЕчШнЗХжУдкаОЦЌБпдЕДІППНќIC2ЕФЕиЗНЃЌIC1/IC3ЮЊЦфЫћЪЙгУИУЕчдДЕФаОЦЌЃЌIC2жааФЮЊаЁЕчШнКЭжаЕШШнСПЬеДЩЕчШнЁЃ |

ЭјгбЦРТл