基于LabVIEW与USB的虚拟仪器接口设计

发布时间:2010-8-13 15:30

发布者:lavida

|

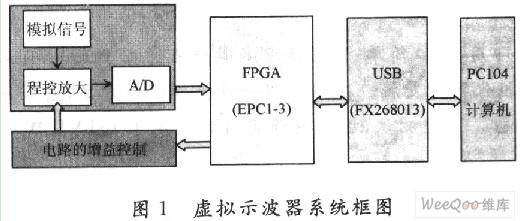

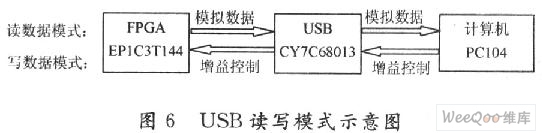

LabVIEW是一种基于图形程序的虚拟仪器编程语言,与传统仪器相比,虚拟仪器技术以计算机为平台,在程序界面中有用于模拟真实仪器面板的控件可供调用,可用于设置输入数值、观察输出值以及实现图表、文本等显示,因此具有友好的人机界面。LabVIEW具有强大的数据采集、分析、处理、显示和存储功能。在测试与测量、数据采集、仪器控制、数字信号分析、工厂自动化等领域获得了广泛的应用,显示出其强劲的生命力。LabVIEW平台下开发的虚拟仪器在相同硬件条件下,改变软件即可实现不同的仪器功能,真正实现了“软件即仪器”的设计理念。 实现LabVIEW对数据的采集和处理,传统的方法是采用数据采集卡,但是这些数据采集卡设备存在安装不便,价格昂贵,受计算机插槽数量、地址、中断资源的限制,可扩展性差等缺点。在LabVIEW平台下使用USB总线进行数据传输,由于USB接口总线具有即插即用,接口简单,传送速率高等特点,因此基于Lab-VIEW和USB接口的虚拟仪器具有灵活、可靠、经济等特点。 鉴于以上LabVIEW和USB接口仪器的优点,实现LabVIEW下USB接口的接口程序就显得尤为重要。在此,介绍了一种基于LabVIEW与USB的虚拟仪器接口设计的方法。 1 设计方案 由于各类基于USB总线的数据采集、控制的虚拟仪器都涉及到LabVIEW与USB接口程序的设计,为了不失一般性,这里以虚拟示波器为例,介绍该接口程序的设计方法。 1.1 硬件设计方案 该系统是虚拟示波器,主要工作是采集被测模拟信号,并将信号通过USB2.o接口传输到PC104计算机,运行计算机LabVIEW平台下的应用软件完成数据的处理与记录,并在显示器上绘制曲线。 该系统主要由模拟信号采集模块、FPGA控制模块、USB传输模块和计算机组成,其系统结构框图如图1所示。  1.1.1 FPGA控制模块 该设计采用Alter公司的Cyclone系列现场可编程门阵列(Field Programmable Gate Array,FPGA),芯片EP1c3T144来实现高速数据控制及传输。 EP1C3T144采用TPFQ封装,拥有100个I/O口和2 910个逻辑单元,是一种高密度、高性能的FPGA。 FPGA的主要功能是高速数据采集、数据帧控制,以及与USB单片机进行通信。具体说明如下: (1)高速数据采集及增益控制。高速数据采集功能是控制高速A/D的时序进行数据采集;增益控制功能是通过向程控增益放大电路发送控制命令,进而达到控制模拟电路放大倍数的目的。由于篇幅关系,有关这两个方面的内容不做详细介绍。 (2)数据帧控制。FPGA每秒向PC机发送100帧和每帧512 B的数据,将如此高速的数据进行准确无误的控制和传输是系统的技术难点之一。该方案中,每帧数据由3部分组成:如图2所示。  其中,每一帧数据的开始位和结束位是固定数据,计算机的测井应用软件判断接收到每一帧数据的帧头及帧尾是否错误。若出现错误,将该帧数据丢弃,同时准备接收下一帧数据。数据第二部分,模拟信号由FPGA控制A/D芯片采集得到。 1.1.2 USB传输模块 Cypress公司的。EZ-USB FX2芯片CY7C68013是一款性能较高的USB 2.0微控制器。在单片机上集成USB 2.O收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。Ez-USB FX2中的智能SIE可以处理大部分USB 2.0协议,使得微控制器可以专注于应用功能,从而减少了开发时间,确保了USB的兼容性。 CY7C68013有3种可用的接口模式:端口、GPIF主控和Slave FIFO方式。在该系统中,根据系统对数据传输速度和实时性的要求,配置CY7C68013工作的接口模式为Slave FIFO模式。在Slave FIFO模式下,外部逻辑或外部处理器直接与FX2端点FIFO相连。这种模式下,外部主控器FPGA通过异步方式与CY7C68013进行数据通信。 FPGA与CY7C68013之间的硬件接口框图如图3所示。SL_WR/SL_RD是Slave FIFO的写使能/读允许信号。FPGA向CY7C68013提供Slave FIFO输出允许信号SL_OE,仅在数据输出时有效。FB[7:O]为8位双向数据总线。ADDR[1:0]为FIFO端点选择信号。在数据输入时固定为00,选择的是端点2;在数据输出时固定为10,选择的是端点6。  1.2 软件设计方案 为了能够在LabVIEW中充分利用其他编程语言的优势,LabVIEW提供了强大的外部程序接口能力。这些接口包括DLL,C语言接口(CIN),ActiveX,.NET,DDE,Matlab等。通过DLL,可以方便地调用c,VC,VB等编程语言编写的程序以及Windows自带的大量API函数。动态链接库(Dynamic LinkLibrary,DLL)是一个可以多方共享的程序模块,内部对共享的例程和资源进行了封装。动态链接库文件的扩展名一般是.dll,DLL和可执行文件(exe)非常相似,最大的区别在于DLL虽然包含了可执行代码却不能单独执行,必须由Windows应用程序直接或间接调用。 因此,开发上层应用软件的首要工作是DLL动态链接库的开发,在这里DLL动态链接库采用VC++6.0进行开发。LabVIEW调用DLL示意图如图4所示,由于DLL能够调用API函数与USB设备进行通信,而采用NI公司的虚拟仪器软件开发平台LabVIEW可以充分发挥虚拟仪器的灵活性。因此,将两者优势结合起来,该设计的虚拟示波器用户控制面板具有界面友好,操作直观等优点,通过面板上的各种控件便可实现数据的采集、存储、再现及分析等功能。  2 软件设计 软件设计是虚拟仪器开发的必备环节。基于LabVIEW与USB的虚拟仪器的软件设计分为4部分:主机操作系统上的客户驱动程序、主机应用程序、Ez-USB FX2的固件程序以及FPGA软件。 2.1 驱动程序 主机软件部分包括USB客户驱动程序和主机应用程序。USB客户驱程序是支持即插即用功能的标准WDM驱动程序,它为实现控制传输、中断传输和批传输提供了标准接口函数。一般情况下Cypress公司所提供的客户驱动程序已经能够满足需求,如果有特别的需求,可以在其基础上开发自己的驱动程序。 2.2 应用程序LabVIEW调用DLL 主机应用程序是系统与用户的接口,需要一个图形用户界面来控制所调用的函数,这里采用LabVIEW来编写应用程序。它通过调用DLL与驱动程序进行通信,以完成对外设的数据传输。在编写用户程序时,首先要建立与外设的连接,然后才能实施数据的传输。在DLL程序中主要用到2个API函数:一是利用Create-File得到USB句柄;二是利用DeviceIoControl来向设备驱动程序发送请求,完成在EZ-USB FX2中数据批传输的读取与写入。 采用LabVIEw来设计这里的应用程序,关键是通过Call Library Function节点来调用前面所编写DLL文件中的各个函数。该节点位于Functions Palette的Connectivity |Libraries & Executables | Call LibraryFunction Node,如图5所示。 通过CLF节点来调用前面所编写的DLL步骤如下: (1)单击该节点将其放置在程序框图中,此时该节点没有与任何DLL连接; (2)右击该节点并选择Configure选项或者直接双击该节点可以打开库函数配置对话框; (3)在该模块的属性设置中选择DLL文件中所包含的某个函数,然后再设置好函数的返回类型和参数类型。这样就可以使LabVIEW调用DLL文件中的一个函数(针对DLL中的每个函数都需要设置一个CallLibrary Function Node)。最后把该模块的另一端连接到显示模块,就可以显示从USB接口读进的数据。 2.3 EZ-USB FX2的固件程序 固件程序是指运行在设备CPU中的程序。只有在该程序运行时,外设才能称之为具有特定功能的外部设备。固件程序负责初始化各硬件单元,重新配置设备。固件代码的存储位置一般有2种: 第一种是存在主机中,设备加电后由驱动程序把固件下载到片内RAM后执行,即“重新枚举”; 第二种是把固件代码固化到1片E2RPOM中,外设加电后由FX2通过I2C总线下载到片内RAM后自动执行。笔者选用第一种方式,这种方式便于系统的调试和升级。 为了简化和加速用户使用EZ-USB FX2芯片进行USB外设的开发过程,Cypress公司提供了一个完整的固件程序架构,用户只需要提供一个USB描述符表,添加其他端点接收和发送数据的通信代码,以及控制外围电路的程序代码。具体操作可以参考文献[1]中的内容。 2.4 FPGA软件 该系统采用VHDL和BlockDiagram/Schematic相结合的方法来对各功能模块进行逻辑描述,然后通过EDA开发平台,对FPGA芯片进行编程,实现系统的设计要求。 数据采集系统的数据方向是双向的。从计算机端来看,“读数据”即FPGA通过CY7C68013向计算机发送测井数据;“写数据”即计算机通过CY7C68013向FPGA发送测井命令。 如图6所示,“读数据模式”的工作原理是计算机在数据采集模式下,CY7C68013的PD7被设置为低电平,FPGA判断该位电平为低,则工作在向USB发送数据模式。此时,FPGA判断USB单片机FULL管脚是否有效,若CY7C68013中FIFO6未满,则一直向FIFO6发送数据。计算机接收到被A/D数据后,完成计算、绘图、保存等功能。  “写数据模式”的工作原理:计算机在发送命令模式下,CY7C68013的PD7被设置为高电平,FPGA判断该位电平为高,则工作在接收USB发送命令模式。此时,FPGA判断USB单片机EMPTY管脚是否有效,若CY7C68013中FIFO2未空,则一直读取FIFO2中的命令数据,同时根据命令改变A/D采集的通道数和程控放大器的增益值。 3 结语 设计的基于LabVIEW与USB的虚拟仪器不但具有体积小,功耗低,成本低,使用灵活方便,硬件电路简单,可在线更新等特点;而且还充分利用了微机资源和LabVIEw的灵活性,因而易开发,且扩展性好。目前,基于LabVIEW与USB的虚拟仪器已经用于我校电子电工实验室建设之中,能达到高速数据传输、记录及显示的要求,具有较高的实用价值。 |

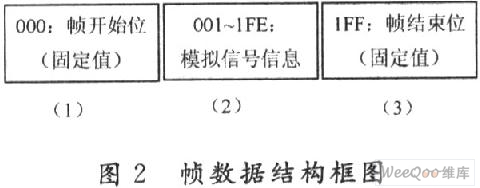

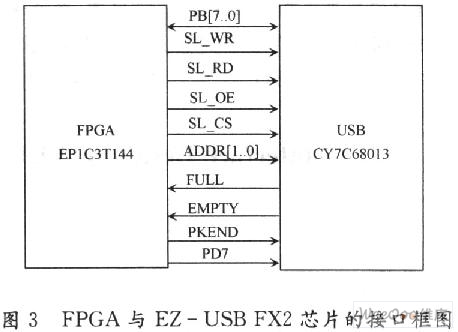

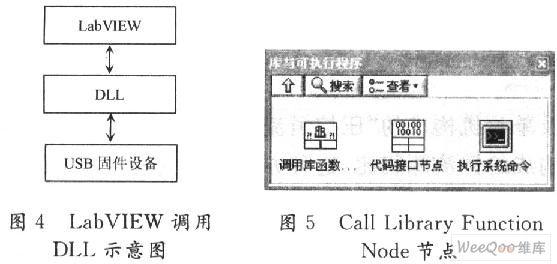

网友评论