基于NiosII的自动指纹识别系统设计

发布时间:2010-8-7 09:55

发布者:lavida

|

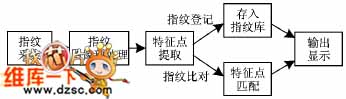

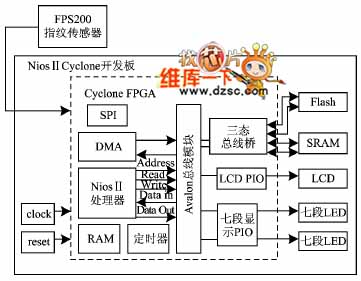

指纹识别作为生物特征识别的一种,在身份识别上有着其他手段不可比拟的优越性:人的指纹具有唯一性和稳定性的特点;随着指纹传感器性能的提高和价格的降低,指纹的采集相对容易;指纹的识别算法已经较为成熟。由于指纹识别的诸多优点,指纹识别技术已经逐渐走入民用市场,并应用到许多嵌入式设备中。 目前的嵌入式处理器种类繁多。Altera公司的Nios II处理器是用于可编程逻辑器件的可配置的软核处理器,与Altera的低成本的Cyclone FPGA组合,具有很高的性能价格比。本系统采用Nios II和Cyclone EP1C20嵌入式系统开发板,以及Veridicom公司的FPS200指纹传感器芯片,实现了一个嵌入式自动指纹识别系统。 1 总体设计及系统架构 本系统有两大功能:指纹登记和指纹比对。指纹登记主要包括指纹采集、指纹图像预处理、特征点提取、特征模板存储和输出显示;指纹比对的前三步与指纹登记相同,但在特征点提取后,是将生成的特征模板与存储在指纹特征模板库中的特征模板进行特征匹配,最后输出显示匹配结果。自动指纹识别系统的基本原理框图如图1所示。  图1 自动指纹识别的基本原理框图 本系统在结构上分为三层:系统硬件平台、操作系统和指纹识别算法。系统层次结构如图2所示。  图2 系统层次 最底层——系统硬件平台,是系统的物理基础,提供软件的运行平台和通信接口。系统的硬件平台在Altera的Nios II Cyclone嵌入式系统开发板上实现,指纹传感器采用美国Veridicom公司的FPS200。FPS200可输出大小为256×300像素、分辨率为500 dpi的灰度图像。 可靠性。这一层提供任务调度以及接口驱动,同时,通过硬件中断来实现系统对外界的通信请求的实时响应,如对指纹采集的控制、对串口通信的控制等。这种方式可以提高系统的运行效率。 最上层是指纹识别核心算法的实现。该算法高效地对采集到的指纹进行处理和匹配。采用C语言在Nios II的集成开发环境(IDE)中实现。 2 系统硬件的设计与实现 2.1 Nios II嵌入式软核处理器简介 Nios II嵌入式处理器是Altera公司于2004年6月推出的第二代用于可编程逻辑器件的可配置的软核处理器,性能超过200 DMIPS。Nios II是基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合,编程至Altera的FPGA中。处理器具有32位指令集,32位数据通道和可配置的指令以及数据缓冲。它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统(SoPC)设计了一套综合解决方案。Nios II处理器系列包括三种内核:一种是高性能的内核(Nios II/f);一种是低成本内核(Nios II/e);一种是性能/成本折中的标准内核(Nios II/s),是前两种的平衡。本系统采用标准内核。 Nios II 处理器支持256 个具有固定或可变时钟周期操作的定制指令;允许Nios II设计人员利用扩展CPU指令集,通过提升那些对时间敏感的应用软件的运行速度,来提高系统性能。 2.2 硬件平台结构 系统的硬件平台结构如图3所示。  图3 系统硬件平台结构 本系统使用FPS200指纹传感器获取指纹图像。FPS200是电容式固态指纹传感器,采用CMOS技术,获取的图像为256×300像素,分辨率为500 dpi。该传感器提供三种接口方式:8位微机总线接口、集成USB全速接口和集成SPI接口。本系统采用集成SPI接口。指纹采集的程序流程是:首先初始化FPS200的各个寄存器,主要是放电电流寄存器(DCR)、放电时间寄存器(DTR)和增益控制寄存器(PGC)的设置;然后查询等待,指纹被FPS200采集进入数据寄存器后,通过DMA存入内存。 由于从指纹传感器采集到的指纹图像数据在80 KB左右,以DMA方式存入片内RAM。Nios II对指纹图像数据进行处理后,生成指纹特征模板,在指纹登记模式下,存入片外Flash中;在指纹比对模式下,与存储在Flash中的特征模板进行匹配,处理结果通过LCD和七段LED显示器输出显示。 本系统的硬件平台主要是在Altera的Nios II Cyclone嵌入式开发板上实现,选用Altera的Cyclone版本的Nios II开发套件,包括Nios II处理器、标准外围设备库、集成了SoPC Builder系统设计工具的QuartusII开发软件等。系统的主要组件Nios II的标准内核、片内存储器、SPI、UART、DMA控制器、并行I/O接口、Avalon总线、定时器等都集成在一块Altera的Cyclone FPGA芯片上,使用SoPC Builder来配置生成片上系统。 |

网友评论