桥式拓扑结构功率MOSFET驱动电路设计

发布时间:2010-8-1 13:01

发布者:lavida

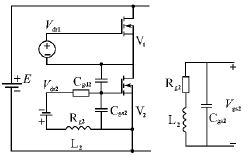

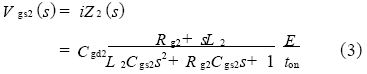

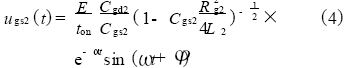

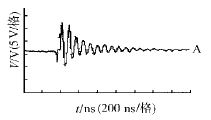

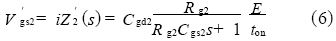

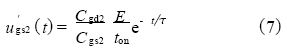

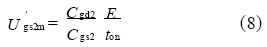

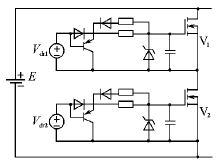

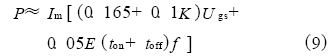

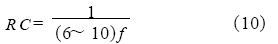

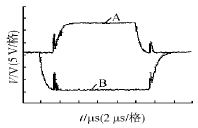

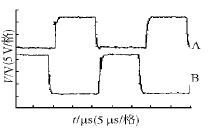

|

功率MOSFET以其开关速度快、驱动功率小和功耗低等优点在中小容量的变流器中得到了广泛的应用。当采用功率MOSFET桥式拓扑结构时,同一桥臂上的两个功率器件在转换过程中,栅极驱动信号会产生振荡,此时功率器件的损耗较大。当振荡幅值较高时,将使功率器件导通,从而造成功率开关管直通而损坏。目前常用的解决方法是在MOSFET关断时在栅极施加反压,以削弱振荡的影响,但反压电路却占用空间,同时增加了成本。本文在深入分析了MOSFET栅极振荡产生机理基础上,设计了硬件驱动电路。理论分析和实验结果表明,采用本文所提出的方法,只需增加较少的器件就能够最大程度地抑制振荡。 栅极驱动信号振荡的产生机理 由功率MOSFET的等效电路可知,3个极间均存在结电容,栅极输入端相当于一个容性网络,驱动电路存在着分布电感和驱动电阻,此时的桥式逆变电路如图1所示。以上管开通过程为例,当下管V2已经完全关断时,栅源极同电位。在上管开通过程中,设上管开通时间为ton,直流母线电压为E,由于开通过程时间很短,其漏源极电压迅速由直流母线电压下降到近似零,相当于在下管V2漏源极间突加一个电压E,形成很高的dv/dt。该dv/dt的数值与上管V1的开通速度有关,可近似认为   图1半桥式拓扑的等效电路 此时虽然下管已经完全关断,但是该dv/dt因结电容Cgd2的存在而对栅源极状态产生影响。 该dv/dt产生的位移电流为  在下管V2栅极产生的电压为  对其进行拉氏反变换可得  式中:  由上式可知,当上管开通时会在下管栅极产生阻尼衰减振荡信号,如图2所示。同理,当上管关断、下管开通时,上管栅极也同样会产生振荡,只是相位与前者相反,其幅值可以表示为  由于振荡频率很高,使MOSFET处于高频开关状态,产生很大的开关损耗。更严重的是若振荡的幅值达到MOSFET的门槛电压,下管将开通,而上管正处于导通状态,此时将造成上下功率管的直通现象,造成MOSFET的损坏。以上现象可以通过调整驱动电路参数加以抑制。  图2栅极振荡干扰实测波形 驱动电路的改进 减小分布电感 若取极限情况,驱动电路的分布电感为零,则驱动信号由式(3)简化为如下形式  对其进行拉氏反变换得  式中,S=Rg2Cgs2。 由上式可知此时振荡已经变为指数衰减形式,在t=0时为最大值  由上述分析可知,分布电感主要影响驱动信号振荡的暂态表现形式,若尽量减小分布电感,可使驱动信号由阻尼振荡变为指数衰减,即可消除MOSFET的高频开关损耗。同时亦可一定程度上降低振荡幅值。因此在设计电路时应该尽量使驱动芯片靠近MOSFET,并减小闭合回路所围的面积。如用导线连接应该使用双绞线或使用同轴电缆,以尽量减小分布电感。 开通和关断时间的配合与调整 由式(5)和式(8)可知,MOSFET的开通时间是影响驱动信号振荡幅值的主要因素,呈反比例关系。若适当增大器件的开通时间,即可在很大程度上减小振荡幅值,因此考虑在驱动芯片与MOSFET栅极间加设缓冲电路,即人为串接驱动电阻,在MOSFET栅源极间并联电容以延长栅极电容的充电时间,降低电压变化率。而MOSFET的关断时间与开通时间存在着一定的矛盾,若单纯增大开通时间,必然也增大了关断时间,而从减小死区时间角度,希望关断时间短一些,因此考虑调整MOSFET的开通和关断时间,在驱动电阻上反并联快恢复二极管,改变MOSFET开通和关断的时间常数,在开通时为减小dv/dt的应力,增加栅极的充电时间,而关断时间应短一些,以使用较短的死区时间减小输出波形的谐波含量,电路如图3所示。通过以上措施,可以实现在增大开通时间,减小电压变化率的同时,保证了较短的关断时间。  图3改进后驱动电路 理论上,开通时间越长dv/dt应力越小,振荡产生的干扰效果就越不显著,但是由MOSFET开关损耗近似公式  可知,开通与关断时间越长,MOSFET的开关损耗越大,另外开通时间还受工作频率的限制。 缓冲电路参数通常的选取原则为  式中:f为MOSFET的工作频率。 由于MOSFET通常工作在几十kHz的开关状态,其充放电电流由栅源极电容和驱动电压决定,若驱动电阻选的很大,使得电路损耗过大,不利于驱动电路的安全运行,因此要综合考虑电阻、电容的取值。一般驱动电阻的阻值为几十8,栅源极并联电容的取值以式(10)为参考。 其它措施 考虑到驱动信号振荡主要出现在桥臂一侧MOSFET的关断阶段,即栅源极为零电位时,由PNP三极管的工作原理,在驱动芯片与驱动电阻之间外接PNP三极管,当驱动芯片提供高电平时,三极管不导通,对电路逻辑不造成影响。在驱动芯片提供低电平过程中,当未产生振荡时,三极管基极与集电极电位均近似为零,三极管不工作;当MOSFET栅源极产生振荡时,三极管集电极电位为正,将饱和导通,振荡电压经反并联二极管和三极管迅速泄放,避免了MOSFET误导通。同时在栅源极间并联稳压管,进一步限制栅源极过压。最终改进后驱动电路如图3所示。 图4是工作频率f为40kHz,MOSFET未加缓冲电路的栅极驱动信号实测波形,此时驱动芯片直接与MOSFET的栅极相连,由于没有考虑分布电感的作用,芯片与MOSFET摆放位置相对较远。实际测得驱动电路分布电感L为135nH,驱动电阻近似为零,从图4中可以看出,改进前振荡的幅值很大,导致MOSFET发热严重,直至过热损坏,逆变器根本无法正常工作。驱动电路改进后,实际测得分布电感L为23.5nH,驱动电阻Rg取为30Ω,并联电容C取为0.01μF。实测栅极驱动波形如图5所示,可以看出改进后的电路很好地解决了栅极驱动信号的振荡问题。  图4改进前驱动信号波形  图5改进后驱动信号波形 结论 桥式拓扑结构功率MOSFET在开关转换过程中发生的直通现象是由于结电容、驱动电路的分布电感以及开关时产生较高的dv/dt在栅极产生振荡造成的。在分析了栅极驱动信号的振荡机理后,进行了驱动电路的优化设计,在栅源极增加了缓冲电路。与外加负压电路以及有源驱动电路相比,该电路具有实现简单、安全可靠的特点。采用该驱动电路实现的镇流器,长期运行并未发生过热和损坏MOSFET的现象。 |

网友评论