基于软件无线电的可调中频调制器的设计与实现

发布时间:2010-7-30 11:18

发布者:lavida

|

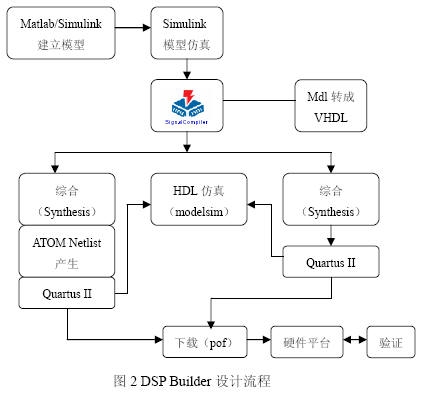

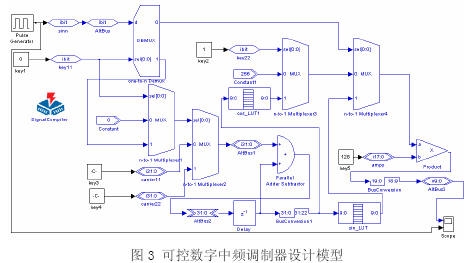

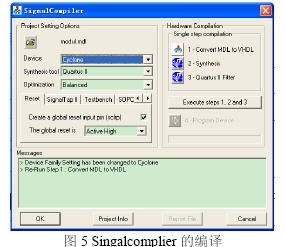

1.引言 软件无线电(software defined radio)是无线电系统从模拟到数字再向前发展的新阶段。其目标是在可编程的硬件平台上通过注入不同的软件,实现对工作频段、调制解调方式、信道多址方式等无线功能的改变。在软件无线电的研究过程中,调制解调技术是无线通信系统的重要组成部分。目前对于软件无线电调制技术的实现多是采用具有调制功能的专用芯片(其中应用较为广泛的是AD公司的AD985X系列)或是采用可编程器件结合专用芯片方法实现。然而在某些场合,调制方式和控制方式会与系统的要求差距很大。因而,完全采用高性能的FPGA器件设计出符合要求的调制电路就是一个很好的解决方法,此方法提供了一个良好的数字无线通讯系统的验证环境,可将多种调制算法在实验平台上实现,并通过平台提供的基本控制对系统进行验证仿真。并且用这种软件化硬件的设计方法,可以产生多种模式的数字调试方式,具有集成度高、易于升级等优点。 本文基于DDS(直接数字频率合成)的技术原理,采用Altera公司推出的在FPGA上进行DSP开发的开发工具DSP Builder软件,设计了一种适合与软件无线电使用的可调中频数字调制器,实现FSK、PSK、ASK三种调制方式,并通过FPGA芯片进行系统验证。 2.DDS的基本原理 DDS(Direct Digital Synthesize)即直接数字合成,是一种新型的频率合成技术,图1为DDS的基本实现原理结构图。  DDS以数控振荡器的方式,产生频率、相位和幅度可控的正弦波。电路包括相位累加器、相位调制器、正弦ROM查找表、基准时钟源、D/A转换器等组成。其中前三者是DDS结构中的数字部分,具有数控频率合成的功能。DDS是基于查找表方法,将一个正弦波周期的N个均匀采样点存储在存储器中,以均匀速率将这些采样点输送到DAC,即可得到一个单频正弦波,如果每隔K个采样点输出一个数据,则会得到K倍频的正弦波。但是,系统会存在一个上限频率,这取决于N的选择和系统的采样频率。设一正弦波为: s(t)=sin(w0t)=sin(2∏f0t) (1) 对其以采样频率fs进行采样,得到: s(n)=sin(2∏f0tTs) (2) 这样可以得到此正弦信号的相位增量为: △φ=2∏f0Ts=2∏f0/f (3) 将一个周期的正弦波均匀分为N份,取N为2的整数幂。则每一份的相位的大小是: δ=2∏/N (4) 如果每隔K个点输出一个采样值,则相位增量就是Kδ,输出频率为: f=Kδ/2∏Ts=Kfs/N (5) 根据采样定理,K应该满足K≤N/2。可以通过增加一个周期的采样点N,也就是增加采样频率得到更高的输出频率。这是计算中频调制参数的依据。 DDS与传统的频率合成技术相比,具有频率稳定度高,频率转换速度快,输出相对带宽宽,频率分辨率高等特点,将DDS的这些功能应用于软件无线电中,可以部分降低CPU的处理负担,使整个系统的性能达到较好的程度。 3. FSK、PSK、ASK调制原理 在数字通信系统中,数字基带信号通常要经过数字调制后再传输。常见的调制方式有频移键控(FSK)、相移键控(PSK)、幅移键控(ASK)等。 以基带数字波形序列来表示{ak},通常二进制数字基带信号表示为: m(t)=∑akg(t-kTb) 其中,ak为二元码符号,1或0;g()为单极性不归0波形,归一化幅度;Tb为二元序列码元间隔。 则频移键控(FSK)信号为: sFSK(t)= A0∑[akg1(t-kTb)cos(w1t+θ1)+(1-ak) g2(t-kTb)cos(w2t+θ2)] 其中w1为传号载频;w2为空号载频;θ1和θ2分别为传号与空号载波的初相,在[-∏, ∏]均匀分布;w0=(w1+ w2)/2为载波频率;kTb≤t≤(k+1) Tb。 相移键控(PSK)信号为: sPSK(t)=A0∑[akg1(t-kTb)cos(w1t+θ1)+(1-ak) g2(t-kTb)cos(w1t+θ2+∏)] 幅移键控(ASK)信号为: sASK(t)= m(t) c(t)= m(t)A0cos(w0t+θ0)= A0∑akg(t-kTb)cos(w0t+θ0) 实现上述调制的方式有多种,采用DDS技术做正交调制,能够克服解调输出的严重失真,提高抗噪声性能。对此正交调制表现在已调信号(传号与空号)各自的相关系数——正交关系。FSK和ASK相关系数均为ρ12=0,PSK的相关系数为ρ12=-1。一般的,要满足此条件,应考虑到载波频率f0是码元频率Rb=1/Tb整数倍,即f0=mRb,或1bit间隔包括整数个载波周期,即Tb=mT0,这将作为在DSP Builder中优化系统时的依据。 4.基于DSP Builder的可调中频调制模块设计 DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它提供了Quartus II 软件和Matlab/Simulink工具之间的接口。DSP Builder允许系统、算法和硬件设计去共享一个通用的开发平台,DSP Builder设计流程如图2。  根据DDS基本原理,基于Matlab/Simulink/Altera DSP Builder建立适合软件无线电应用的中频调制器模型如图3。电路全部采用有符号数,其中频率字为32位,幅度字为18位,分别控制载波的频率值及载波幅度值。系统由两个控制按键(key1和key2),一个信号输入端,三个初值输入端(key3、key4和key5)组成。其中key1和key2控制调制方式,key3和key4是载波的频率控制字输入口,key5是载波幅度控制字的输入端。  整个系统主要由一个DDS构成,包括两个查表ROM及其他控制电路。当key1、key2为11、01、00时,分别实现FSK、PSK、ASK调制;当key1、key2为10时无信号输出。在信号的输入端接收被调制的信号。由AltBus、Parallel Adder Substractor、Delay构成DDS的核心部分——相位累加器。正弦查找表模块LUT的计算式为: 255*sin( 10*[0:1*pi/(2^10):10*pi] ) +256 受存储器容量和成本限制,正弦查找表模块LUT容量有限,这里设置为10位,为了获得较高的频率分辨率,DDS模块的频率字设置为32位,也即相位累加器字长位32位,DDS将获得fclk/232。 要达到软件无线电传输标准的调制器设计,能够通过计算推算出频率字的取值。设基带码元速率为1kHz,系统采样频率为32MHz,即对每个码元采样32k个点,要达到一个中频载频取中频载频为:f1=600k,f2=1M,取N=232,根据式(5),可得其频率控制字分别为: Key1=80530637;key2=134217728;取幅度控制字key5=128。对此系统进行仿真验证。 5.系统仿真及硬件实现。 按照图3所示的调制器结构在Simulink中完成仿真系统的搭建,并对其进行系统级仿真,施加合适的激励,添加合适的观察区间,在模型窗口选择“Simulink”菜单,再选Start项仿真。双击Scope模块,分别得到FSK、PSK、ASK仿真波形,如图3。  通过Simulink系统级仿真后对模块进行编译,这在Simulink中自动完成后续的综合,时序分析等操作。通过SignalComplier(如图4)把Simulink的模块文件(.mdl)转换成通过的硬件描述语言VHDL文件,选定Cyclone系列芯片,并由QuartusII进行综合、适配、时序分析,最终得到可供下载使用的.sof文件。  打开Quartus II,进行Cyclone系列的EP1C6Q240C8芯片,进行重新编译,仿真,下载到芯片在示波器中验证了系统的调制功能。 6.结论 该设计避免了编写繁琐的硬件描述程序,同时避免了向ROM中填写大量的波形数据。充分利用了Matlab中Simulink的DSP Builder工具箱的图形化界面建模、系统仿真功能,同时又区别与完全图形化的方法。采用DDS技术,具有分辨率高、频率变化快、频率可控等优点,很好的实现了调制功能。实验证明,采用文中的方法设计的基于软件无线电的调制器具有较好的功能,基本满足一般应用的需求。而对于如何控制调制器的频率是下一步研究的内容。 |

网友评论