高速大深度新型FIFO存储器IDT72V3680的应用

发布时间:2010-7-28 12:47

发布者:lavida

|

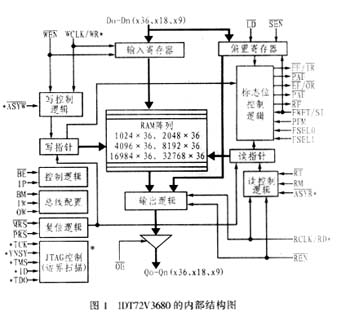

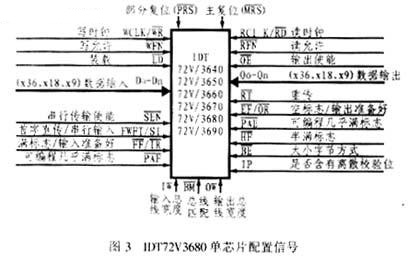

1 FIFO概述 FIFO芯片是一种具有存储功能的高速逻辑芯片,可在高速数字系统中用作数据缓存。FIFO通常利用双口RAM和读写地址产生模块来实现其功能。FIFO的接口信号包括异步写时钟(wr-clk)和读时钟(rd-clk)、与写时钟同步的写有效(wren)和写数据(wr-data)、与读时钟同步的读有效(rden)和读数据(rd-data)。写地址产生模块一般还根据读地址和写地址来产生FIFO的满标志。读地址产生模块一般根据读地址和写地址的差来产生FIFO的空标志。为了实现正确的读写和避免FIFO的上溢或下溢,通常还应给出与读时钟和写时钟同步的FIFO的空标志(empty)和满标志(full),以禁止读写操作。写地址产生模块通常根据写时钟和写有效信号来产生递增的写地址,而读地址产生模块则根据读时钟和读有效信号来产生递增的读地址。FIFO一般在操作时,首先在写时钟wr clk的上升沿且当wren有效时,将wrdata写入双口RAM中写地址对应的位置中,然后将读地址对应的双口RAM中的数据输出到读数据总线上,这样就可实现先进先出功能。读写操作一般会自动访问存储器中连续的存储单元。从FIFO中读出的数据顺序与写入的顺序相同,而地址的顺序则在内部已经预先定义好,因此,对FIFO芯片的操作不需要额外的地址信息。另外,FIFO芯片还能提供对读/写指针的复位功能。这些结构上的特点使FI-FO的应用大大简化了电路的复杂程度,提高了系统的可靠性和稳定性。由于微电子技术的飞速发展,新一代FIFO芯片的容量越来越大,体积也越来越小,价格越来越便宜,因而将在高性能、低功耗、快速数据处理系统中发挥越来越重要的作用。 2 IDT72V3680简介 2.1 IDT72V3680功能特点 IDT72V3680属于IDT公司的高密度supersyncTMⅡ36位系列存储器IDT72V3640~3690中的一种,其存储结构为16,384×36。这一系列CMOS工艺的FIFO(先入先出)芯片具有极大的深度。其基本功能特点如下: ●对读/写口都可进行灵活的总线宽度设置,可选择不同的输入/输出数据线宽度(可在36 in 36 out;36 in 18 out;36in 9 out;18 in 36 out;9in 36 out中选择); ●重传操作延时很低且固定; ●首字的写入到读出的延时很低且固定; ●数据密度高达1Mbit; ●操作时钟可达166MHz; ●可选大/小字节排列格式; ●主复位方式可提供FIFO整体清零,部分复位只清掉存储数据,但保留可编程设置项; ●几乎空/满标志置位或无效操作可选择同步或异步时间模式; ●具有两种时间工作模式,分别为 IDT标准模式(采用  和 和 标志位)和FWFT首字直传模式(采用 标志位)和FWFT首字直传模式(采用 标志位); 标志位);●读写操作采用独立时钟,并可异步操作; ●采用TQFP(128引脚)和PBGA(144引脚)两种封装形式,其中PBGA封装形式不仅可用JTAG口提供边界扫描功能,还可选择同步或者异步读写操作(只对PBGA封装); ●与5V输入兼容; ●具有节电模式; ●管脚可与更高密度的芯片IDT72V36100和IDT72V36110兼容。 IDT72V3680的内部结构框图如图1所示。  2.2 使用要点 IDT72V3680系列产品在使用中,通常应注意以下几点: (1)两种可选择的时间运行模式的区别 在主复位时,FWFT/SI信号电平为低表示选择IDT标准模式,否则表示选择首位字直传模式FWFT。在两种不同模式下,其输出的标志信号也有所不同,其中  、 、 为IDT标准模式; 为IDT标准模式; (输出准备好) (输出准备好) 输入准备好)为FWFT模式。另一个区别是在FWFT方式下,第一个写入字在三个读时钟上升沿后将直接传到输出Qn上,而不需要 输入准备好)为FWFT模式。另一个区别是在FWFT方式下,第一个写入字在三个读时钟上升沿后将直接传到输出Qn上,而不需要 信号有效,以后写入的字则需要 信号有效,以后写入的字则需要 信号有效才能通过Qn传出;而在IDT方式下,写入字都需要 信号有效才能通过Qn传出;而在IDT方式下,写入字都需要 有效才能读出数据。另外,FWFT在深度扩展时,FIFO可串行连接,即上一个FIFO的Qn直接连接下一个FI-FO的Dn,而无需额外控制逻辑。 有效才能读出数据。另外,FWFT在深度扩展时,FIFO可串行连接,即上一个FIFO的Qn直接连接下一个FI-FO的Dn,而无需额外控制逻辑。 (2)两种复位操作 IDT72V3680有主复位(MRS)和部分复位(PRS)两种方式(都属于异步操作)。当主复位启动后,读写指针都指向第一个数据位置,几乎空标志置低,几乎满标志和半满标志置高,同时,输入/输出的总线宽度、可编程标志位的同/异步方式以及是否需要去掉字节中的校验位均被确定,输出寄存器初始化为全零,上电即进行复位,以后才可进行写操作。而当部分复位后,只有读写指针复位,几乎空标志置低,几乎满标志和半满标志置高电平,其余各种运行方式不变,部分复位可在操作进行中进行复位,当经过编程设定的偏置值不理想时,可随时调用。 (3)加载操作 当  置高时,可以采用串行的方式加载可编程标志位以生效偏置值;而当其置低时,则采用并行方式加载。读出这些偏置值时,只能采用并行方式。加载和读出偏置值的操作既可以被中断以执行普通数据的读写操作,也可以在主复位时通过FSL1、FSL0选择缺省的8种偏置值。 置高时,可以采用串行的方式加载可编程标志位以生效偏置值;而当其置低时,则采用并行方式加载。读出这些偏置值时,只能采用并行方式。加载和读出偏置值的操作既可以被中断以执行普通数据的读写操作,也可以在主复位时通过FSL1、FSL0选择缺省的8种偏置值。(4)PAE、  几乎空/满标志可由PFM引脚输入并将其设定为同步或异步模式操作。在异步操作时,几乎空标高速大深度新型FIFO存储器IDT72V3680的应用志位电平在RCLK的上升沿降低,而在WCLK的上升沿电平升高;对于几乎满标志位,在WCLK的上升沿电平降低,而在RCLK的上升沿电平升高。在同步操作时,几乎空标志位只能随读时钟上升沿跳变,几乎满标志位只能随写时钟上升沿跳变。 (5)读写操作 读写操作可以通过异步读写引脚将读写操作设定为同步或异步方式。对于异步读写操作,芯片不能在FWFT模式下工作。  3 FIFO在高速数据传输系统中的应用 笔者所研究的高速数据传输系统是针对大容量的视频数据的压缩和解压缩性能研制的测试设备,在测试前后,需要将大容量的视频信号数据流从高档服务器中通过PCI接口读出或写入,系统所要求达到的指标是数据传输速率为62.5M字节/秒。PCI总线是高速端口,采用PCI总线进行数据传输,还应考虑到它与另一子系统间的数据传输协调及同步问题。如果这一子系统速率较低,整个系统的速率也将降低,PCI总线的优势将不能发挥出来。而采用FIFO存储器则不同,它不但提供了存储空间作为数据的缓冲,而且还可以在两个子系统之间提供一个“橡皮绷带式”(有弹性)的存储器,以使其在两端速率不一致的情况下,仍然可以实现两个子系统间的高速数据传输,而不需要解决相互同步和协调问题。IDT72V3680的工作时钟最高可达166MHz。 图2是FIFO所在的接口卡的结构框图。在这个设计中,PCI总线接口卡用来进行视频信号的高速传输和接收。双口存储器FIFO则作为PCI总线主控和后续或前端数据处理电路(如分路器、压缩、解压缩等电路)之间的数据通道。由于PCI总线经过PCI控制器转换后的插卡总线仍为同步总线,所以使用同步器件最能发挥总线的传输效率。在设计中,要求系统输出是8~12位长度的字节输出,而PCI总线的数据线输出位数是32位,由于该种FIFO有灵活的字节宽度匹配设置,因而免去了在逻辑设计中加入字节转换器的设计,这样不仅简化了控制逻辑设计的复杂度,而且提高了系统的速度及稳定性。该接口卡中的控制逻辑部分负责完成PCI9656的插卡总线和双口存储器之间的通信协议以及对前端或后端数据处理的传输控制。图3是IDT72V3680单芯片配置信号框图。  对FIFO芯片的时间运行模式、可编程标志位的时间模式、输入/输出字节宽度、缺省偏置值的选择等均可由拨动开关来设置;各标志位信号输出到控制逻辑可与前后端部分进行消息传递;读写时钟则由时钟产生电路提供。 4 结论 应用FIFO存储芯片可用其内部读写指针代替复杂的地址发生器,从而从硬件上简化了数据高速交换中与地址线相关的处理逻辑电路。高速FIFO存储芯片在PCI总线插卡设计中的应用能够保证高速系统数据传输的速度与效率。目前,FIFO芯片在众多的数据传输处理领域已得到广泛的应用。另外,由于FIFO存储芯片是成系列生产且功能相同,因此,随着存储容量的增加,外部引脚数不会增加,从而为以后系统的升级带来了方便。 |

网友评论