CMOSНјПсґ«ёРЖчУГПсЛШј¶Л«ІЙСщґжґўјјКх

·ўІјК±јдЈє2010-7-25 21:20

·ўІјХЯЈєlavida

|

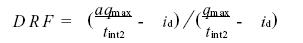

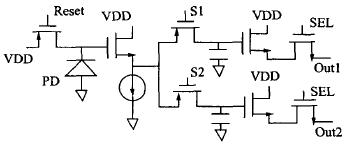

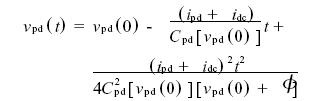

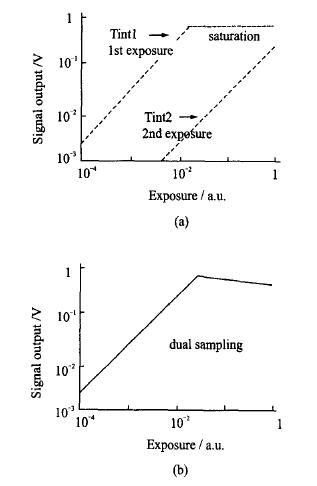

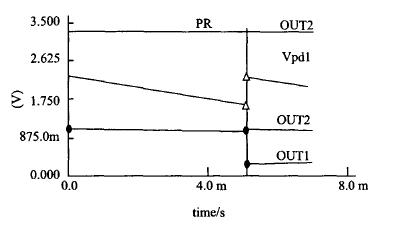

1 З°СФ ЅьР©ДкАґ,ЛжЧЕCMOSјјКхµД·ЙЛЩ·ўХ№,ТФј°іЦРшФцјУµДУ¦УГРиЗу,CMOSНјПсґ«ёРЖчјјКхµГТФСёЛЩ·ўХ№ЎЈCMOSНјПсґ«ёРЖчѕЯУРёЯ¶ИјЇіЙ»ЇЎў№¦єДµНЎўµҐТ»№¤ЧчµзС№ЎўѕЦІїПсЛШїЙ±аіМЛж»ъ¶БИЎµИУЕµгЎЈµ«ЛжЧЕУ¦УГµДРиТЄ,CMOSНјПсґ«ёРЖчµД¶ЇМ¬·¶О§УРґэЅшТ»ІЅМбёЯ,ИзµдРНµДCMOSAPS(ActivePixelSensor)НјПсґ«ёРЖч¶ЇМ¬·¶О§ОЄ65Ў«75dB,ДСУЪВъЧгёьїнХХ¶И·¶О§ЙгПсіЎѕ°ТЄЗуЎЈТ»°гАґЛµ,ѕЯУРЅПёЯ¶ЇМ¬·¶О§µДґ«ёРЖчїЙТФМЅІвёьїнµДіЎѕ°ХХ¶И·¶О§,ґУ¶шїЙТФІъЙъёь¶аПёЅЪµДНјПс,їЙТФЛµ,¶ЇМ¬·¶О§ФЪТ»¶ЁТвТеЙП,ѕц¶ЁЧЕCMOSНјПсґ«ёРЖчµДЦКБїЎЈCMOSAPSНјПсґ«ёРЖч¶ЇМ¬·¶О§µДА©Х№їЙІЙУГёчЦЦ·Ѕ·Ё,ЖдЦР¶аґОЖШ№вјјКхКЗТ»ЦЦЅПОЄУРР§µД·Ѕ·Ё,ЖдФЪ»сµГёЯ¶ЇМ¬·¶О§µДН¬К±,УРЅПёЯµДРЕФл±ИSNRЎЈІЙУГ¶аґОЖШ№в·Ѕ·Ё,Т»·щіЎѕ°ТФІ»Н¬µДЖШ№вК±јд±»ЙгПсјёґО,ЛщІ¶»сНјПсУГУЪЧйєПіЙёьёЯ¶ЇМ¬·¶О§µДНјПс,ЖШ№вґОКэУъ¶а,РЕєЕ±д»Ї·¶О§УъѕщФИ,µ«¶аУЪБЅґОµДЖШ№в,Т»°гРиТЄФЪЖ¬ЙП»тЖ¬НвґжґўЖчЦ§іЦ,РЕєЕґ¦АнёґФУ,К№ґ«ёРЖчµДЦЎЖµКЬµЅПЮЦЖ,Из№ыФЪПсЛШДЪУ¦УГБЅґОЖШ№вІЙСщґжґўµД·Ѕ·Ё,їЙФЪА©Х№¶ЇМ¬·¶О§»щґЎЙП,ККєПУЪёЯЛЩУ¦УГіЎєПЎЈ 2 ПсЛШј¶ІЙСщґжґўјјКхµД№¤ЧчФАн ОЄБЛА©Х№CMOSНјПсґ«ёРЖчµД¶ЇМ¬·¶О§,їЙУ¦УГБЅґОЖШ№в·Ѕ·Ё,јґТ»·щіЎѕ°УГі¤»э·ЦК±јдЖШ№вєН¶М»э·ЦК±јдЖШ№вЙгПсБЅґО,БЅ·щНјПсЧйєПіЙТ»·щёЯ¶ЇМ¬·¶О§µДНјПсЎЈґУАнВЫЙПЛµ,¶МµД»э·ЦК±јдНјПсІ¶»сБЛіЎѕ°ёЯХХ¶ИЗшУт,і¤»э·ЦК±јдНјПсФЪЧг№»µД»э·ЦК±јдєу,І¶»сБЛіЎѕ°µНХХ¶ИЗшУт,Иф¶МЖШ№вК±јдОЄTint2єНі¤ЖШ№вК±јдОЄTint1,Фтґ«ёРЖчµД¶ЇМ¬·¶О§ФцЗїТтЧУDRFОЄ:  ЖдЦР,qmaxКЗґ«ёРЖчµДЧоґуЪеИЭ,a=Tint1/Tint2,idКЗ°µµзБчЎЈїЙјы,µ±°µµзБчЅПРЎК±,¶ЇМ¬·¶О§ФцЗїТтЧУОЄa,Н¬К±АнВЫ·ЦОц±нГчЛ«ІЙСщјјКхТІїЙ»сµГЅПёЯРЕФл±ИSNRЎЈФЪCMOSAPSНјПсґ«ёРЖчЦР,ІЙУГґ«НіµДPD(PhotoDiode)APSПсЛШЅб№№,У¦УГБЅґОЖШ№в·Ѕ·Ё,ІЙУГБЅёцІўРРБРРЕєЕґ¦АнВ·ѕ¶КµПЦЛ«ІЙСщ,їЙТФН¬К±¶БіцБЅ·щНјПс,ЛдИ»їЙ»сµГїн¶ЇМ¬·¶О§µДНјПс,µ«НјПсЧйєПґ¦АнФЪЖ¬НвЦґРР,К№µГНјПсµДКµК±ґ¦АнЛЩ¶ИКЬµЅТ»¶ЁµДПЮЦЖ,ДСУЪВъЧгёЯЛЩУ¦УГіЎєПµДТЄЗуЎЈ ОЄБЛДЬ№»ФЪА©Х№¶ЇМ¬·¶О§Н¬К±,ЗТККєПУЪёЯЛЩУ¦УГіЎєП,Т»ЦЦїЙРРµД·Ѕ·ЁКЗУ¦УГПсЛШј¶ІЙСщґжґўјјКх,Ѕ«ЖШ№вІЙСщј°НјПсЧйєПґ¦АнФЪПсЛШДЪКµПЦ,ХвСщїЙУРР§МбёЯНјПсµДКµК±ґ¦АнЛЩ¶ИЎЈОЄґЛ,ИЛГЗ¶ФПсЛШј¶µДІЙСщґжґўјјКхЅшРРБЛ№г·єµДСРѕї,јёЦЦїЙДЬµДПсЛШµҐФЄЅб№№ИзНј1ЛщКѕЎЈНј1(a)ЦР,ІЙСщ±ЈіЦµзВ·ЦРЦ»ІЙУГMOSїЄ№Ш,ХвЦЦЅб№№ЛдИ»їЙ»сµГЅПРЎµДГж»э,µ«¶БіцКэѕЭК±,УлCMOSPPS(PassivePixelSensor)ПсЛШЅб№№АаЛЖ,ИЭТЧКЬФлЙщµДёЙИЕ,Тт¶шSNRЅПІо,ІўЗТ¶БИЎТ»ґОКэѕЭєу,ПсЛШДЪґжґўЖчC1ЙПКэѕЭРЕПў±»»Щ»µ,¶шКµјКУ¦УГЦРНщНщПЈНыДЬ№»¶ФПсЛШКэѕЭ¶аґО¶БИЎ,ХвРиТЄґжґўµзИЭЙПµДµзС№ЦµФЪ¶БИЎЖЪјд±ЈіЦІ»±д,ТтґЛХвЦЦЅб№№ДСУЪ»сµГїЙЅУКЬµДР§№ыЎЈ  Нј1ПсЛШј¶µДІЙСщґжґўјјКх:(a)Ц»УГMOSїЄ№Ш;(b)ІЙУГµҐј¶»єіеЖч;(c)ІЙУГБЅј¶»єіеЖч ОЄБЛёДЙЖ¶БіцФлЙщ,ІўЗТККєПУЪ¶аґО¶БИЎµДУ¦УГ,їЙФЪґжґўµзИЭC1єН¶БіцСЎНЁїЄ№ШЦ®јдФцјУ»єіеЖчA2,ИзНј1(b)ЛщКѕ,»єіеЖчТ»°гІЙУГјтµҐµДФґј«ёъЛжЖчЕдЦГЅб№№,єНµдРНµДCMOSAPSПсЛШЅб№№ПаЛЖ,ХвїЙТФУРР§ёДЙЖПсЛШµДРФДЬ,µ«ФцјУБЛПсЛШГж»эЎЈЛщ±ЁµАµДУ¦УГПсЛШґжґўјјКхµДCMOSНјПсґ«ёРЖчґу¶аІЙУГБЛХвЦЦЅб№№,ФЪХвЦЦЅб№№ЦР,ФЪ¶Ф№вГф¶юј«№ЬЙППсЛШРЕПўІЙСщЖЪјд,¶юј«№ЬЦР№вЙъµзєЙУлґжґўµзИЭC1№ІПн,µ±ІЙСщїЄ№ШґтїЄК±,УЙУЪMOSїЄ№ШµД·ЗАнПлМШРФ,µјЦВµзєЙЧўИлР§У¦,ТэЖрІЙСщОуІо,ОЄБЛјхРЎХвЦЦР§У¦,ФЪПсЛШЙијЖК±,РиТЄК№№вµз¶юј«№ЬµзИЭУлґжґўµзИЭµД±ИЦµЧојС»Ї,НЁіЈК№БЅХЯЅьЛЖПаµИЎЈОЄБЛМбёЯ№вЙъµзєЙµДКХјЇР§ВК,ёДЙЖSNR,Т»°г№вГф¶юј«№ЬУРЅПґуµДµзИЭ,ХвК№µГґжґўµзИЭТІУ¦µ±ѕЯУРІоІ»¶аН¬СщµДБїЦµ,¶шФґј«ёъЛжЖчA2Х¤ј«ЅЪµгґ¦µДјДЙъµзИЭПа¶ФЅПРЎ,ДСУЪВъЧгґжґўµзИЭµДРиТЄ,ЛщТФНЁіЈІЙУГCMOS№¤ТХЦРїЙРРµДѕЯУРБјєГРФДЬµДMOSµзИЭАґФцјУґжґўµзИЭ,УЙУЪ°жНјЙијЖ№жФтµДТЄЗу,К№ПсЛШГж»эУРЅПґуµДФцјУЎЈ ОЄБЛКµПЦПсЛШј¶µДЛ«ІЙСщєННјПсЧйєПґ¦Ан,їЙІЙУГНј1(b)АаЛЖµДПсЛШЅб№№,КЧПИЅшРРі¤К±јд»э·ЦЖШ№в,ІЙСщК±,і¤»э·ЦК±јдµД№вЙъµзєЙФЪ№вГф¶юј«№ЬµзИЭУлґжґўµзИЭјд№ІПн,И»єуЅшРР¶М»э·ЦК±јдЖШ№в,К№і¤¶МБЅґО»э·ЦК±јдЖШ№вµД№вЙъµзєЙФЪ№вГф¶юј«№ЬДЪЦ±ЅУЧйєП,ґУ¶ш»сµГ¶ЇМ¬·¶О§µДёДЙЖЎЈФЪХвЦЦПсЛШЅб№№ЦРЖШ№вДЈКЅІЙУГБЛґ«НіµД№ц¶ЇЖШ№в,¶шФЪТ»Р©№¤ТµєНїЖС§У¦УГЦР,іЈРиТЄ¶ФїмЛЩФЛ¶ЇµДДї±к»тВціе№вХХЙгПс,ИфІЙУГ№ц¶ЇЖШ№вДЈКЅЅ«µјЦВСПЦШµДФЛ¶ЇК§Хж,ґЛК±У¦ІЙУГѕЯУРН¬ІЅЖШ№вДЈКЅ,јґЛщУРПсЛШН¬К±»э·ЦЖШ№в,ЛжєуЅ«РЕєЕµзєЙґжґўµЅПсЛШДЪµДІЙСщ±ЈіЦµзИЭ,Т»Ц±µЅ¶БіцЎЈИз№ыК№ХвЦЦЅб№№ПсЛШ№¤ЧчУЪН¬ІЅЖШ№вДЈКЅ,УЙУЪНјПсЦ±ЅУЧйєПґ¦АнФЪ№вГф¶юј«№ЬДЪЅшРР,ИфФЪПсЛШКэѕЭ¶БіцµДН¬К±ЅшРРЖШ№вІЙСщЅ«»Щ»µµ±З°ЦЎµДКэѕЭ,ЛщТФКэѕЭµД¶БіцєНЖШ№вІ»ДЬН¬К±ЅшРР,ХвЅ«ј«ґуПЮЦЖБЛґ«ёРЖчµДКэѕЭґ¦АнЛЩ¶ИЎЈТтґЛ,ХвЦЦПсЛШЛ«ІЙСщ·Ѕ·ЁЛдИ»їЙТФ»сµГ¶ЇМ¬·¶О§µДёДЙЖ,µ«КЗДСУЪУ¦УГУЪРиТЄН¬ІЅЖШ№вµДёЯЛЩУ¦УГЎЈ їЙјыТЄККєПУЪН¬ІЅЖШ№вµДёЯЛЩУ¦УГ,Л«ІЙСщНјПсµДЧйєПґ¦АнІ»ДЬФЪ№вГф¶юј«№ЬДЪЦ±ЅУЅшРР,¶шЦ»ДЬФЪПсЛШДЪµДґжґўЖчДЪЅшРР,Т»ЦЦ·Ѕ·ЁКЗФЪНј1(b)Ѕб№№µД»щґЎЙПФЪПсЛШДЪФцјУБнТ»В·ІЙСщ±ЈіЦµзВ·,ИзОДПЧ[14]МбіцµДїЙТФЦ±ЅУЦЎІо¶БіцµДПсЛШЅб№№ЎЈµ«КЗ,ФЪХвЦЦПсЛШЅб№№ЦР,РиТЄБЅёцЅПґуµДґжґўµзИЭ,К№ПсЛШГж»эЅПґу,Хв¶ФУЪѕЮґуПсЛШХуБРґ«ёРЖчЅ«КЗДСУЪЅУКЬµДЎЈОЄБЛДЬ№»јхРЎґжґўµзИЭЛщХјГж»э,їЙІЙУГНј1(c)ЛщКѕµДЅб№№,ФЪ№вГф¶юј«№ЬєНґжґўµзИЭјдФцјУТ»ј¶»єіеЖчA1,ХвСщФЪБјєГSNRєНФКРн¶аґО¶БИЎµД»щґЎЙП,Из№ыґжґўДЬБ¦ДЬ№»ВъЧгУ¦УГРиЗу,ФтїЙТФІЙУГЅПРЎµДґжґўµзИЭЎЈТ»°г,µзИЭµДґжґўДЬБ¦УлВ©µзБчµјЦВµДµзИЭВ©µзєН№вµјЦВµзИЭµД·ЕµзУР№Ш,ЛжЧЕCMOS№¤ТХјјКхµДІ»¶ПёДЙЖЎўУРР§№вСЪ±О·Ѕ·ЁУ¦УГј°ЖдЛь№¤ТХјјКхИзЅ«PDЦГУЪЪеЦРЎўІЙУГ±Ј»¤»·ёфАлPDµИ,К№µзИЭµДґжґўДЬБ¦µГµЅБЛј«ґуёДЙЖ,К№µГФґЛжЖчХ¤ЅЪµгґ¦ЅПРЎјДЙъµзИЭїЙТФВъЧгґжґўµзИЭµДРиТЄЎЈХвСщЛдИ»ФЪПсЛШДЪФцјУБЛТ»ј¶»єіеЖч,µ«І»ФЩРиТЄГж»эЅПґуµД¶оНвMOSµзИЭ,ґУ¶шїЙДЬК№ПсЛШГж»эјхЙЩЎЈ 3 ПсЛШј¶Л«ІЙСщґжґўјјКх Т»ЦЦѕЯУРЛ«ІЙСщґжґў№¦ДЬµДПсЛШЅб№№ИзНј2ЛщКѕ,єНЦ±ЅУЦЎІоКдіцµДПсЛШЅб№№ПаАаЛЖ,ОЄБЛДЬ№»ФЪПсЛШј¶КµПЦЛ«ІЙСщґжґўєННјПсµДЦ±ЅУЧйєПґ¦Ан,ІўЗТККєПУЪН¬ІЅЖШ№вµДёЯЛЩУ¦УГ,ІЙУГБЛБЅВ·ІЙСщ±ЈіЦµзВ·,ІЙСщ±ЈіЦµзВ·УЙІЙСщїЄ№ШєН±ЈіЦЅЪµгЧйіЙ,ІЙСщїЄ№ШЧчОЄµзЧУЖШ№вЖчїШЦЖЖШ№вК±јдЎЈµ«І»Н¬µДКЗФЪРЕєЕІЙСщ¶БіцѕщІЙУГБЛ»єіеЖч,ИзЗ°ЛщКц,ХвК№µГІ»ФЩРиТЄБЅёц¶оНвµДMOSґжґўµзИЭ,Нј2ЦРЛщКѕґжґўµзИЭ±нКѕФґј«ёъЛжЖчХ¤ј«ЅЪµгґ¦µДЧЬјДЙъµзИЭ,ХвСщУРР§µШјхЙЩБЛПсЛШГж»э,їЙТФУ¦УГУЪѕЮґуПсЛШХуБРЗйїцЎЈ  Нј2Л«ІЙСщґжґўµДПсЛШЅб№№ Т»°гФЪПсЛШЙијЖЦР,ЛщУРѕ§Ме№ЬУ¦ѕЎБїІЙУГПаН¬µДАаРН,ТФ±ЬГвПсЛШ°жНјЦРЙијЖ№жФтЛщТЄЗуµДѕЮґуЪејдѕаЎЈИ»¶шµ±µзФґµзС№ЅПµНК±,РЕєЕµД°Ъ·щЅ«іЙОЄЦчТЄµДїјВЗЎЈИзёґО»(Reset)ІЙУГNMOSѕ§Ме№Ь,№вµз¶юј«№ЬЅцДЬёґО»µЅVDD-VT(VTОЄгРЦµµзС№),ПЮЦЖБЛґ«ёРЖчµД¶ЇМ¬·¶О§,ІўЗТЛжЧЕCMOSјјКхµД·ўХ№,МШХчіЯґзФЅАґФЅРЎ,VDD-VTПВЅµєЬїм,¶Ф¶ЇМ¬·¶О§У°ПмёьјУПФЦшЎЈБнТ»·ЅГж,ЛжЧЕЙоСЗОўГЧCMOSјјКхФЪCMOSНјПсґ«ёРЖчЦРµД№г·єІЙУГ,ОЄФЪПсЛШј¶ІЙУГРФДЬёьУРР§µД№¦ДЬµҐФЄМṩБЛЙијЖїХјд,Тт¶шФЪПсЛШЅб№№ЦРёґО»ѕ§Ме№ЬєНЖШ№вѕ§Ме№ЬѕщІЙУГБЛPMOSѕ§Ме№Ь,ХвІ»Ѕц±ЬГвБЛгРЦµµзС№ЅµµДЛрК§,ёДЙЖБЛ¶ЇМ¬·¶О§,ІўЗТїЙК№№вГф¶юј«№ЬНкИ«ёґО»,ґУ¶шПыіэНјПсНПОІПЦПу,Хв¶ФУЪёЯЛЩУ¦УГ·ЗіЈЦШТЄЎЈХвЦЦПсЛШЅб№№ЦРТ»ёцЗ±ФЪµДОКМвКЗРЕєЕІЙСщј¶»єіеЖчµД№¦єДОКМв,УЙУЪ±ЈіЦЅЪµгµзИЭЅПРЎ,Тт¶шїЙТФК№ёГј¶»єіеЖчЖ«ЦГµзБчѕЎїЙДЬРЎ,ОЄБЛЅшТ»ІЅјхРЎ№¦єД,У¦К№ЖдЦ»УРФЪІЙСщS1єНS2РЕєЕУРР§К±ј¤»о,ХвСщЅшТ»ІЅјхРЎБЛ№¦єДЎЈ ґ«ёРЖч№¤ЧчУЪН¬ІЅЖШ№вДЈКЅК±,ПсЛШ№¤ЧчК±РтИзНј3ЛщКѕЎЈResetЎўS1єНS2КЗИ«ѕЦРЕєЕ,ФЪѕ№эі¤»э·ЦК±јдTint1ЖШ№вєу,S1ВціеСЎНЁ,Ѕ«µ±З°ЦЎПсЛШХуБРЦР№вГф¶юј«№ЬPDЛщІъЙъµДРЕєЕµЪТ»ґОІЙСщµЅґжґўЅЪµг,ЛжєуReset¶ФИ«ѕЦПсЛШёґО»;ФЩѕ¶М»э·ЦК±јдTint2ЖШ№вєу,S2ВціеСЎНЁ,Ѕ«№вГф¶юј«№ЬІъЙъРЕєЕ¶юґОІЙСщµЅБнТ»ґжґўЅЪµг,Ц®єу,ёчРРµДСЎНЁРЕєЕSELТАґОЅ«ПсЛШЦРґжґўµДБЅґОІЙСщРЕєЕІо·ЦЧйєПКдИлµЅБР·ЕґуµзВ·¶Біцґ¦Ан,їЙјыФЪПсЛШј¶КµПЦБЛБЅґОЖШ№вІЙСщґжґўј°НјПсЧйєПґ¦АнЎЈФЪµ±З°ЦЎПсЛШКэѕЭ¶Біцґ¦АнµДН¬К±,їЄКј¶ФПВТ»ЦЎНјПсµДі¤»э·ЦК±јдЖШ№в,ФЪµ±З°ЦЎПсЛШДЪґжґўЖчКэѕЭНкИ«¶Біцєу,јґїЙЅшРРПВТ»ЦЎµДі¤»э·ЦК±јдІЙСщґжґў,КэѕЭµД¶БіцєНЖШ№вїЙТФН¬К±ЅшРР,Тт¶шїЙ»сµГёЯЛЩКµК±КэѕЭґ¦АнЎЈµ±И»,ґ«ёРЖчТІїЙ№¤ЧчУЪ№ц¶ЇЖШ№вДЈКЅ,ПсЛШ№¤ЧчК±РтєННј3ЛщКѕАаЛЖ,µ«ResetЎўS1єНS2І»ФЩКЗИ«ѕЦРЕєЕ,ФЪµ±З°РРКэѕЭ¶БіцµДН¬К±,їЙ¶ФПВТ»РРПсЛШЅшРРЖШ№вІЙСщІЩЧч,ТІїЙ»сµГЅПёЯЛЩ¶ИµДКµК±КэѕЭґ¦АнЎЈґЛНв,µ±БЅґОЖШ№вК±јдПаµИК±,їЙєЬИЭТЧКµПЦїЙУГУЪФЛ¶ЇМЅІвµДЦ±ЅУЦЎІо¶БіцДЈКЅЎЈ  Нј3ПсЛШј¶БЅґОЖШ№вІЙСщґжґўН¬ІЅЖШ№вК±Рт №вГф¶юј«№ЬФЪ»э·ЦЖШ№вЖЪјд·Еµз,ЖдЙПµзС№їЙ±нКѕОЄ:  ЖдЦР,ipdЎўidc·Ц±рКЗ№вГф¶юј«№ЬµД№вµзБчєН°µµзБч,CpdКЗ№вГф¶юј«№ЬµзИЭ,pd=20fF,Tint1=5ms,Tint2=64¦МsК±,єцВФ°µµзБчµДУ°Пм,Л«ІЙСщґжґўµДДЈДвЅб№ыИзНј4ЛщКѕ,НјЦРЖШ№вµДЧоґуИлЙд№вЗї1ПаУ¦УЪФј105fA№вµзБчЎЈНј4(a)ЦР,µЪТ»ґОі¤К±јд»э·ЦЖШ№в,РЕєЕКдіцЛжЧЕИлЙд№вЗї¶ИµДФцјУ¶шПЯРФФцјУ,ФЪЗї№вХХК±РЕєЕКдіцґпµЅ±ҐєНІ»ФЩФцјУ;µЪ¶юґО¶МК±јд»э·ЦЖШ№в,№вХХЅПИхК±,РЕєЕКдіцЅьЛЖОЄБг,ЛжЧЕ№вХХµДФцЗї,РЕєЕКдіц»єВэФцјУ,Зї№вХХЙд,РЕєЕКдіцФцјУПФЦш;Нј4(b)ЦР,Л«ІЙСщРЕєЕІо·ЦКдіц,УЙБЅґОЖШ№вµДРЕєЕЧйєП¶шіЙ,іЎѕ°ЅПµНХХ¶ИЗшУтЦчТЄУЙµЪТ»ґОі¤»э·ЦК±јдµДЖШ№вІЙСщѕц¶Ё,іЎѕ°ЅПёЯХХ¶ИЗшУтЦчТЄУЙµЪ¶юґО¶М»э·ЦК±јдЖШ№вІЙСщѕц¶ЁЎЈCMOSНјПсґ«ёРЖчµД¶ЇМ¬·¶О§Т»°гТААµУЪЖдїЙ·Ц±жµДЧоРЎРЕєЕј°їЙІвБїµДЧоґуРЕєЕ,ПФИ»Л«ІЙСщЧйєПКдіцА©Х№БЛґ«ёРЖчїЙІвБїµДЧоґу№вЗїРЕєЕ,ґУ¶шФцјУБЛ¶ЇМ¬·¶О§ЎЈ  Нј4 Л«ІЙСщґжґўµДДЈДв:(a)БЅґОЖШ№вІЙСщ;(b)Л«ІЙСщЧйєП БнНв,Л«ІЙСщЧйєП¶БіцІЙУГБЛІо·Ц¶БіцДЈКЅ,ФЪТ»¶ЁіМ¶ИЙПТІјхРЎБЛ°йЛжЧЕРЕєЕµД°µµзБч,ґУ¶шЅшТ»ІЅёДЙЖБЛ¶ЇМ¬·¶О§ЎЈУ¦ЧўТвµЅ,Л«ІЙСщІо·Ц¶БіцјхРЎБЛЧоґу±ҐєНРЕєЕµД·щ¶И,ІўЗТФЪTint1Ф¶ґуУЪTint2К±,ПсЛШЛ«ІЙСщІо·ЦРЕєЕКдіцЅьЛЖУЪ¶ФНјПсіЎѕ°ЅПёЯХХ¶ИЗшУтµД·щ¶ИРЕПўЧч»Т¶И·ґЧЄґ¦АнЎЈПсЛШ№¤ЧчµДSpectresДЈДвЅб№ыИзНј5ЛщКѕ,ЖдЦРPRКЗёґО»РЕєЕ,Vpd1КЗ±»ІЙСщµД№вГфРЕєЕ,їЙјыЅПєГКµПЦБЛЛ«ІЙСщґжґўЎўІо·Ц¶Біц№¦ДЬЎЈ  Нј5ПсЛШµДЛ«ІЙСщґжґўЎўІо·Ц¶Біц 4 ЅбКшУп CMOSНјПсґ«ёРµД¶ЇМ¬·¶О§¶Ф·э»сµДНјПсЦКБїУРЧЕЦШТЄТвТе,¶аґОЖШ№вјјКхКЗА©Х№¶ЇМ¬·¶О§µДУРР§·Ѕ·ЁЦ®Т»,µ«¶аУЪБЅґОµДЖШ№в,РЕєЕґ¦АнёґФУ,ґ«ёРЖчµДЦЎЖµКЬµЅПЮЦЖ,¶шПсЛШј¶Л«ІЙСщґжґўјјКхЅ«БЅґОЖШ№вІЙСщј°НјПсЧйєПґ¦АнФЪПсЛШДЪКµПЦ,ФЪА©Х№¶ЇМ¬·¶О§µД»щґЎЙП,їЙУРР§МбёЯНјПсµДКµК±ґ¦АнЛЩ¶ИЎЈѕЯУРБЅј¶»єіеµДЛ«ІЙСщґжґўµДПсЛШЅб№№,ФЪёДЙЖ¶ЇМ¬·¶О§µД»щґЎЙП,І»ЅцїЙТФ№¤ЧчУЪёЯЛЩН¬ІЅЖШ№вДЈКЅ,ТІїЙ№¤ЧчУЪ№ц¶ЇЖШ№вДЈКЅЎЈ |

НшУСЖАВЫ