СуЛљДЁбЇFPGAЃЈЪЎСљЃЉtestbenchКмживЊЃЌЧАЗТецШЋЙ§ГЬБЪМЧЃЈЯТЦЊЃЉ

ЗЂВМЪБМфЃК2016-2-19 09:09

ЗЂВМепЃКdesignapp

|

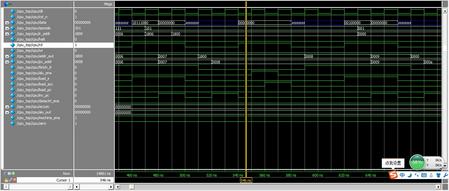

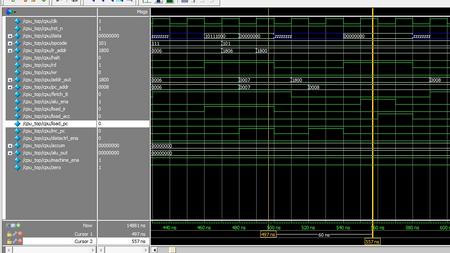

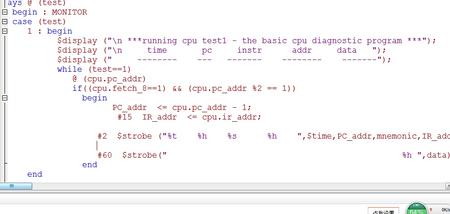

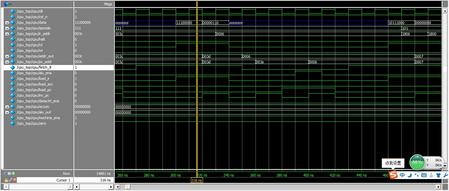

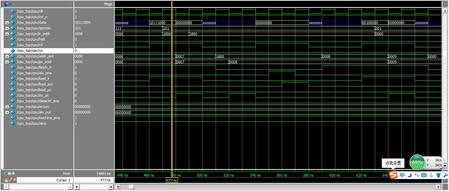

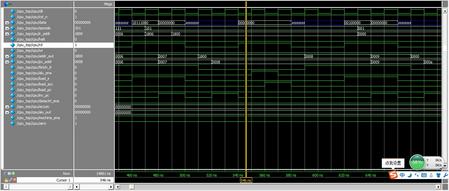

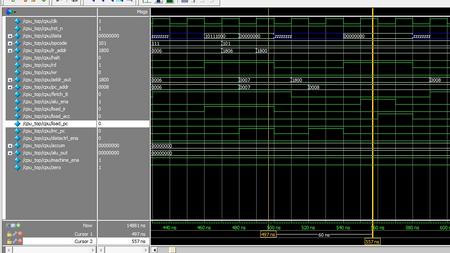

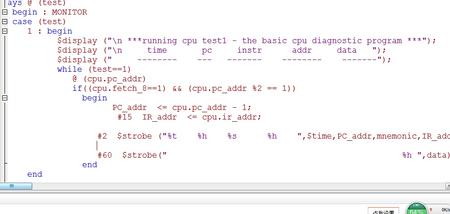

ЁЁЁЁНјШыВЈаЮЗТецКѓЕуЛїдЫааАДХЅМДПЩГіВЈаЮЃЌЯТУцЮвУЧРДбщжЄЮвУЧЕФcpuДњТыЪЧЗёе§ШЗ ЁЁЁЁДѓМвЯШПДСНИіЭМЃЌЕШЛсаЁФЋЭЌбЇЛсНсКЯетСНИіЭМИјДѓМвЯИЯИНВНтЗТецЙ§ГЬ ЁЁЁЁ  ЁЁЁЁ  ЁЁЁЁ  ЁЁЁЁЮвУЧЯШРДПДЕквЛИіЙ§ГЬ ЁЁЁЁ  ЁЁЁЁЩЯЕчКѓЃЌcpuЯШДгROMжаЖСЛиСНИіжмЦкЕФЪ§ОнЃЌЪЧДгROMЕФ0ЕижЗПЊЪМЕФЃЌдйЖдБШЮвУЧжЎЧАЖЈвхКУЕФROMЃЌЪ§ОнЖСШЁе§ШЗЃЌЖСЛиЕФЪ§ОнЕФЧАШ§ЮЛЪЧ111ЃЌМДжИСюТыJMPЃЌКѓ13ЮЛ003cЮЊЕижЗТыЃЌJMPжИСюЪЧНЋЖСЛиЕФЪ§ОнзїЮЊаТЕФЕижЗТыРДЖСШЁЯргІЕижЗЕФЪ§ОнЁЃФЧУДЃЌЯТвЛВНЃЌcpuгІИУЪЧДгROMЕФ003cЕижЗДІЖСЪ§ОнВХЖдЃЌдйПДвЛЯТВЈаЮ ЁЁЁЁ  ЁЁЁЁЖдБШВЈаЮКѓПЩжЊЃЌcpuе§КУЪЧДг003cДІЖСШЁЪ§ОнЃЌЖСЕНЕФЪ§ОнжИСюТыЮЛ111МДJMPЃЌЕижЗТыЮЛ0006ЃЌдйЕНROMЕФ0006ЕижЗДІПД ЁЁЁЁ  ЁЁЁЁетДЮЖСЛиЕФжИСюТыЮЛ101ЃЌМДLDAЃЌвВОЭЪЧЫЕНЋКѓ13ЮЛЕижЗТыЖдгІЕФRAMжаЕФЪ§ОнЖСЛиЃЌЫЭЕНРлМгЦїжаЃЌЯывЛЯТЃЌетЪБЕФRAMгІИУЪЧДђПЊЕФЃЌЖјЧвЫЋЯђЪфШыЪфГіПкЕФЪ§ОнзмЯпЩЯгІИУЪЧРДздRAMЕФ8ЮЛЪ§ОнЃЌгЩгкROM0006ЕижЗДІЕФЕижЗТыЮЊ1800ЪЧ13ЮЛЕФЃЌЖјRAMЕФЕижЗЪЧ9ЮЛЕФЃЌвђДЫЪЕМЪЩЯЮвУЧДгRAMжаЖСЛиЕФЪ§ОнЪЧДгRAMЕФ0ЕижЗЖСЛиЕФЃЌМДЮвУЧжЎЧАИјRAMаДКУЕФ0000_0000ЃЌдйПДвЛЯТВЈаЮ ЁЁЁЁ  ЁЁЁЁе§ШчЮвУЧЫљЯыЕФвЛбљЃЌЪ§ОнзмЯпЩЯЪЧ0000_0000ЃЌRAMЪЧДђПЊЕФЃЌЕижЗЮЊ1800 ЁЁЁЁОЭетбљЃЌЖСепПЩвдздМКдйЪдвЛЯТЃЌПДПДЮвУЧЕФcpuЪЧВЛЪЧАДееЮвУЧжЎЧАИјЫћЕФГЬађдЫааЕФЃЌдкетРяЮвОЭВЛдйИјДѓМввЛвЛНщЩмСЫ ЁЁЁЁЫфШЛВЈаЮЗТецКмжБЙлЃЌЕЋЪЧПДОУСЫОЭЛсСюШЫблЛЈчдТвЃЌгШЦфЪЧЪ§ОнКмЖрЕФЪБКђЃЌЮвУЧжЛФмПДЦфжавЛВПЗжЃЌВЛФмНВЫљгаЪ§ОнПДЭъећЃЌетЪБКђЮвУЧЕЅЕЅЪЧгУВЈаЮРДЗТецОЭдЖдЖВЛЙЛСЫЃЌЯТУцНщЩмгУЯЕЭГШЮЮёЗТецЕФЙ§ГЬ ЁЁЁЁдйЛиЕНЮвУЧЕФДњТыЃЌЛЙМЧЕУаЁФЋЭЌбЇзЂЪЭЕєСЫвЛаЉДњТыАЩЃЌЮвУЧАбФЧаЉДњТыИјМгЩЯ ЁЁЁЁЮввдЦфжавЛИіЙ§ГЬЮЊР§ ЁЁЁЁ  ЁЁЁЁМйЩшЖСЛиЕФжИСюТыЮЛ101ЃЌМДLDAЃЌШчЙћЮвдкfentch_8ЕФИпЕчЦНЦкМфЧвдкcpuЪфГіЕижЗЮЊЦцЪ§ЕФЪБКђМЧТМвЛЯТДЫЪБЕФЪБМфЁЂжИСюЁЂЕижЗЁЂФПЕФЕижЗЁЂЪ§ОнЕФЛАОЭПЩвдВЛгУПДВЈаЮЃЌШУЕчФдРДАяжњЮвУЧРДЗжЮіСЫЃЌвђДЫзїШчЯТДІРэ ЁЁЁЁ  ЁЁЁЁетРяЮвбгЪБ60nsЃЌЪЧвђЮЊЕквЛДЮМЧТМЕФЪБКђЪ§ОнзмЯпЩЯЛЙУЛгаЪ§ОнЃЌжЛгабгЪБвЛЛсВХЛсгаЪ§ОнЃЌМДЩЯУцФЧеХВЈаЮЭМгвБпФЧИљЛЦЩЋЕФЯпДІМЧТМвЛЯТЪ§ОнЃЌВЂНЋЦфЯдЪОЁЃЮвУЧвВПЩвдМгЩЯвЛЯТБъзЂЃЌРДАяжњЮвУЧЙлВь ЁЁЁЁетбљЮвУЧдйРДЗТецЕФЪБКђОЭВЛгУПДВЈаЮСЫЃЌжБНгДђПЊtranscriptвЛРИЙлВьМЧТММДПЩ ЁЁЁЁ  ЁЁЁЁетбљБуПЩвдЮЊЮвУЧЪЁЯТДѓСПЕФЗТецЪБМф ЁЁЁЁетРяаЁФЋЭЌбЇжЛзівЛИіЪТР§ЃЌЦфЪЕгаКмЖрЯИНкЛЙашвЊИїЮЛЖСепздМКЭкОђЃЌаЁФЋЭЌбЇдкзіетИіЪЕбщЕФЪБКђвВгіЕНЙ§ВЛЩйЮЪЬтЃЌЕЋЪЧЮЪЬтзмЪЧвЊНтОіЕФЃЌЯЃЭћИїЮЛЖСепВЛвЊРЯНшжњгкНЬГЬЃЌгіЕНЮЪЬташвЊздМКНтОіЃЌздМКПМТЧвЛЯТгІИУдѕУДаоИФЃЌетбљбЇЕНЕФжЊЪЖВХЪЧзюРЮЙЬЕФЁЃ ЁЁЁЁетРяаЁФЋЭЌбЇжЛзіЕквЛИіВтЪдЃЌЕкЖўЕкШ§ИіВтЪдСєИјЖСепздМКЭъГЩЃЌЮввбЩЯДЋЙ§ДњТыЃЌЯЃЭћЙуДѓЖСепЖрЬсвтМћЃЌДѓМвЙВЭЌНјВН ЁЁЁЁДПЪжДђ~аЛаЛИїЮЛДѓЩёжЇГж~ |

ЭјгбЦРТл