TMS320LF2407”κLAN91C111–Ά«Ε»κ Ϋ“‘ΧΪΆχΫ”ΩΎΒγ¬ΖΒΡ Βœ÷

ΖΔ≤Φ ±ΦδΘΚ2015-11-10 15:54

ΖΔ≤Φ’ΏΘΚdesignapp

|

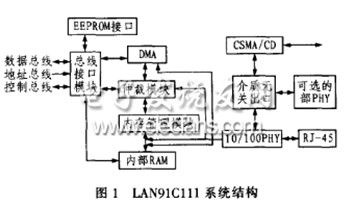

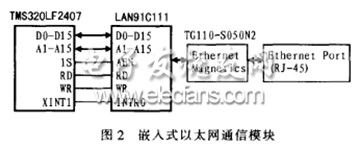

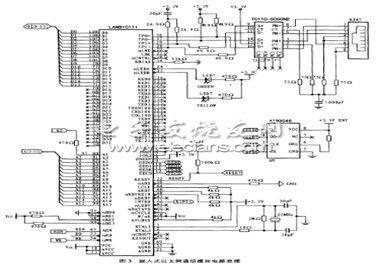

ΓΓΓΓ«Ε»κ Ϋ“‘ΧΪΆχ≤ΜΫωΩ…”Ο”ΎΙΛ“Βœ÷≥Γ Βœ÷œ÷≥ΓΫΎΒψΒΡΉ‘Ε·…œΆχΙΠΡήΘ§Εχ«“ΜΙΩ…“‘”Ο”Ύ–≈œΔΦ“ΒγΒΡ“‘ΧΪΆχΫ”ΩΎ Βœ÷‘Ε≥ΧΩΊ÷ΤΘ§ΨΏ”–ΚήΚΟΒΡΖΔ’Ι«ΑΨΑΓΘΈΡ’¬Ϋι…ήΜυ”ΎTMS320LF2407–ΆDSPΒΡ«Ε»κ ΫœΒΆ≥”κLAN91C111–ΆΉ‘ ”Π10Mb/s/100Mb/s«Ε»κ Ϋ“‘ΧΪΆχΩΊ÷ΤΒΡΫ”ΩΎΒγ¬ΖΦΑ»μ”≤Φΰ Βœ÷ΖΫΖ®ΓΘ ΓΓΓΓ1 “ΐ―‘ ΓΓΓΓΡΩ«ΑΙΊ”Ύ«Ε»κ Ϋ“‘ΧΪΆχΒΡ…ηΦΤΖΫΑΗ≤Μ «ΚήΕύΘ§Τδ÷–¥σΕύ «Μυ”ΎΒΞΤ§ΜζΒΡΘ§»±Βψ «ΥΌΕ»¬ΐΓΔ≥…±ΨΧΪΗΏΓΘDSPΉςΈΣ“Μ÷÷ΧΊ βΒΡ«Ε»κ ΫΈΔ¥ΠάμΤςœΒΆ≥Θ§ΨΏ”–«Ε»κΒΡ–≠¥ΠάμΤςΚΆ”Ο”ΎΩλΥΌ ΐΨί¥ΠάμΒΡ≤Δ–– ΐΨίΆ®ΒάΘ§‘Ύ«Ε»κ ΫΆχ¬γ…η±Η÷–“ΐ»κDSPΦΦ θΩ…“‘ Ι«Ε»κ Ϋ“‘ΧΪΆχ±δΒΟΗϋΩλΓΔΗϋ±ψ“ΥΓΔΗϋ»ί“ΉΫχ––ΙΠΡήά©≥δΓΘ±ΨΈΡΫι…ήΝΥΜυ”ΎTMS320LF2407–ΆΒΡ«Ε»κ ΫœΒΆ≥”κLAN91C111–ΆΉ‘ ”Π10Mb/s/100Mb/s«Ε»κ Ϋ“‘ΧΪΆχΩΊ÷Τ–ΨΤ§ΒΡΫ”ΩΎΒγ¬ΖΚΆ Βœ÷ΖΫΖ®ΓΘ ΓΓΓΓ  ΓΓΓΓ2 LAN91C111 ΓΓΓΓLAN91C111 «SMSCΙΪΥΨΈΣ«Ε»κ Ϋ”Π”ΟœΒΆ≥ΆΤ≥ωΒΡΒΎ»ΐ¥ζΩλΥΌ“‘ΧΪΆχΩΊ÷ΤΤςΓΘLAN91C111ΒΡ–ΨΤ§…œΦ·≥…ΝΥΉώ―≠SMSC/CD–≠“ιΒΡMAC(ΟΫΧε≤ψ)ΚΆPHY(Έοάμ≤ψ)Θ§ΖϊΚœIEEE802.3/802.U-100Base-Tx/10Base-TΙφΖΕΘ§ΤδœΒΆ≥ΫαΙΙ»γΆΦ1Υυ ΨΓΘΗΟ“‘ΧΪΆχΩΊ÷ΤΤςΒΡ÷ς“ΣΙΠΡή»γœ¬ΘΚ ΓΓΓΓΓΛΉ‘ ”ΠΒΊ―Γ¥Ϊ δΥΌ¬ Θ§÷ß≥÷10Mb/s/100Mb/s; ΓΓΓΓΓΛ≥δΖ÷÷ß≥÷»ΪΥΪΙΛΫΜΜΜ Ϋ“‘ΧΪΆχ; ΓΓΓΓΓΛ÷ß≥÷ΆΜΖΔ ΐΨί¥Ϊ δ; ΓΓΓΓΓΛ8kΉ÷ΫΎΒΡΡΎ≤Ω¥φ¥ΔΤς”ΟΉςΫ” ’ΖΔΥΆΒΡFIFOΜΚ¥φ; ΓΓΓΓΓΛ‘ω«Ω ΫΡήΝΩΙήάμΙΠΡή; ΓΓΓΓΓΛ÷ß≥÷ΉήœΏ8ΈΜΓΔ16ΈΜΓΔ32ΈΜΒΡCPUΖΟΈ ; ΓΓΓΓΓΛΧα«ΑΖΔΥΆΚΆΫ” ’ΓΘ ΓΓΓΓLAN91C111“‘ΧΪΆχΩΊ÷ΤΤςΉώ―≠IEEEΑδ≤ΦΒΡ802.3“‘ΧΪΆχ¥Ϊ δ–≠“ιΓΘΤδ8-32ΈΜ ΐΨίΉήœΏΫ”ΩΎΒΞ‘ΣΆ®ΙΐΩΊ÷ΤΉήœΏΓΔΒΊ÷ΖΉήœΏΚΆ ΐΨίΉήœΏ”κΆβ≤ΩΒΡCPUœύΝ§ΓΘΆβ≤Ω ΐΨίΩ…“‘8ΈΜΓΔ16ΈΜΜρ32ΈΜΒΡΖΫ Ϋ”κLAN91C111Ϋχ––ΫΜΜΜΓΘΗΟΒγ¬ΖΜΙΦ·≥…ΝΥEEPROMΫ”ΩΎΘ§Ή‘ΨΌ ±‘ΌΆ®ΙΐEEOROMΫ”ΩΎ δ»κΒΫ–ΨΤ§÷–Θ§¥”Εχ Βœ÷Ή‘Ε·≥θ ΦΜ·ΓΘΉήœΏ÷Ό≤ΟΤς(Arbiter)”Οά¥Φύ ”“‘ΧΪΆχΉήœΏΒΡ ΐΨίΫΜΝς«ιΩωΘ§“ΜΒ©ΖΔ…ζΉη»ϊΘ§÷Ό≤ΟΤς“ΜΖΫΟφΆ®ΙΐΉήœΏΫ”ΩΎΒΞ‘Σ”κΆβ≤ΩCPUΝΣœΒΘ§Νμ“ΜΖΫΟφΩΊ÷ΤΡΎ¥φΩΊ÷ΤΒΞ‘Σ(MMU)Θ§ Βœ÷ΉήœΏ ΐΨί–≠ΒςΓΘΡΎ¥φΩΊ÷ΤΒΞ‘ΣΩ…ΩΊ÷Τ8kBΕ·Χ§SRAMΒΡ¥φ¥Δ«ιΩωΘ§ Βœ÷”κDMAΩΊ÷ΤΤς÷°ΦδΒΡ ΐΨίΝΣ¬γΓΘDMAΩΊ÷ΤΤς”κΉήœΏΩΊ÷ΤΤς“ΜΤπΩΊ÷ΤDMA”κ“‘ΧΪΆχ–≠“ι¥ΠάμΤς(EPH)÷°ΦδΒΡ ΐΨίΫΜΜΜΓΘ“‘ΧΪΆχ–≠“ι¥ΠάμΤς(EPH)÷°ΦδΒΡ ΐΨίΫΜΜΜΓΘ“‘ΧΪΆχ–≠“ι¥ΠάμΤς≥ωά¥ΒΡ ΐΝΩΉν÷’Ψ≠Ιΐ10Mb/s/100Mb/sΒΡΈοάμ≤ψ(PHY)÷±Ϋ”ΒΫ¥ο“‘ΧΪΆχΉήœΏΓΘ ΓΓΓΓ  ΓΓΓΓ3 ”≤ΦΰΒγ¬ΖΉι≥… ΓΓΓΓ≥ω”Ύ–‘Φέ±»ΒΡΩΦ¬«Θ§―Γ”ΟDSPΩΊ÷ΤΤςΉςΈΣ÷ςCPUΓΘTMS320LF2407 «TIΙΪΥΨΖΔ≤ΦΒΡ“ΜΩνΗΏ–‘Φέ±»ΒΡΘ§ ”Ο”ΎΙΛ“ΒΩΊ÷ΤΝλ”ρΒΡDSPΓΘΗΟœΒΝ–ΨΏ”–«Ω¥σΒΡ÷ΗΝνœΒΆ≥ΓΔΫœ«ΩΒΡΝιΜν–‘ΓΔΗΏΥΌΒΡ ΐ―ߥΠάμΙΠΡήΦΑ»Ϊ–¬ΒΡΡΎ≤ΩΫαΙΙΘ§Ω…ΙψΖΚ”Ο”ΎΆ®–≈ΓΔΦΤΥψΜζΓΔ…Χ“ΒΓΔΙΛ“ΒΓΔΨϋ ¬Β»Νλ”ρΓΘTMS320LF2407 «240XœΒΝ–ΩΊ÷ΤΤς÷–ΙΠΡήΉν«ΩΒΡ“ΜΩνΘ§≤…”ΟΒΆΙΠΚΡCMOSΦΦ θΘ§ΨΏ”–30MI/sΒΡ÷¥––ΥΌ¬ Θ§Τ§…œΜΙΦ·≥…ΝΥΖαΗΜΒΡΆβΈß≤ΩΦΰ(EVMΓΔA/DΡΘΩιΓΔCANΓΔSCIΓΔSPIΦΑJTAG)ΓΘTMS320LF2407ΒΡΙΛΉςΤΒ¬ ΫœΗΏ(40MHz)Θ§¥φ÷ϋΩ’ΦδΫœ¥σ(ΗΏ¥ο32kΉ÷ΒΡFLASH≥Χ–ρ¥φ¥ΔΤςΘ§Ω…ά©’ΙΆβ≤Ω64kΉ÷¥φ¥ΔΤςΘ§64kΉ÷I/O―Α÷ΖΩ’Φδ)Θ§Ζ«≥Θ Κœ¥ΠάμΗ¥‘”ΒΡTCP/IP–≠“ιΓΘ ΓΓΓΓ”…”ΎLAN91C111 «Ή®ΈΣ«Ε»κ ΫœΒΆ≥…ηΦΤΒΡΘ§“ρ¥ΥΘ§ΤδΆβΈßΒγ¬ΖœύΕ‘±»ΫœΦρΒΞΓΘΥϋΚΆΟΜ”–DMA¥Ϊ δ–‘ΡήΒΡ16ΈΜDSP(TMS320LF2407)ΦΑTG110-S050N2–ΆΒγ¥≈ώνΚœ±δ―ΙΤςΙΙ≥…ΒΡ«Ε»κ Ϋ“‘ΧΪΆχΫαΙΙ»γΆΦ2Υυ ΨΓΘΆΦ÷–Θ§ΒΊ÷ΖΉήœΏA1-A15œύΝ§ΓΘA0ΟΜ”–±ΜLAN91C111 Ι”ΟΘ§–ϋΩ’; ΐΨίΉήœΏD0-D15œύΝ§Θ§”Ο”Ύ16ΈΜ ΐΨί¥Ϊ δΓΘLAN91C111ΕΥD16-D32–ϋΩ’;LAN91C111ΒΡΤ§―Γ–≈Κ≈AEN”…DSPΒΡΆβ≤ΩI/OΫ”ΩΎ―ΓΆ®–≈Κ≈ISΧαΙ©ΓΘΕΰΗω‘ΣΦΰΒΡΕΝΒγΤΫRDΓΔ–¥ΒγΤΫWRΖ÷±πœύΝ§ΓΘLAN91C111ΒΡ÷–Εœ δ≥ω–≈Κ≈INTROΥΆ»κDSPΒΡΆβ≤Ω÷–ΕœΫ≈XINT1¥ΞΖΔ÷–ΕœΓΘ«Ε»κ Ϋ“‘ΧΪΆχΆ®–≈ΡΘΩιΒΡΒγ¬Ζ‘≠άμ»γΆΦ3Υυ ΨΓΘ ΓΓΓΓ«Ε»κ Ϋ“‘ΧΪΆχ≤ΜΫωΩ…”Ο”ΎΙΛ“Βœ÷≥Γ Βœ÷œ÷≥ΓΫΎΒψΒΡΉ‘Ε·…œΆχΙΠΡήΘ§Εχ«“ΜΙΩ…“‘”Ο”Ύ–≈œΔΦ“ΒγΒΡ“‘ΧΪΆχΫ”ΩΎ Βœ÷‘Ε≥ΧΩΊ÷ΤΘ§ΨΏ”–ΚήΚΟΒΡΖΔ’Ι«ΑΨΑΓΘΈΡ’¬Ϋι…ήΜυ”ΎTMS320LF2407–ΆDSPΒΡ«Ε»κ ΫœΒΆ≥”κLAN91C111–ΆΉ‘ ”Π10Mb/s/100Mb/s«Ε»κ Ϋ“‘ΧΪΆχΩΊ÷ΤΒΡΫ”ΩΎΒγ¬ΖΦΑ»μ”≤Φΰ Βœ÷ΖΫΖ®ΓΘ ΓΓΓΓTX INTΘΚΒ±TX completion FIFO≤ΜΈΣΩ’ ±÷Ο1e; ΓΓΓΓTX EMPTY INT:Β±TX FIFOΈΣΩ’ ±÷Οto; ΓΓΓΓAUTO RELEASEΘΚ»γΙϊ÷ΟΈΣ1Θ§ΖΔΥΆΑϋ≥…ΙΠΚσΘ§packet number≤Μ–¥ΒΫTX completion FIFO÷–Θ§Εχ«“ΥϋΥυ Ι”ΟΒΡ¥φ¥ΔΩ’Φδ±ΜΉ‘Ε· ΆΖ≈ΓΘ ΓΓΓΓ  ΓΓΓΓ(7) Ι”ΟΓΑΟΩΖΔΥΆ“ΜΗωΑϋ≤ζ…ζ“ΜΗω÷–ΕœΓ±ΖΫΑΗ ±Θ§AUTO RELEASE=0Θ§ΗΟΖΫΑΗΒΡΝς≥Χ»γ…œΈΡΥυ ωΓΘ Ι”ΟΓΑΟΩΖΔΥΆ“ΜΗω–ρΝ–ΒΡΑϋ≤ζ…ζ“ΜΗω÷–ΕœΓ±ΖΫΑΗ ±‘ –μTX EMPTY INTΚΆTX INTΘ§AUTORELEASE=1Θ§Β±ΖΔΥΆΆξFIFO÷–ΒΡΉνΚσ“ΜΗωΑϋΚσΘ§≤ζ…ζTX EMPTY INT÷–ΕœΓΘ»τ≥ωœ÷―œ÷ΊΒΡΖΔΥΆ¥μΈσΘ§‘ρ≤ζ…ζTX INT÷–ΕœΘ§Ά§ ±ΫΪΖΔΥΆ ßΑήΒΡΑϋΒΡpacket number±Θ¥φΒΫFIFO PortsΦΡ¥φΤςΘ§’β―υDSPΨΆΩ…“‘÷ΣΒάΖΔΥΆΙΐ≥ΧΆΘ÷ΙΝΥΓΘ’β÷÷ΖΫΑΗΩ…“‘Φθ…ΌDSPΒΡΗΚΒΘΘ§Εχ«“¥φ¥ΔΩ’ΦδΒΡ ΆΖ≈“≤Ηϋ―ΗΥΌΓΘΒ±AUTO RELEASE=1 ±Θ§DSP≤ΜΡήΒΟΒΫ≥…ΙΠΖΔΥΆΑϋΒΡpacket numberΓΘ ΓΓΓΓ4.2.3 Ϋ” ’ ΐΨίΑϋΝς≥Χ ΓΓΓΓ(1)DSP…η÷Οreceive controlΦΡ¥φΤς÷–ΒΡRXENΈΜΘ§‘ –μΫ” ’ΑϋΓΘ ΓΓΓΓ(2)Κ§”–’ΐ»ΖΒΊ÷ΖΒΡΑϋ±ΜΫ” ’ΒΫΘ§¥”MMU«κ«σ¥φ¥ΔΩ’ΦδΘ§≤ΔΖ÷≈…“ΜΗωpacket numberΘ§ΡΎ≤ΩΒΡDMA¬ΏΦ≠≤ζ…ζΝ§–χΒΡΒΊ÷ΖΘ§≤ΔΫΪΫ” ’ΒΫΒΡΉ÷–¥ΒΫmemory÷–Θ§»γΙϊ≥§ΫγΘ§Αϋ±ΜΕΣΤζΘ§¥φ¥ΔΩ’Φδ±Μ ΆΖ≈ΓΘΒ±Φλ≤βΒΫΑϋΒΡΫα χΘ§Status Word±Μ–¥ΒΫΫ” ’ΑϋΒΡΉν«ΑΟφΘ§byte count–¥ΒΫΒΎΕΰΗωΉ÷ΓΘ»γΙϊCRC–Θ―ι’ΐ»ΖΘ§packet number±Μ–¥ΒΫRX FIFOΘ§”…”ΎRX FIFOΖ«Ω’ ±Θ§“ρ¥ΥΫΪ≤ζ…ζRCV INT÷–Εœ;»γΙϊRCR–Θ―ι≤Μ’ΐ»ΖΘ§‘ρ¥φ¥ΔΩ’Φδ±Μ ΆΖ≈Θ§Εχ«“≤Μ≤ζ…ζ÷–ΕœΓΘ ΓΓΓΓ(3)DSPΫ” ’ΒΫ÷–ΕœΚσΩΣ Φ÷¥––÷–Εœ¥Πάμ≥Χ–ρΘ§ Ήœ»ΕΝ»κInterrupt StatusΦΡ¥φΤςΘ§»γΙϊ≤ζ…ζΫ” ’÷–Εœ(RCV INTΈΜΈΣ1)Θ§‘ρΩ…¥”FIFO portsΦΡ¥φΤςΒΟΒΫΫ” ’ΑϋΒΡpacket numberΘ§Εχ«“Ω…¥”data registerΫΪΫ” ’Αϋ¥ΪΥΆΒΫDSPΒΡΡΎ¥φΜρΆβ¥φ÷–ΓΘΒ±¥ΠάμΫα χΘ§DSPœρ¥ΠάμΤςΖΔΥΆREMOVE AND RELEASE FROM TOP OF RXΟϋΝν(Φ¥…η÷ΟΦΡ¥φΤςMMUCOMΈΣ0x0060)“‘ ΆΖ≈ Ι”ΟΒΡ¥φ¥ΔΩ’ΦδΚΆpacket numberΓΘ ΓΓΓΓ5 Ϋα χ”ο ΓΓΓΓΗΟœΒΆ≥ΡήΙΜ’ΐ»ΖΒΊΫ”»κΩλΥΌ“‘ΧΪΆχΘ§ΨΏ±Η100/10Mbit/sΓΔ»ΪΥΪΙΛ/ΑκΥΪΙΛΉ‘ ”ΠΒ»Εύ÷÷ΙΠΡήΘ§ΖϊΚœIEEE802.3/802.3ΠΧ-100Base-TX/1Obase-TΙφΖΕΘ§Τδ«Ε»κ Ϋ“‘ΧΪΆχΫ”ΩΎ÷ß≥÷RJ45ΚΆ“‘ΧΪΆχΒΡΝ§Ϋ”Θ§Ω…“‘Ά®Ιΐ“‘ΧΪΆχΫ”»κInternetΘ§¥”Εχ Βœ÷¥”Internet…œΦύΩΊ«Ε»κ Ϋ…η±ΗΓΘ |

Άχ”―Τά¬έ