迄今最强大的实时网络交换处理器设计案例分享

发布时间:2015-10-27 11:02

发布者:designapp

|

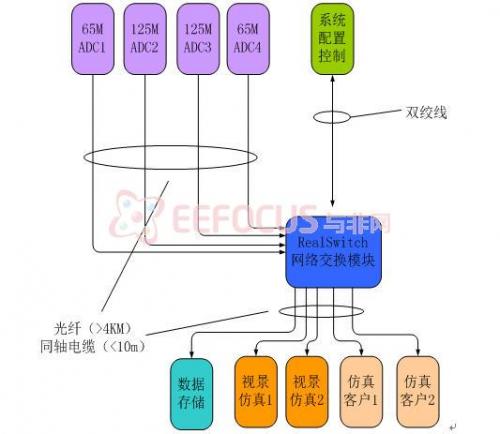

项目背景及可行性分析 项目名称、项目的主要内容及目前的进展情况 项目名称:实时网络交换处理器 项目内容:基于Xilinx高端FPGA构建实时网络交换处理器,实现数据的高速实时采集、交换、存储以及实时处理,填补国内在实时测控设备方面的空白。 目前的进展情况:系统框架构建阶段部分子系统已经实现。 项目关键技术及创新点的论述 关键技术:实时测控技术一直是航空、航天、核工业、汽车工业领域的重要支撑技术,目前国内在实时测控领域采用的设备一直依赖于国外进口设备,价格昂贵,现有的1000M以太网因网络的传输延迟抖动不确定,不具备实时性,不能应用于该领域。本项目以由高端FPGA构建的网络交换处理器为中心,集高速数据采集、交换、处理、存储以及实时显示为一体,提供完整的实时测控平台,能够完全替代国外昂贵的高速采集、实时传输、实时存储设备。 创新点:随着工业设备的日益复杂,设备的测控系统结构庞大,地理分布越加分散,如何实现数据的高速采集、实时传输是测控系统面临的巨大挑战。为了实现数据的高速采集,ADI等国外企业推出高性能仿真机,现有高端仿真机能够实现128路高到65MSPS的高速并行采集;为实现数据的高速传输与交换,GE等公司推出广播内存等实时传输设备。国外众多高速采集、实时传输设备存在的缺点主要包括:1)成本高,采用现有国外设备构建一套高速采集、实时传输系统,其成本一般在100万左右;2)接口不统一,现有高速数据采集系统与传输系统之间没有统一的接口标准,采集系统与传输系统之间需要通过PC完成数据中转,极大降低了设备的性能。本项目提出以实时网络交换处理器为中心,集数据的高速采集、实时传输为一体的测控平台,该平台以现有FPGA设备为基础,以同轴电缆或者光纤为通信介质,完成数据的高速采集与实时传输。该平台整体成本低于现有平台的10%,能够以逻辑星形结构、逻辑环形结构等多种拓扑方式实现实时通信,系统在灵活性与可靠性方面高于现有设备组成的系统。 技术成熟性和可靠性论述: 1.在数据采集方面,目前ADC的采样速率能够达到2GSPS,ADI、TI等公司等推出众多65MSPS~200MSPS的AD转换器,在ADC的接口逻辑设计以及PCB布线设计都有丰富的设计手册;本小组成员在高速ADC接口逻辑设计方面经验比较丰富,能够完成数据采集部分的设计、测试。 2.在数据传输方面,在具有16位宽度的收发器中,实现1.0Gbps的传输速率,假设采用8B10B编码方式,则FPGA需要具有在125M的工作频率,现有的FPGA工作频率远高于此频率;系统采用同轴电缆能够实现10米内的低误码率传输;采用GBIC与单模光纤,能够实现20Km以上的传输距离;项目小组成员曾参与国内知名企业核心路由器的研究,在高速逻辑设计与布线设计方面经验丰富。 项目实施方案 1.方案基本功能框图及描述  图1 实时网络交换处理器功能模块框图 系统以RealSwitch交换模块为核心,包括数据采集子系统、数据消费子系统、系统总体控制子系统与数据存储系统构成。RealSwitch交换模块由virtexⅡpro构造,最多可支持64个数据采集子系统与64个数据消费子系统,交换模块基板支持8个设备,扩展接口以堆叠方式扩展基板;数据采集子系统由多个65MSPS~125MSPS数据采集器采集数据,由SpartanII FPGA完成数据压缩与传输协议控制,由TI的1.25Gbps收发器完成数据的并-串转换,高速串行数据通过GBIC-光纤或者双绞线传输;数据消费系统完成高速数据的串-并转换以及协议控制,采用Xilinx SpartanII FPGA实现,部分仿真客户端需要模拟信号,数据消费系统完成相应的数-模转换;系统总体控制子系统完成交换系统的参数配置、数据源设置、网络交换方式配置等,系统总体控制子系统以标准Ethnet通信与网络交换模块通信;数据存储系统由4个SATA接口硬盘构成RAID系统,完成数据的可靠高速存储,由Xilinx FPGA实现。 2.需要的开发平台 实现本方案所需要的基本功能、功能、接口: DDR-RAM或者高速SDRAM,Flash存储; PowerPC处理器核,标准Ethnet接口,在网络交换模块中实现与外部主机的通信,完成系统总体控制; 网络交换模块要求FPGA主频至少125MHz; 数据存储子系统支持4个SATA接口高速硬盘; (3) 所需要的目标FPGA开发平台,简述为什么需要此平台 网络交换模块宜采用Virtex II Pro开发平台,原因如下:项目中网络交换模块具有逻辑功能要求复杂、系统处理速度要求高等特点,而Virtex-II Pro XC2VP30含有3万个Logic cells,因此能够胜任本设计;板上FPGA内含有PowerPC硬核以及Ethnet接口,方便系统总体控制子系统实现。 需要的开发工具包括Xilinx ISE、ModelSim等。 2.方案实施过程中需要开发的模块 如图1本方案中需要研制、开发的功能主要模块如下: RealSwitch网络交换子系统; 高速数据采集子系统; 仿真客户端接口子系统; 系统总体控制子系统; 数据存储子系统; 系统最终要达到的性能指标 系统吞吐量:1.25G; 系统ADC速率: 65MSPS~125MSPS; 系统传输延迟抖动:<1us; 交换接口数:128 需要的其它资源 1.设计输入输出功能子板 目前已经完成了高速数据采集系统以及仿真客户端子系统的设计,能够实现点对点高速数据的采集与传输; 需要近一步完成数据存储子系统、网络交换处理器系统以及系统总体控制子系统模块。 2.测试设备 目前开发小组借助西安交通大学电信学院网络所的资源优势,拥有泰科500M数字存储示波器2台、逻辑分析仪1台,以及其他直流稳压电源、万用表等设备。 |

网友评论