ЛљгкS3C4480XЕФДѓаЭLEDЯдЪОЯЕЭГЩшМЦ

ЗЂВМЪБМфЃК2010-7-12 13:58

ЗЂВМепЃКzealot

|

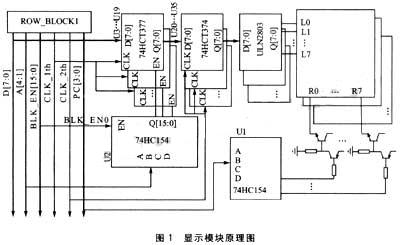

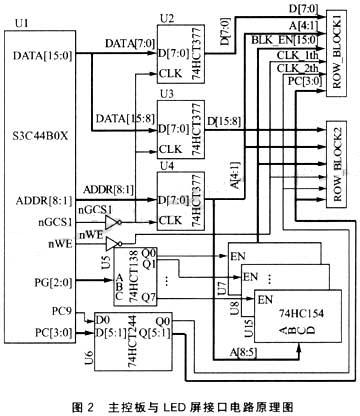

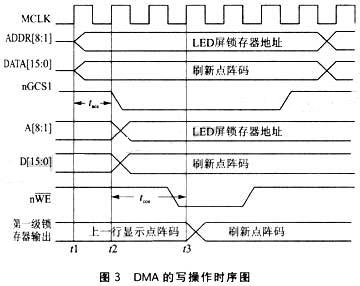

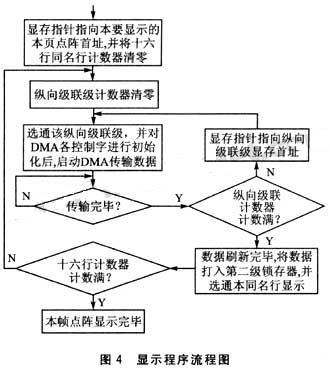

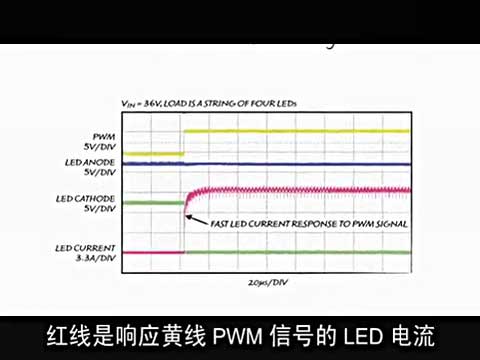

ДѓаЭLEDЯдЪОЯЕЭГвбОЙуЗКгІгУгкИїжжЪвФкЭтГЁКЯЃЌЕЋгЩгкЦфЖрВЩгУЖрЛњЯЕЭГЃЌЬсИпСЫЯЕЭГГЩБОКЭШэгВМўЩшМЦИДдгЖШЁЃЖрЛњЯЕЭГЙЄзїЪБЃЌБОжЪЩЯЯрЕБгквЛИіИпзмЯпПэЖШЕФМЦЫуЛњЯЕЭГЁЃЦфММЪѕФбЕуШчЯТЃК ДѓаЭLEDЯдЪОЦСЩЯЕФЯёЫиЪ§вдЭђМЦЃЌЫцзХЯдЪОУцЛ§діДѓЃЌЕчТЗНсЙЙЫцжЎдіДѓЁЃ ЮЊСЫБЃжЄвЛЖЈЕФЯдЪОжЪСПЃЌжЁЦЕгІдк30жЁЃЏsвдЩЯЁЃЖдгквЛИі512ЁС252ЕФЕЅЩЋLEDЦСЃЌУПУыЕФЪ§ОнДЋЪфСПжСЩйЮЊ480 KBвдЩЯЃЌЖдгкВЪЦСМАЯдЪОжЪСПИпЕФГЁКЯЃЌЪ§ОнДЋЪфСПЛЙНЋАДећЪ§БЖдіГЄЁЃ ЕБLEDЦСЮЛгкЪвЭтЪБЃЌЩЯЯТЮЛЛњЭЈаХПЩФмдкАйУзЩѕжСЧЇУзвдЩЯЃЌвЊЧѓЭЈаХЫйЖШПьЧвПЩППЁЃ МјгкЩЯЪіЧАСНИіММЪѕФбЕуЃЌЮЊФмЙЛЪЙгУЕЅCPUЯЕЭГДњЬцЖрЛњЯЕЭГПижЦДѓаЭLEDЯдЪОЯЕЭГЃЌВЩШЁЕФгІЖдВпТдШчЯТЃК ДѓаЭЕФlEDЦСгЩЭЈгУЕФЯдЪОФЃПщзщГЩЃЌЯдЪОФЃПщОпгаСМКУЕФЭЈгУадКЭПЩЧЖШыадЁЃ ЪЙгУ16ЮЛВЂаазмЯпЪ§ОнДЋЪфЗНЪНЃЌвЊЯдЪОЯргІЮЛжУЕФЯдЪОФЃПщЃЌФЃПщЩЯЕФСаЫјДцЕЅдЊФмЙЛзМШЗбЁЭЈЃЌЪЙКсЯђМЖСЊЕФLEDЯдЪОФЃПщФмЙЛБЛЪгЮЊвЛЖЮСЌајЕФДцДЂЕЅдЊЁЃ ЪЙгУS3C44BOXФкВПЕФDMAПижЦЦїНјааЪ§ОнЕФДЋЪфКЭПижЦЃЌНкЪЁСЫЪЙгУжИСюДЋЪфЪ§ОнЕФCPUШЁжИКЭвыжИЪБМфвдМАЪЙгУжИСюДЋЪфЪ§ОнИНДјЕФМЦЪ§ЁЂБШНЯЁЂЬјзЊЕШШэМўПЊЯњЃЌДгЖјФмЙЛдкСЌајЕФЖСаДВйзїжаЭъГЩЪ§ОнЕФДЋЪфЃЌЬсИпСЫЪ§ОнДЋЪфЕФЫйЖШКЭаЇТЪЁЃ 1 гВМўНсЙЙМАдРэ ДѓаЭLEDЯдЪОЯЕЭГвЛАуЗжЮЊжїПиАхКЭЯдЪОЧ§ЖЏФЃПщСНВПЗжЁЃ 1ЃЎ1 ЯдЪОФЃПщ ЯжНёЃЌДѓаЭLEDЯдЪОЯЕЭГЪЧРћгУШЫблЪгОѕЬиЕуВЩгУж№ааЩЈУшКЭСаЧ§ЖЏЗНЪНвдНкЪЁгВМўПЊжЇЕФЃЌБОЯЕЭГВЩгУ1ЃЏ16ж№ааЩЈУшЗНЪНЃЌЫљвдећИіДѓаЭLEDЦСБЛЗжЮЊ16ааЭЌУћааЃЌЯдЪОФЃПщдРэЭМШчЭМ1ЫљЪОЁЃ  УПИіЯдЪОФЃПщЮЊ1Иі64ЁС32ЕФаЁЕуеѓЦСЃЌЗжЮЊСНВПЗжЃЌЩЯЯТИї16ааЃЌУПВПЗжга8зщСаЪ§ОнЫјДцЦїЁЃЩЯЯТСНВПЗжИДгУ1Иі4ЁЊ16выТыЦїU1ЃЌбЁЭЈЧ§ЖЏ1ЃЏ16ж№ааЩЈУшЯдЪОЃЌВЂашвЊ16зщСаЧ§ЖЏЫјДцЦїЫјДцСаЯдЪОЪ§ОнЁЃВЩгУВЂаазмЯпЪ§ОнДЋЪфЗНЪНЪБЃЌашвЊ1Иі4ЁЊ16выТыЦїU2бЁЭЈЪЙФмСаЫјДцЦїЁЃдкЕуеѓЫЂаТЪБЃЌашвЊЪЙгУСНМЖЫјДцЦїЫјДцСаЯдЪОЪ§ОнЃЌЗёдђЛсГіЯжЯдЪОЭЯЮВЯжЯѓЁЃБОДЮе§дкЯдЪОЕФЪ§ОнДцдкЕкЖўМЖЫјДцЦїжаЃЌжїПиАхЖдЦСЖЫЕквЛМЖЫјДцЦїаДЯТвЛаавЊЯдЪОЕФЪ§ОнНјааСаЪ§ОнЫЂаТЃЌЕБЯТвЛаавЊЯдЪОЕФЪ§ОнДЋЪфЭъБЯКѓЃЌвЛЦ№ЫјДцЕНЕкЖўМЖЫјДцЦїЪфГіВЂбЁЭЈЧ§ЖЏЯТвЛааЯдЪОЁЃВЩгУВЂаазмЯпЗНЪНЯТЖўМЖЫјДцЦїШдБШЪ§ОнДЎааДЋЪфдйзЊГЩВЂааЪфГіЕФЗНАИОМУЁЃ ЯдЪОФЃПщгыФЃПщжЎМфКсЯђМЖСЊЪБЃЌдЫгУДэЮЛМЖСЊЕФЫМЯыЃЌЪЙЦфОпгаСМКУЕФЭЈгУадКЭПЩЧЖШыадЁЃШчЭМ1ЫљЪОЃЌбЁЭЈЯпУПЕНвЛМЖЪБОЭЛсДэЮЛвЛДЮВЂДЋЕНЯТвЛМЖЃЌзмЪЧЪЙЕквЛИљбЁЭЈЯпBLK_EN0зїЕквЛМЖСаЫјДцЦївыТыЦїЕФЪЙФмПижЦЯпЃЌетбљnИљбЁЭЈЯпОЭФмвРДЮбЁЭЈnМЖКсЯђМЖСЊФЃПщЁЃетбљОЭПЩвдгУЯрЭЌЕФЯдЪОФЃПщШЮвтзщКЯГЩКсЯђМЖСЊЕФЬѕЦСЁЃ дЫгУДэЮЛМЖСЊЫМЯыЃЌЪЙКсЯђМЖСЊЕФЯдЪОФЃПщЩЯЕФЕквЛМЖЫјДцЦїЕФвыТыЦїU2ФмЙЛвРДЮбЁЭЈЃЌИУвыТыЦїгжФмвРДЮбЁЭЈЕквЛМЖСаЪ§ОнЫјДцЦїЃЌетбљКсЯђМЖСЊЦСЩЯЕФЕквЛМЖСаЪ§ОнЫјДцЦїОЭФмПДГЩвЛЖЮСЌајЕФДцДЂЕЅдЊЃЌетЪЧЪЙгУDMAВЂааЪ§ОнДЋЪфПижЦЕФЛљДЁЁЃ 1ЃЎ2 жїПиЕчТЗгыLEDЦСЕФНгПкЩшМЦ БОЯдЪОЯЕЭГбЁгУЛљгкARM7TDMIФкКЫВЂДјгаФкВПDMAПижЦЦїЕФS3C44BOXзїжїПижЦЦїЃЌЪЙЦфЙЄзїдкARMзДЬЌЃЌВЂЪЙгУ16ЮЛзмЯпЁЃгЩгкАбLEDЦСащФтЕФЪгЮЊвЛЖЮСЌајЕФДцДЂЕЅдЊЃЌЙЪЮЊЦфЗжХфЕижЗПеМф0x2000000ЁЋOx4000000ЁЃ жїПиЕчТЗгыLEDЦСНгПкгІФмЪЕЯжвдЯТЙІФмЃК бЁЭЈШЮвтЮЛжУЕФЯдЪОФЃПщМАИУФЃПщЩЯЕФЕквЛМЖСаЪ§ОнЫјДцЦїЁЃНЋИУЮЛжУвЊЯдЪОЕФЕуеѓТызМШЗЫјДцЃЌВЂФмдкЕквЛМЖСаЪ§ОнЫјДцЦїЪ§ОнЫЂаТКѓЃЌНЋЫЂаТЪ§ОнЫјДцЕНЕкЖўМЖСаЪ§ОнЫјДцЦїВЂЪфГіЁЃ ФмПижЦбЁЭЈЧ§ЖЏ16ааЭЌУћаажаЕФвЛааНјааж№ааЩЈУшЯдЪОЁЃ ЪЕЯжжїПиаОЦЌ3ЃЎ3 VЕНLEDЦС5VЕФТпМЕчЦНзЊЛЛЁЃ жїПиАхгыLEDЦСНгПкЕчТЗдРэЭМШчЭМ2ЫљЪОЁЃ  вЛИіДѓаЭLEDЦСЕФНсЙЙПЩЗжЮЊзнЯђМЖСЊКЭКсЯђМЖСЊЃЌетжжНсЙЙРрЫЦгквЛИіШ§ЮЌЪ§зщЁЃМйЩшвЛИіШ§ЮЌЪ§зщLED[j][k]ЃЌЦфжаЃК i=0ЃЌ1ЃЌ2,ЁЃЌm БэЪОLEDЦСзнЯђМЖСЊМЖЕФађКХЁЃ j=0ЃЌ1ЃЌ2,ЁЃЌn БэЪОLEDЦСКсЯђМЖСЊМЖЕФађКХЁЃ k=OЃЌ1ЃЌ2,ЁЃЌ16 БэЪОЯдЪОФЃПщЩЯ16ИіЕквЛМЖСаЪ§ОнЫјДцЦїЕФађКХЁЃ гЩгкЯЕЭГЪЙгУ16ЮЛВЂаазмЯпЪ§ОнДЋЪфЗНЪНЃЌВЂНЋLEDЦСЪгЮЊвЛЖЮСЌајЕФДцДЂЕЅдЊЃЌЙЪЪЙгУA[4ЃК1]зїЯдЪОФЃПщЩЯбЁЭЈЕквЛМЖСаЪ§ОнЫјДцЦївыТыЦї(ЭМ1жаU2)ЕФвыТыЪфШыЃЌМДЮЊШ§ЮЌЪ§зщЕФkБфСПЃЛЪЙгУA[8ЃК5]зїбЁЭЈКсЯђМЖСЊЯдЪОФЃПщЕФвыТыЦї(ЭМ2жаU7)выТыЪфШыЃЌМДЮЊШ§ЮЌЪ§зщЕФjБфСПЃЛгЩгкLEDЦСвЊОпгаСМКУЕФСщЛюадЃЌгжгЩгкВЩгУDMAДЋЪфЪ§ОнвЊЧѓЕуеѓТыДцЗХЫГађЕФММЪѕвЊЧѓЃЌзнЯђМЖСЊМЖбЁЭЈВЛТњзуЪЙгУЕижЗзмЯпвыТыбЁЭЈЕФЬѕМўЃЌЫљвдЪЙгУS3C44BOXЕФPG[2ЃК0]зїзнЯђМЖСЊМЖбЁЭЈвыТыЦїЕФвыТыЪфШыЃЌМДШ§ЮЌЪ§зщЕФiБфСПЁЃ гЩгкЕижЗКЭЪ§ОнзмЯпЩЯЕФзДЬЌВЛЖЯБфЛЏЃЌЫљвддкЖдLEDЦСНјаааДВйзїЪБЃЌЕижЗКЭЪ§ОнаХКХгІНјааЫјДцЃЌжїПиАхЩЯЗжБ№ЪЙгУU2ЁЂU3КЭU4ЫјДцЖдLEDаДВйзїЪБЕФЕижЗКЭЪ§ОнзмЯпЕФзДЬЌЁЃLEDЦСЗжХфЪзжЗЮЊOx2000000ЃЌЕБЖдЦфНјаааДВйзїЪБЃЌS3C44BOXЕФnGCSlКЭnWEНХЛсГіЯжПЩБрГЬПижЦЪБбгЕФгааЇЕЭЕчЦНЁЃnGCSlОвЛИіЗЧУХзїU2ЁЂU3КЭU4ЕФЫјДцЪЙФмПижЦаХКХЃЌБЃжЄНідкЖдLEDЦСЗУЮЪЪБЃЌЕижЗКЭЪ§ОнзмЯпЩЯЕФаХКХВХБЛЫјДцЁЃnWEОвЛИіЗЧУХзїЦСЖЫЕквЛМЖСаЪ§ОнЫјДцЦї(ЭМ1жаU3ЁЋU19)ЕФЫјДцЪЙФмПижЦаХКХЃЌБЃжЄжЛгаЕБЫЂаТЪ§ОнЮШЖЈГіЯждкСаЪ§ОнЫјДцЦфЪфШыЖЫЪБВХБЛЫјДцЁЃS3C44BOXЕФPCI0зїЫљгаЦСЖЫЕкЖўМЖЫјДцЦї(ЭМ1жаU20ЁЋU35)ЕФЫјДцЪЙФмПижЦаХКХЯпЃЛS3C44BOXЕФPC[3ЃКO]зї16ааЧ§ЖЏвыТыЦї(ЭМ1жаU1)ЕФвыТыЪфШыЁЃгЩгкЪ§ОнДЋЪфЪБжЛашвЊжїПиАхЖдLEDЦСЪфГіПижЦЃЌВЛашвЊаХКХЗДРЁЃЌЫљвдНгПкЕчТЗВЩгУСЎМлЕФ5VЙЉЕчЕФHCTЕчТЗаОЦЌЗНАИЃЌОЭПЩТњзужїПиаОЦЌ3.3VЕНLEDЦС5VЕФТпМЕчЦНзЊЛЛЁЃ дкDMAДЋЪфЪ§ОнЪБЃЌИќЙиаФЕФЪЧDMAЕФаДВйзїЃЌЪБађШчЭМ3ЫљЪОЁЃt1ЪБПЬDMAаДВйзїПЊЪМЃЌЕижЗКЭЪ§ОнзмЯпЩЯГіЯжLEDЦСЯргІЮЛжУЕФЕижЗКЭЫЂаТЪ§ОнЃЛt2ЪБПЬnGCS1в§НХГіЯжгааЇЕЭЕчЦНЃЌЕижЗКЭЪ§ОнзмЯпЩЯЕФЪ§ОнБЛЫјДцЕНU2ЁЋU4ВЂЪфГіЃЛt3ЪБПЬnWEв§НХГіЯжгааЇЕЭЕчЦНЃЌU2ЁЋU4ЕФЪфГіЪ§ОнБЛЫјДцЕНЦСЖЫЕквЛМЖСаЪ§ОнЫјДцЦїВЂЪфГіЁЃетбљжїПижЦЦїОЭЭъГЩСЫвЛДЮСаЪ§ОнЕФЫЂаТЁЃ  2 ШэМўЩшМЦ 2ЃЎ1 LEDЦСЯдЪОГЬађЩшМЦ гЩгкЪЙгУСЫS3C4480XФкВПDMAПижЦЦїНјааЪ§ОнЕФДЋЪфгыПижЦЃЌЯдЪОГЬађЕУЕНКмДѓМђЛЏЃЌГЬађСїГЬШчЭМ4ЫљЪОЁЃЕуеѓТыЕФДЋЪфШЋгЩDMAПижЦЦїЭъГЩЃЌжЛашдкЦєЖЏDMAЪ§ОнДЋЪфЧАНЋЕуеѓТыЕФЪзжЗЁЂLEDЦСЕФЪзжЗМАДЋЪфЪ§ОнСПЕФжЕЗжБ№ИГИјЯргІЕФПижЦзжКѓЃЌЦєЖЏDMAВйзїМДПЩЁЃЭъГЩЫљгаБОЭЌУћааЕуеѓТыДЋЪфКѓЃЌНЋЫЂаТЕФЪ§ОнЫјДцЕНЕкЖўМЖСаЪ§ОнЫјДцЦїЪфГіЃЌВЂЧ§ЖЏБОЭЌУћааЯдЪОЁЃетбљбЛЗЯдЪО16ааЭЌУћааКѓОЭЭъГЩСЫвЛжЁЕуеѓЯдЪОЁЃ  2ЃЎ2 ЕуеѓХХађ гЩгкLEDЯдЪОФЃПщЕФЕчТЗНсЙЙвдМАЪЙгУСЫ16ЮЛВЂаазмЯпКЭDMAЪ§ОнДЋЪфММЪѕЃЌдкЯдЪОЪБЕуеѓТыЕФХХЗХЫГађЃЌашвЊТњзуШчЯТвЊЧѓЃК Ђй16ЮЛВЂаазмЯпвЛДЮЪ§ОнДЋЪфЃЌМДвЛДЮDMAаДВйзїДЋЪфСНИізжНкЕФЕуеѓТыЃЌЕЭЮЛКЭИпЮЛзжНкЗжБ№ДЋЫЭЕНСНЯрСкЕФзнЯђМЖСЊФЃПщЕФЭЌУћааКЭЭЌУћСаЪ§ОнЫјДцЦїжаЃЌвђДЫЯрСкЕФзнЯђМЖСЊФЃПщЕФЭЌУћааКЭЭЌУћСаЕуеѓТыгІСЌајДцЗХЁЃ ЂкгЩгкЯдЪОФЃПщЕФЕквЛМЖСаЪ§ОнЫјДцЦївыТыбЁЭЈЕчТЗНсЙЙКЭDMAЪ§ОнДЋЪфвЊЧѓЃЌЖдЭЌвЛЯдЪОФЃПщЕФЩЯЯТСНВПЗжЕФЭЌУћааЕуеѓгІАДСаЪ§ОнЫјДцЦїЕФбЁЭЈЫГађвРДЮСЌајДцЗХЁЃ ЂлСНЯрСкЕФзнЯђМЖСЊМЖЕФвЛЯЕСаКсЯђМЖСЊМЖгІАДЂйКЭЂкддђНјааЕуеѓТыХХађЁЃ ЂмИїзнЯђМЖСЊМЖвРДЮАДЂйЁЂЂкЁЂЂлддђНјааЕуеѓТыХХађЁЃ Ђн16ааЩЈУшЯдЪОЗНЪНЯТЃЌвЛИіДѓаЭLEDЦСЗжЮЊ16ааЭЌУћааЃЌУПвЛЭЌУћааАДееЂйЁЂЂкЁЂЂлЁЂЂмддђНјааЕуеѓХХађЁЃ вдвЛИі128ЁС64ЕФЕуеѓЦСЕквЛааЭЌУћааЕФЪ§ОнХХађЮЊР§ЃЌШчЭМ5ЫљЪОЃЌЕквЛааЭЌУћааЕФЕуеѓТыЕФДцЗХЫГађгІвРДЮЮЊЃКaЃЌbЁЁzЃЌAЃЌBЃЌЁЁzЁЁЁЃ  3 Нс Тл ЪЙгУВЂаазмЯпDMAЪ§ОнДЋЪфММЪѕМђЛЏСЫLEDЯдЪОЯЕЭГЕФШэгВМўЩшМЦЃЌНЕЕЭСЫЯЕЭГГЩБОЃЌШЁЕУСЫКмКУЕФЯдЪОжЪСПЃЌдк22.1184MHzЕФЯЕЭГЪБжгЯТЃЌ512ЁС256(8m2)ЕЅЩЋЕуеѓЦСЯдЪОжЁЦЕДяЕН250HzЃЌЦНОљ120nsДЋЫЭ1ИізжНкЃЌДяЕНСЫЪЙгУЕЅCPUЯЕЭГДњЬцЖрЛњЯЕЭГПижЦLEDЯдЪОЯЕЭГЕФФПЕФЁЃЕЋЮЊСЫЪЙЩЯвЛДњЕФЯдЪОЧ§ЖЏАхШдФмЙЛЪЙгУЃЌЕуеѓТыашвЊХХађЃЌЯдЪОЪБжЛФмЪЙгУвГУцЗНЪНЯдЪОЃЌетбљдкЖрвГЖЏЬЌЙіЦСЯдЪОЪБашвЊДѓШнСПЕФДцДЂЦїЁЃЖдгк512ЁС256ЕЅЩЋЕуеѓЦСашвЊЪ§ЪЎезЕФШнСПЃЌЪЙгУ32ЮЛARM7TDMlФкКЫЯШНјПижЦЦїS3C44BOXКЭСЎМлЕФДѓШнСПSDRAMДцДЂЦїПЩвдЪЙИУЮЪЬтЕУЕНКмКУЕФНтОіЁЃШєЪЙгУеыЖдDMAПижЦЯдЪОЩшМЦЕФЯдЪОЧ§ЖЏАхЯдЪОЪБЃЌЕуеѓТыОЭВЛашвЊХХађЃЌвЛЦЌЪ§АйKBЕФSRAMОЭФмТњзуЯЕЭГвЊЧѓСЫЁЃ |

ЭјгбЦРТл