ВЂПкЭЈбЖЕФЫЋТЗИпЫйПЩБрЪ§зжМАФЃФтаХКХдДЩшМЦ

ЗЂВМЪБМфЃК2010-6-28 10:07

ЗЂВМепЃКzealot

|

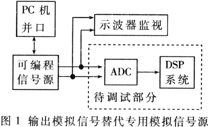

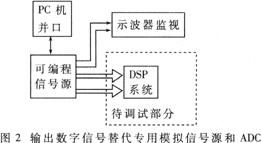

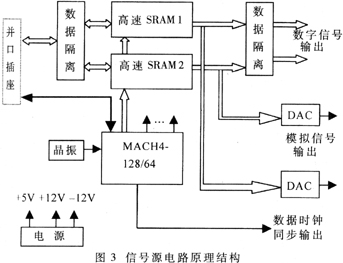

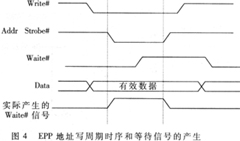

ДѓЖрЪ§DSPгІгУЯЕЭГЖМАќРЈвЛИіЧАЖЫЕФФЃ/Ъ§зЊЛЛЕчТЗ(ADC)ЁЃдкЕїЪдИпЫйЪ§зжаХКХДІРэ(DSP)ЯЕЭГЪБЃЌЭЈГЃЪЧзівЛИізЈгУЕФФЃФтаХКХдД(ШчРзДяжаЦЕФЃФтаХКХдДЕШ)ЃЌМгЩЯвЛИіЮЊЪЕМЪгІгУЬижЦЕФФЃ/зЊЛЛЕчТЗ(ADC)ЃЌвдЛёШЁгыЪЕМЪгІгУЯрЕБЕФзЈгУаХКХЪ§ОнРДЕїЪдИУDSPЯЕЭГЁЃЭЈГЃЃЌФЃФтаХКХдДЁЂADCМАDSPЯЕЭГЪЧгЩВЛЭЌЕФПЊЗЂШЫдБЩшМЦжЦзїЕФЁЃЮЊСЫЕїЪдDSPЯЕЭГЃЌашвЊИїЗНШЫдБазїЃЌЕїЪдШЮЮёЯрЕБЗБдгЁЃЧвВЛЭЌЕФDSPЯЕЭГЕїЪдашвЊВЛЭЌЕФаХКХдДКЭADCЃЌвВЪЧЯЕЭГбаЗЂНзЖЮЕФФбЕуЁЃ дкЖрДЮЕїЪдDSPЯЕЭГжЎКѓЃЌЩшМЦВЂжЦзїСЫвЛжжИпЫйЫЋТЗПЩБрГЬаХКХдДЁЃЫќЕФЪфГіОпгаЪ§зжКЭФЃФтСНжжаЮЪНЃЛаХКХЕФФкШнЁЂЪфГіЫйТЪЁЂЪ§ОнГЄЖШЕШЖМПЩвдЭЈЙ§ЃаЃУЛњВЂПкРДНјааЩшжУКЭПижЦЃЛЪ§ОнЪфГіЫйТЪПЩИпДя75Mзж/sЃЌЯргІЕФФЃФтЪфГіаХКХзюДѓЦЕТЪЮЊ37.5MHzЃЌЪ§ОнжиИДГЄЖШзюДѓЮЊ128KзжЃЛПЩЙуЗКгІгУгкИїРрDSPЯЕЭГЕФЕїЪдЁЃгЩгкИУаХКХдДдЫгУМЦЫуЛњВњЩњЫљашЕФВЈаЮЪ§ОнКЭПижЦаХЯЂЃЌвђДЫЫќвВЪєгкЭЈГЃЫљГЦЕФащФтвЧЦїЗЖГыЁЃЦфгІгУаЮЪНгаСНжжЃКЂйРћгУЪфГіЕФФЃФтаХКХЬцДњзЈгУЕФФЃФтаХКХдДЃЛЂкРћгУжБНгЪфГіЕФЪ§зжаХКХЬцДњФЃФтаХКХдДКЭADCЁЃСНжжгІгУЗжБ№ШчЭМ1КЭЭМ2ЫљЪОЁЃ   1 ПЩБрГЬаХКХдДЕчТЗдРэ ИУаХКХдДЕФЛљБОЩшМЦЫМТЗЪЧЃЌгЩМЦЫуЛњБрГЬВњЩњЫљашЕФСНТЗаХКХЪ§Он(АќРЈМгдыЪ§Он)ЁЃЭЈЙ§МЦЫуЛњВЂПк(EPPФЃЪН)НЋЪ§ОнЗжБ№ДЋЕНаХКХдДЕФСНИіИпЫйЪ§ОнЛКГхЧј?СНИі128KЁС8ЕФSRAMЁЁЃЌдкаХКХдДЕФФкВПЪБжгЭЦЖЏЯТНЋЪ§ОнИпЫйЪфГіЃЛЭЌЪБНЋЯргІЪ§ОнОЙ§СНТЗИпЫйЪ§/ФЃзЊЛЛЦї(DAC)ЕчТЗзЊЛЛГЩФЃФтаХКХЭЌВНЪфГіЁЃЦфжаЪ§ОнЪфГіЕФГЄЖШвдМАЪфГіЫйТЪЪЧПЩвдЩшжУЕФЁЃ аХКХдДЕФЫљгаТпММАЪБађЙІФмгЩвЛЦЌCPLD(MACH4-128/64)ЭъГЩЃЌАќРЈEPPФЃЪНВЂПкЕФНгПкПижЦЁЂЪ§ОнДцДЂЦїЕФЕижЗМАЖСаДаХКХВњЩњЁЂЪ§ОнЛКГхИєРыПижЦЁЂDACПижЦЁЂФкВПЪБжгПижЦЁЂЪ§ОнЪБжгЭЌВНЕФВњЩњЁЃећИіЕчТЗЕФдРэНсЙЙШчЭМ3ЫљЪОЁЃ  1.1 EPPФЃЪНВЂПкТпМЩшМЦ EPPФЃЪНЕФВЂПкI/OПеМфГ§СЫБъзМНгПк(SPP)гУЕНЕФ3ИіЖЫПквдЭтЃЌЛЙдіЩшСЫСНИіЫЋЯђЕФ8ЮЛЖЫПкЃЌМДЕижЗЖЫПкКЭЪ§ОнЖЫПкЃЌЫќУЧЗжБ№еМгУЛљЕижЗ(ЭЈГЃЮЊ378H)ЕФЦЋвЦСП3КЭ4ДІЁЃе§ЪЧетСНИіаТдіЕФЫЋЯђЖЫПкЪЙЕУВЂПкEPPФЃЪНБЛЙуЗКПЊЗЂгІгУЁЃетСНИіЖЫПкДгЪБађЩЯЪЧвЛбљЕФЃЌгЩИїздЕФбЁЭЈТіГхаХКХРДЧјЗжЁЃдкБОаХКХдДЩшМЦжаЃЌВЩгУЕижЗЖЫПкЫјДцЪ§ОнзїЮЊПижЦУќСюЃЌЪ§ОнЖЫПкгУгкДЋЫЭЪ§ОнЃЌАќРЈЪ§ОнФкШнЁЂГЄЖШКЭЪфГіЪ§ТЪбЁдёЁЃдкEPPВЂПкЭЈбЖавщжаЃЌЕижЗаДжмЦкЪБађШчЭМ4ЫљЪОЁЃ  ЮЊе§ШЗЭъГЩвЛИіEPPЕижЗЛђЪ§ОнЕФЖСаДжмЦкЃЌашвЊе§ШЗВњЩњвЛИіЕШД§аХКХ(WaiteЃЃ)ЁЃдкEPPавщЪБађЭМЩЯЃЌЫќБШЕижЗбЁЭЈаХКХвЊЭЦГйвЛаЉ(ШчЭМ4)ЁЃШчКЮВњЩњетИіЕШД§аХКХЪЧОГЃРЇЛѓЩшМЦШЫдБЕФЮЪЬтЁЃЭЈЙ§заЯИбаОПавщЙцдђЃЌЗЂЯжвЛИіе§ГЃЕФЖСаДжмЦкЪЧгЩЕШД§аХКХРДЭЦЖЏЕФЁЃБШШчЕБМЦЫуЛњЯђЕижЗЖЫПкаДЪ§ОнЪБЃЌМЦЫуЛњЕФEPPНгПкТпМЪзЯШЪЙаДаХКХгааЇЃЌШЛКѓМрЪгЕШД§аХКХЃЌШчЙћЮЊЕЭЃЌВХЪЉМгбЁЭЈаХКХ(Addr StrobeЃЃ)ЃЌжЎКѓМЬајМрЪгЕШД§аХКХЃЌШчЙћЕШД§аХКХЮЊИпБэУїжеЖЫЩшБИвбШЁЕУЪ§ОнЃЌДгЖјГЗЯћбЁЭЈаХКХВЂНсЪјаДжмЦкЁЃЪ§ОнжмЦкгыЕижЗжмЦкРрЫЦЁЃСЫНтетвЛЕужЎКѓЃЌдкЖСаДЪ§ОнЛђЕижЗЖЫПкЪБЃЌЕШД§аХКХПЩвджБНггУбЁЭЈаХКХШЁЗДРДВњЩњЃЌжЛвЊЫйЖШЩЯФмБЃжЄдкбЁЭЈаХКХНсЪјЪБПЩвде§ШЗЖСГіЛђепБЃДцЪ§ОнЃЛгЩгкДцдкЕижЗКЭЪ§ОнСНИібЁЭЈаХКХ?Addr StrobeЃЃКЭData StrobeЃЃЁЁЃЌгУЫќУЧЕФгыЗЧРДВњЩњИУЕШД§аХКХМДПЩЁЃ 1.2 ЕижЗВњЩњ БОаХКХдДЕФЕижЗВњЩњТпМЪЕМЪЩЯЪЧвЛИіЭЌВНМгМЦЪ§ЦїЃЌгУвдВњЩњЫГађМг1ЕФЕижЗЃЌжЛЪЧЫќЕФЭЌВНЪБжггаСНИіРДдДЁЃЕБМЦЫуЛњЭЈЙ§ВЂПкаДЪ§ОнЪБЃЌЫќЕФМЦЪ§ЪБжггЩЪ§ОнбЁЭЈаХКХ(Data StrobeЃЃ)РДЧ§ЖЏЃЌБЃжЄМЦЫуЛњУПаДвЛИіЪ§ОнЪЙЕУИпЫйЛКДцЦїЕФЕижЗМг1ЃЛЖјЕБаХКХдДИпЫйЪфГіЪ§ОнЪБЃЌМЦЪ§ЪБжггЩаХКХдДЕФФкВПЪБжгЧ§ЖЏЁЃЫќУЧЕФЧаЛЛЪЧгЩCPLDФкЕФПижЦМФДцЦїРДПижЦЕФЁЃУПДЮдкМЦЫуЛњаДЪ§ОнЪБЃЌгІЕБгЩМЦЫуЛњЭЈЙ§ПижЦМФДцЦїИјМЦЪ§ЦїЧхСуЃЛЖјдкаХКХдДЪфГіЪ§ОнЪБЃЌЧхСуаХКХгЩЪ§ОнГЄЖШМФДцЦїКЭЕБЧАЕижЗжЕЕФБШНЯНсЙћРДШЗЖЈЃЌвЛЕЉЕижЗжЕгыЪ§ОнГЄЖШМФДцЦїЯрЕШЃЌСЂМДВњЩњвЛИіЧхСуаХКХЃЌвдЪЙЪ§ОнДгСуЕижЗДІжмЦкаджиИДЪфГіЁЃИУЕижЗВњЩњЦїЕФТпМдРэШчЭМ5ЫљЪОЁЃ  1.3 ФкВПЪБжгПижЦ ЖдФкВПЪБжгЕФПижЦОіЖЈСЫзюжеЪфГіЪ§ОнЕФЫйТЪЁЃЦфЛљБОЪБжггЩвЛИігадДОЇеёВњЩњЃЌПЩвдЭЈЙ§ИќЛЛОЇеёРДШЁЕУЬиЖЈЕФЪфГіЪБжгЫйТЪЁЃЭЌЪБЬсЙЉЖдИУЪБжгЕФЗжЦЕбЁдёЁЃИУЗжЦЕЦїЪЕМЪЩЯЪЧвЛИі7ЮЛЭЌВН2НјжЦМЦЪ§ЦїЃЌЪфГіОЇеёЪБжгЕФ2/4/8ЃЎЃЎЃЎ128ЗжЦЕСПЃЌгЩДЫЬсЙЉвЛжжгаЯоЕЋШДМђЕЅЕФЪБжгбЁдёЁЃЖдЪБжгЕФбЁдёПЩвдгУМђЕЅЕФAHDLгябдРДЭъГЩЩшМЦЁЃМйЩшЗжЦЕЦїЕФЪфГіЮЊQ6~Q0ЃЌЪБжгЮЊJTCLKЃЌЗжЦЕбЁдёПижЦЮЛЮЊF2~F0ЃЌЪфГіЪБжгЮЊOUTCLKЃЌЯргІAHDLгябдЕФEquationsЖЮШчЯТЃК ?Q6ЃЎЃЎQ0??ЃН?Q6ЃЎЃЎQ0?+1? ЁхЩшМЦ7ЮЛЕФЖўНјжЦМЦЪ§Цї ?Q6ЃЎЃЎQ0?ЃЎclkЃНJTCLK? ЁхМЦЪ§ЦїЪБжгЮЊОЇеёЪфГі WHEN??F2ЃЎЃЎF0?ЃНЃоb000ЁЁ THEN OUTCLK=JTCLK? ЁхВЛЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb001ЁЁ THEN OUTCLKЃНQ0?Ёх1/2ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb010ЁЁ THEN OUTCLKЃНQ1?Ёх1/4ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb011ЁЁ THEN OUTCLKЃНQ2?Ёх1/8ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb100ЁЁ THEN OUTCLKЃНQ3?Ёх1/16ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb101ЁЁ THEN OUTCLKЃНQ4?Ёх1/32ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb110ЁЁ THEN OUTCLKЃНQ5?Ёх1/64ЗжЦЕ WHEN??F2ЃЎЃЎF0?ЃНЃоb111ЁЁ THEN OUTCLKЃНQ6?Ёх1/128ЗжЦЕ ЪфГіЪБжгOUTCLKЗжБ№гУгкЕижЗМЦЪ§ЦїЕФМЦЪ§ЪБжгЧ§ЖЏЁЂDACЕФзЊЛЛЪБжгЧ§ЖЏвдМАВњЩњЪфГіЪ§ОнЕФЭЌВНЪБжг(АќРЈе§ЁЂЗДСНжжЯрЮЛ)ЁЃ 2 аХКХдДPCBАхЩшМЦ гЩгкИУаХКХдДPCBАхКЌгаЪ§зжМАФЃФтСНжжЕчТЗЃЌЪЙЕУPCBАхЕФЩшМЦЗЧГЃЙиМќЁЃШчPCBЩшМЦВЛЕБЃЌНЋЪЙDACЕчТЗЪфГіЕФФЃФтаХКХдыЩљдіДѓЃЌДгЖјгАЯьаХКХдДЕФадФмЁЃ дкИУPCBЩшМЦжаЃЌжївЊПМТЧСНИівђЫиЃЌвЛЪЧЕчдДТЫВЈЃЌСэвЛИіЪЧНгЕиЁЃ дкЕчдДШыПкДІЃЌгІЕБНгШывЛИіМИЪЎЮЂЗЈЕФюуЕчНтЕчШнКЭвЛИі0.1ІЬFЕФЖРЪЏЕчШнЁЃЪ§зжЕчТЗВПЗжЕФЕчдДТЫВЈвЛАужЛашдкЪ§зжICЕФЕчдДЖЫгУвЛжЛ0.1ІЬFЛђ0.01ІЬFЕФЖРЪЏЕчШнНјааХдТЗТЫВЈЁЃИУЕчШнБиаыОЁСПППНќЪ§зжICЕФЕчдДв§НХДІЃЌВЂЧвНгЕиЖЫвЊжБНгНгШыДѓУцЛ§ЕФЕиЯпЃЌЗёдђЪеаЇЩѕЮЂ(МћЭМ6)ЁЃ  ФЃФтЕчТЗЕФ5VЕчдДгІЕБКЭЪ§зжЕчТЗЕФ5VЕчдДЗжПЊзпЯпЃЌжаМфгУДХжщМгвдИєРыЃЌвдЯћГ§Ъ§зжЕчТЗв§Ц№ЕФЕчдДВЈЖЏЖдФЃФтЕчТЗЕФгАЯьЁЃDACЕчТЗЕФдЫЗХвЊЭЌЪБНјааИпЦЕКЭЕЭЦЕТЫВЈЃЌМДдкИїдЫЗХЕФе§ИКЕчдДЖЫЭЌЪБВЩгУЪ§ЮЂЗЈЕФюуЕчНтКЭ0.1ІЬFЕФЖРЪЏЕчШнНјааХдТЗЁЃШчЙћЪЙгУПЊЙиЕчдДЃЌдђдЫЗХЕФе§ИК12VЕчдДЖМвЊгУДХжщДЎСЊвдМѕЧсПЊЙидыЩљЖдЪфГіаХКХЕФгАЯьЁЃ ЯрЖдгкЕчдДТЫВЈЃЌНгЕиЮЪЬтгШЮЊживЊЁЃНгЕиЮЪЬтЕФЙиМќЪЧВЩгУЕЅЕуЙВЕиММЪѕЃЌМДЪ§зжЕчТЗКЭФЃФтЕчТЗСНВПЗжЕФЕиЯпдкPCBАхЩЯбЯИёЗжПЊЃЌжЛдквЛЕуНјааЙВЕиСЌНгЃЌИУЕуГЦЮЊаЧЕу(STAR POINT)ЁЃИУММЪѕФмвжжЦДѓВПЗжФЃЪ§ЛьКЯЕчТЗжаЬигаЕФЪ§зждыЩљЖдФЃФтЕчТЗЕФгАЯьЁЃЖјЧвИљОнРэТлКЭЪЕМЪОбщЃЌФЃФтВПЗжгІЕБжУгкППНќЕчдДШыПкЕФвЛЖЫЁЃ 3 ШэМўЩшМЦ ШэМўВЩгУзЈЮЊащФтвЧЦїЩшМЦЕФLabWindows/CVIРДЭъГЩГЬађЕФжїЬхМАНчУцЩшМЦЃЌЪЙЕУИУаХКХдДЕФШэМўНчУцОпгаецЪЕвЧЦїЕФУцАхЗчИёЁЃгЩгкМЦЫуЛњВЂПкжЛЪЙгУI/OПеМфЃЌВЂЧвДѓЖрЪ§ВйзїЯЕЭГ(ШчWINDOWS9X)ЖМУЛгаЖдI/OЖЫПкНјааЦСБЮЃЌШэМўЕФПижЦКЭЪ§ОнДЋЪфВПЗжОЭЗЧГЃМђЕЅЃЌжБНгЪЙгУI/OКЏЪ§МДПЩ(LabWindows/CVIЬсЙЉЯргІКЏЪ§жЇГж)ЁЃШэМўЕФжївЊЙЄзїЪЧВњЩњЫљашЬиЖЈаХКХЕФЪ§ОнЁЃИљОнашвЊЃЌПЩвдВњЩњСНТЗ8ЮЛЛђЕЅТЗ16ЮЛЕФаХКХЪ§ОнЃЌЦфжа16ЮЛЕФЪ§ОнаХКХвЊЗжЮЊИпЕЭ8ЮЛСНВПЗжЪ§ОнЗжБ№ДЋЫЭЁЃашвЊзЂвтЕФЪЧЃЌШчЙћаХКХЪ§ОнЪЧ16ЮЛЃЌдђDACЕчТЗЪфГіЕФСНТЗФЃФтаХКХгыЪфГіЪ§ОнЪЧВЛвЛжТЕФЃЌжЛгаЦфжавЛТЗПЩвдДжТдЕиЙлВьЕНИУаХКХВЈаЮ(Ъ§ОнИп8ЮЛЕФВЈаЮ)ЁЃЮЊСЫЪЙгУЖржжЙЄОп(ШчMatlabЕШ)ВњЩњЕФаХКХЪ§ОнЃЌШэМўдкВњЩњГЃгУаХКХЕФЛљДЁЩЯЃЌПЩбЁдёЖСШЁЪ§ОнЮФМўЕФЗНЪНЃЌДгЖјПЩвдИќПьИќСщЛюЕиЕУЕНИїжжЬиЖЈаХКХЕФЪфГіЁЃ |

ЭјгбЦРТл