一种基于SOC的FLASH替换设计

发布时间:2014-12-16 10:42

发布者:designapp

|

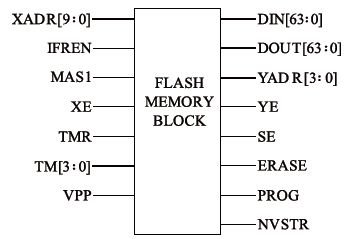

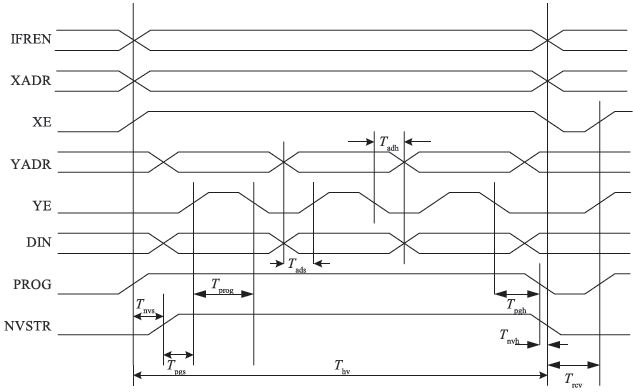

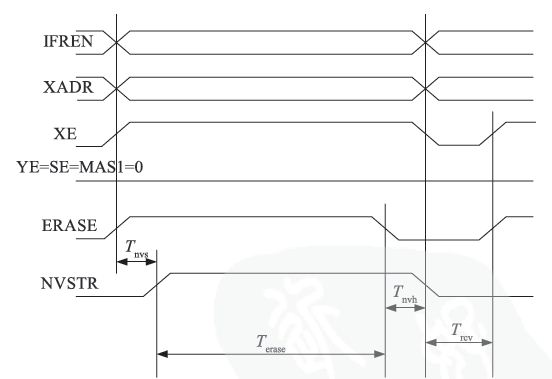

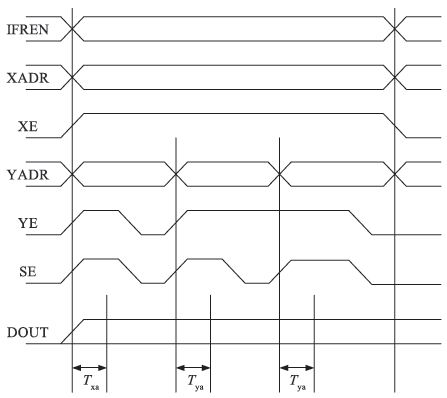

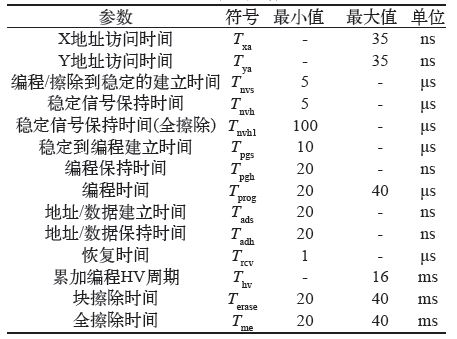

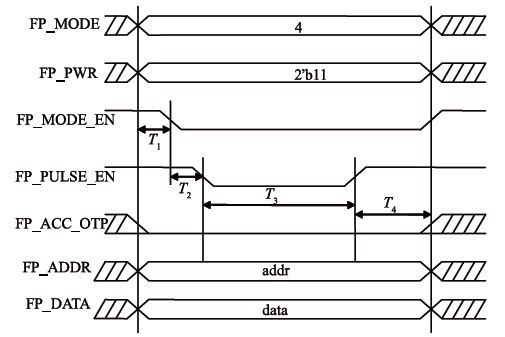

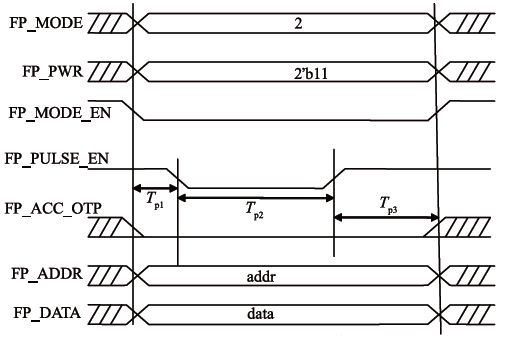

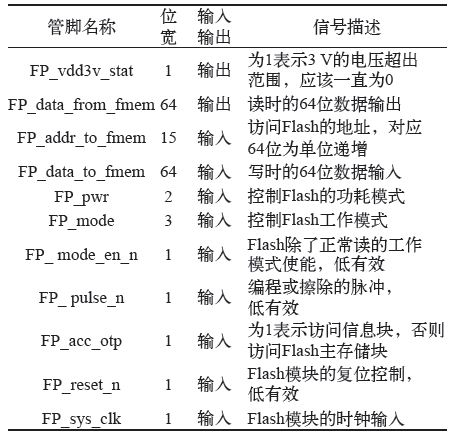

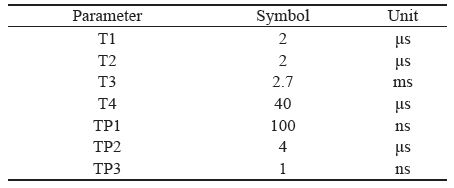

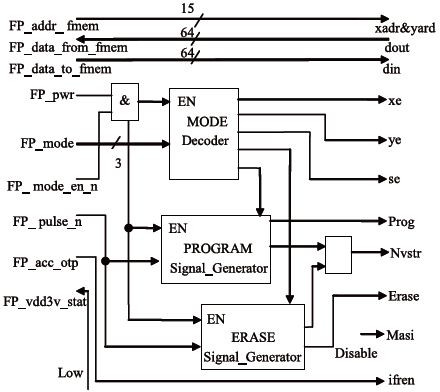

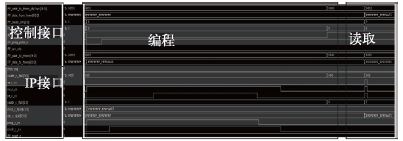

1 引言 FLASH存储器具有成本低、密度大、掉电不丢失的特点,在存储器市场中所占的比例越来越大,作为主流SOC重要组成部分,FLASH对SOC作用与影响也越来越大。 由于SOC设计升级或者原有SOC产品存储容量提升等原因,随之会带来其嵌入式FLASH的替换问题,SOC系统设计规模一般较大,设计更改难度和风险都比较大。除此之外,大部分情况下还需要考虑更改后的设计对原产品的兼容性。通过在原SOC FLASH 控制接口之外增加控制接口转换逻辑实现对新的FLASH IP的连接,可以避免对已成功设计的修改,在达到对FLASH存储器替换的同时降低了设计的风险。而且由于原FLASH控制逻辑完全固化,只要接口转换逻辑正确,替换后的设计将对原产品完全兼容。 通过对FLASH IP接口与参数的分析,结合对已有SOC中Flash接口时序的要求,设计给出了FLASH控制接口与新FLASH IP之间的接口与时序转换逻辑,并通过仿真,对设计的正确性进行验证。 2 FLASH IP分析 2.1 整体介绍 设计所选用的Flash存储器是一款CMOS页擦除、16位编程的嵌入式存储器,包含主存储块和信息存储块。主存储块大小为16k×64,是由128个存储页组成,每个页内有8个行存储单元,每个行又分为16个存储单元,每个存储单元为64位。信息模块大小为320×64,可用来存储固定信息。其擦除操作分为页擦除和块擦除两种,页擦除操作擦除一页内的所有字节,块擦除操作擦除整个主存储块。分立的门单元设计和厚氧化层沟道注入相比于传统的方法获得了更好的可靠性和可制造性。Flash执行擦除和编程操作只需要1.8 V供电,室温下能够长期保存数据。 2.2 接口分析  图1 FLASH接口模块图 整体Flash IP的接口如图1所示。根据功能,可以将接口引脚分为三类:XE、YE、SE、ERASE、PROG、NVSTR、IFREN、MAS1为控制信号线;YADR[3:0]、XADR[9:0]为地址信号;DIN[63:0]、DOUT[63:0]为数据信号。外部地址信号的高低位分别通过地址信号线YADR[3:0]、XADR[9:0]来进行存储单元的定位。其中XADR[9:0]为X地址输入来确定存储单元中某个页中的一行。YADR[3:0]地址确定所选择行中的一个存储单元。DIN[63:0]为数据输入总线;DOUT[63:0]为数据输出总线;控制信号XE、YE分别为X地址和Y地址的使能信号;在进行读取操作时,除了X地址和Y地址使能外,还需要置位SE信号来使能读取操作。IFREN为信息模块使能,置位是选中信息存储块,清零时选中主存储区。ERASE为页擦除使能信号。MAS1为整体擦除使能信号,对其使能可一次擦除整个存储区。PROG为编程使能信号,上述信号均为高电平有效。NVSTR为擦写稳定控制信号,控制擦写时间;VDD、VSS为电源地信号。TMR、VPP以及TM为FLASH IP测试使用。 2.3 接口时序定义与分析 FLASH的编程时序如图2所示。编程操作时,首先将行使能信号XE和编程使能信号PROG同时置高保持,等待至少Tnvs后将NVSTR信号置高,待稳定控制信号NVSTR置高后至少等待Tpgs将列使能YE信号置高,这样再根据读入的地址信号确定编程的地址单元,将数据写入地址单元中。连续编程为了提高编程的稳定性,在编程前保留至少Tads的时间裕量,编程完成后留有Tadh的时间裕量。编程结束时信号PROG保持Tpgh后置低,待PROG置低后Tnvh将NVSTR拉低,两次编程至少间隔Trcv。  图2 FLASH编程时序 FLASH擦除时序如图3 所示。将控制信号YE、SE、MAS1置低,待XE、ERASE使能信号置高后等待Tnvs将信号NVSTR置高,Terase为擦除时间,擦除完成后NVSTR高电平保持Tnvh后置低,连续两次擦除的时间间隔至少为Trcv。  图3 FLASH擦除时序 FLASH读取时序如图4 所示,首先将XE、YE信号置高,XADR和YADR 地址读取使能,地址读取需要Txa和Tya的反应时间,读取数据时应当留有相应的时间裕量确保数据的正确读出,保证测试的可靠性。  图4 FLASH读取时序 由于FLASH IP的操作对时间非常敏感,因此在进行FLASH IP操作时应该按照厂家所给的时间参数进行,如表1。 表1 时间参数  3 FLASH 控制接口分析 已有的FLASH控制接口及描述如表2所示。其擦除和编程时序如图5、图6所示,时序参数如表3所示,其中的信号时序由对应的控制程序来决定。  图5 FLASH控制接口的擦除时序  图6 FLASH控制接口的编程时序 表2 FLASH控制接口及描述  表3 FLASH控制接口时序参数  4 转换逻辑的设计分析 通过上述分析可以看出,原有的FLASH控制接口和FLASH IP的接口不匹配,且时序差别也很大。但是两者也存在一定的相似性,即除了数据和地址信号一样外,其他的信号也基本上都分为模式控制信号和时序信号两部分,因此可分别对两组信号进行转换。在模式控制信号上,原有控制接口中由FP_pwr、FP_mode和FP_ mode_en_n三个信号共同确定操作的模式,而FLASH IP的操作模式由XE、YE和SE决定,设计通过增加模式译码模块在两者之间进行模式信号的转换,实现对新的FLASH IP模式的选择。在时序上,原有的控制接口只有一个脉冲控制信号,根据不同的操作模式,产生的脉冲时间也不同。FLASH IP的时序由多个信号分别对应不同的模式,Prog对应编程脉冲信号,Erase对应擦除脉冲信号,Nvstr为稳定控制信号,起到对脉冲信号的稳定作用。设计根据不同模式将原有的时序控制信号分配到对应的FLASH IP时序脉冲信号上,并根据不同的脉冲宽度进行放大或缩小。除此之外,对一些无相关性的信号进行了一些固定值设定。整体转换逻辑如图7所示。  图7 逻辑转换结构图 5 仿真测试 本文使用Cadence公司开发的仿真软件Ncsim对FLASH IP进行了相应的功能仿真,通过对FLASH的接口时序分析,分别测试了FLASH的读写擦操作,由于FLASH的编程只能将相应位上的1编程成0,不能降0置1,因而在进行每次编程操作前都要先将相应地址的数据擦除成全1 然后将相应的数据编入相应的地址中。仿真时首先对地址0050进行擦除后读取的操作如图8所示。从图中IP接口一栏的信号可以看出,仿真对地址0050进行了擦除操作后读取地址内数据为FFFFFFFF_FFFFFFFF。随后对地址0052进行了编程操作,如图9所示。将数据FFFFFFFF_FFFFAA55写入地址后再将数据读出。从仿真结果可以看出设计实现了对新FLASH的读写擦操作,达到了设计要求。  图8 FLASH擦除操作  图9 FLASH编程操作 6 总结 本文通过对FLASH接口时序的分析并设计了相应的测试激励,分别实现了对FLASH的读写擦等功能的测试,达到了预期测试的目标。通过后续的综合和静态时序分析,FLASH已经成功用于一款定点32位DSP芯片当中。 |

网友评论