XilinxНЖіцХл¶ФOpenCLЎўCәН C++өДSDAccelҝӘ·ў»·ҫі

·ўІјКұјдЈә2014-11-18 14:16

·ўІјХЯЈәeechina

|

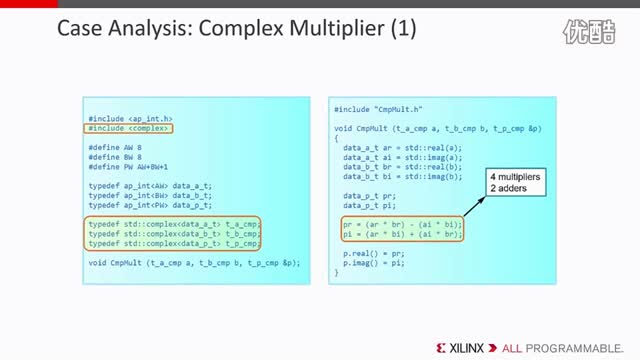

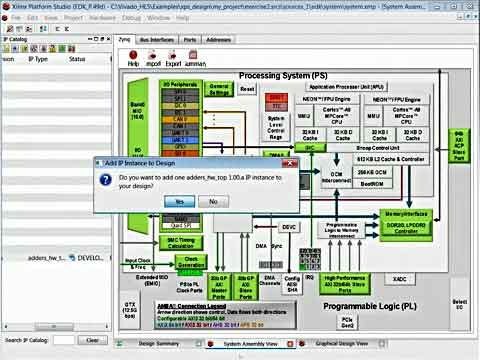

ИьБйЛј№«ЛҫЈЁXilinxЈ©НЖіцХл¶Ф OpenCLЎўC әН C++өДS DAccel ҝӘ·ў»·ҫіЈ¬Ҫ«өҘО»№ҰәДРФДЬМбёЯҙп25ұ¶Ј¬ҙУ¶шАыУГ FPGA КөПЦКэҫЭЦРРДУҰУГјУЛЩЎЈSDAccel КЗИьБйЛј SDxПөБРөДЧоРВіЙФұЈ¬Ҫ«ТөҪзКЧҝоЦ§іЦ OpenCLЎўC әН C++ ДЪәЛИОТвЧйәПөДјЬ№№УЕ»ҜұаТлЖчЎўҝвЎўҝӘ·ў°еНкГАҪбәПФЪТ»ЖрЈ¬ФЪ FPGA ЙПКЧҙОКөПЦБЛНкИ«АаЛЖ CPU/GPU өДҝӘ·ўәНФЛРРКұјдМеСйЎЈ ҙч¶ы№«ЛҫЖҪМЁјЬ№№УлјјКхј° CTO °м№«КТЦҙРРЧЬја Robert Hormuth ЦёіцЈәЎ°»щУЪ FPGA өДјјКхУРБЛРВөДН»ЖЖЈ¬ДЬЦ§іЦУЕ»ҜөДјЖЛгУҰУГЎЈФЪҙч¶ы·юОсЖчІҝКрөД№эіМЦРЈ¬јт»ҜұаіМКЗҫц¶ЁІЙУГ FPGA јУЛЩЖчөД№ШјьХП°ӯ ЎЈ әБОЮТЙОКЈ¬ИьБйЛјҝӘұЩБЛТ»МхХэИ·өДөАВ·Ј¬ИГҝӘ·ўИЛФұДЬ№»ҪиЦъТ»ёцИнјю»·ҫіЈ¬МбёЯ FPGA ЖҪМЁУГ»§өДЙъІъБҰЎЈЎұ IBM өзФҙҝӘ·ўёұЧЬІГјж OpenPOWER »щҪр»бЧЬІГ (IBM vice president of Power Development and OpenPOWER president) Brad McCredie ұнКҫЈәЎ°IBM ёЯ¶ИФЮЙНИьБйЛјЦВБҰУЪКөПЦЖд FPGA ИнјюҝЙұаіМРФХвТ»·ўХ№·ҪПтЎЈАыУГ CЎўC++әН OpenCL ҙҙҪЁУЕ»ҜРН FPGA јУЛЩЖчөДёЯ¶ИБй»оРФәНҝЙҝҝөДҪб№ыЦКБҝЈ¬ДЬМбЙэ IBM ОӘҝН»§ҙшАҙёьҙујЫЦөөДДЬБҰЎЈIBM јбРЕ OpenCL ¶ФМбёЯЙъІъБҰҙуУРсФТжЈ¬Н¬КұОТГЗХэФЪУлИьБйЛјХ№ҝӘҪфГЬәПЧчЈ¬Ҫ«ёГјјКхУҰУГөҪОТГЗөД OpenPOWER ІъЖ·ЙијЖЦРЎЈЎұ КЧҝоХл¶Ф OpenCLЎўC әН C++ өДјЬ№№УЕ»ҜұаТлЖч SDAccel өДјЬ№№УЕ»ҜұаТлЖчПа¶Ф CPU »т GPUЈ¬өҘО»№ҰәДРФДЬМбёЯҙп25ұ¶Ј¬Па¶ФЖдЛь FPGA Ҫвҫц·Ҫ°ёЈ¬РФДЬәНЧКФҙР§ВКМбёЯ3ұ¶ЎЈSDAccel ІЙУГБЛТСұ»1,000¶аГыіМРтФұ№г·әК№УГөД»щҙЎұаТлЖчјјКхЎЈSDAccel ід·ЦАыУГёГұаТлЖчөД№ҰДЬЈ¬К№ИнјюҝӘ·ўИЛФұДЬ№»АыУГРВөД»тПЦУРөД OpenCLЎўC әНC++ ҙъВлҙҙҪЁёЯРФДЬјУЛЩЖчЈ¬ІўХл¶ФјЖЛгЛСЛчЎўНјПсК¶ұрЎў»ъЖчС§П°ЎўұаВлЧӘ»»ЎўҙжҙўС№ЛхәНјУГЬөИёчЦЦКэҫЭЦРРДУҰУГЦРөДҙжҙўЖчЎўКэҫЭБчәНБчЛ®ПЯјјКхҪшРРБЛҫ«РДУЕ»ҜЎЈ ФЪ FPGA ЙПКЧҙОКөПЦНкИ«АаЛЖ CPU/GPU өДҝӘ·ўМеСй ҪиЦъ SDAccelЈ¬ҝӘ·ўИЛФұДЬ№»К№УГЖдКмПӨөД№ӨЧчБчіМУЕ»ҜУҰУГЈ¬¶шЗТјҙұгЦ®З°Г»УР FPGA К№УГҫӯСйЈ¬ТІДЬКЬТжУЪ FPGA ЖҪМЁөДУЕКЖЎЈјҜіЙЙијЖ»·ҫі (IDE) І»ҪцҝЙМṩұаВлДЈ°еәНИнјюҝвЈ¬¶шЗТ»№ДЬ¶ФёчЦЦҝӘ·ўДҝұкҪшРРұаТлЎўөчКФәНМШРФ·ЦОцЈ¬ИзФЪ X86ЖҪМЁЙП·ВХжЎўК№УГҝмЛЩ·ВХжҪшРРРФДЬСйЦӨТФј°ФЪ FPGA ҙҰАнЖчЙПҪшРРұҫөШЦҙРРөИЎЈIDE ҝЙФЪКэҫЭЦРРДУГ FPGA ЖҪМЁЙПЦҙРРУҰУГЎЈёГЖҪМЁЕдМЧМṩГжПтЛщУРЦ§іЦҝӘ·ўДҝұкөДЧФ¶ҜТЗЖчІеИл№ҰДЬЎЈҙЛНвЈ¬SDAccel »№ҫӯ№эҫ«РДЙијЖЈ¬К№ CPU/GPU ҝӘ·ўИЛФұДЬ№»ЗбЛЙҪ«ЖдУҰУГЗЁТЖөҪ FPGA ЙПЈ¬Н¬Кұ»№ҝЙФЪЛыГЗКмПӨөД№ӨЧчБчіМЦРО¬»ӨәНёҙУГ OpenCLЎўC әН C++ҙъВлЎЈ ЧЫәПИ«ГжөД SDAccel »·ҫі°ьАЁұаіМЖчУГ IDEЎў»щУЪCУпСФөД FPGA УЕ»ҜҝвЈ¬ТФј°КэҫЭЦРРДУГПЦіЙЙМУГ (COTS) ЖҪМЁЎЈ SDAccel ҝв°ьАЁУГУЪёЯРФДЬөН№ҰәДКөПЦ·Ҫ°ёөДДЪЦГ OpenCL әҜКэЎўDSPЎўКУЖөТФј°ПЯРФҙъКэҝвЎЈХл¶ФМШ¶ЁБмУтјУЛЩЈ¬ИьБйЛјБӘГЛәПЧчіЙФұ Auviz Systems МṩБЛҫ«РДУЕ»ҜөД OpenCV әН BLAS OpenCL јжИЭРНИнјюҝвЎЈФӯУРөД COTS іЙФұ°ьАЁ Alpha DataЎўConveyЎўPico ComputingЈ¬ФӨјЖ2015ДкДкіх»№Ҫ«ФцјУёь¶аіЙФұЎЈ ФЪ FPGA ЙПКЧҙОКөПЦНкИ«Ул CPU/GPU өДФЛРРКұјдМеСй Ц»УР SDAccel ДЬ№»Ц§іЦҙшУР¶аёціМРтәНАаЛЖ CPU/GPU °ҙРиҝЙјУФШјЖЛгөҘФӘөДУҰУГЎЈУл CPU/GPU АаЛЖЈ¬SDAccel ¶ФУЪ FPGA Ҫвҫц·Ҫ°ёөД¶АМШЦ®ҙҰЈ¬ФЪУЪДЬ№»ұЈіЦіМРтЧӘ»»№эіМЦРөДПөНіХэіЈ№ӨЧчЎЈSDAccel КЗТөҪзОЁТ»ДЬ№»ҙҙҪЁҝЙФЪУҰУГФЛРР№эіМЦРјУФШРВјУЛЩЖчДЪәЛөД FPGA јЖЛгөҘФӘөД»·ҫіЎЈ ФЪХыёцУҰУГЦҙРР№эіМЦРЈ¬ҙжҙўЖчЎўТФМ«НшЎўPCIe®әНРФДЬјаҝШЖчөИ№ШјьПөНіҪУҝЪәН№ҰДЬҫщұЈіЦ№ӨЧчЧҙМ¬ЎЈјҙКұҝЙЦШЕдЦГөДјЖЛгөҘФӘҝЙИГ¶аёцУҰУГ№ІПн FPGA јУЛЩЖчЎЈАэИзНЁ№э¶ФФЛРРПөНіұаіМЈ¬ҝЙЦ§іЦНјПсЛСЛчЎўКУЖөЧӘВләННјПсҙҰАнЦ®јдөДЗР»»ЎЈ №©»хЗйҝц ИьБйЛјФЪГА№ъР°¶ыБјКРҫЩРРөД2014№ъјКі¬Лгҙу»бЙПКөКұСЭКҫБЛ SDAccel ІъЖ·ЎЈИзРиБЛҪвёь¶а SDAccel ФзЖЪКФУГ°жөД№ҰДЬЈ¬ҫҙЗлБӘПөұҫөШөДПъКЫҙъұнЎЈИзУыБЛҪвёь¶аПкЗйЈ¬ҫҙЗл·ГОКЈәhttp://www.xilinx.com/sdaccel ЎЈ ёГІъЖ·»щУЪТС·ўІјөД Khronos №ж·¶Ј¬УРНыНЁ№э Khronos Т»ЦВРФІвКФ№эіМЎЈИзУыБЛҪвУР№ШөұЗ°өДТ»ЦВРФІвКФЧҙМ¬Ј¬ҫҙЗл·ГОКЈәhttp://www.khronos.org/conformanceЎЈ |

НшУСЖАВЫ