КұЦУІЙСщПөНіЧоҙуПЮ¶ИјхЙЩ¶¶¶Ҝ

·ўІјКұјдЈә2014-10-27 15:13

·ўІјХЯЈәeechina

|

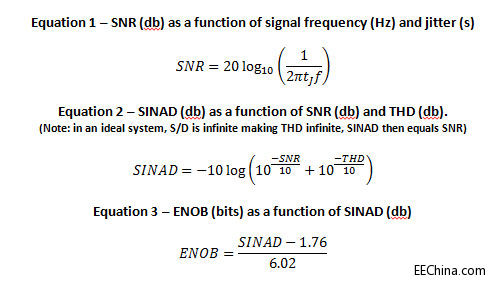

ЧчХЯЈәRichard ZarrЈ¬TI№«Лҫ әЬ¶аИЛ¶јЦӘөАЈ¬¶¶¶ҜЈЁХвКЗКұЦУұЯСШІ»И·¶ЁРФЈ©КЗІ»әГөДПЦПуЈ¬ЖдІ»ҪцҝЙөјЦВФлЙщФцјУЈ¬¶шЗТ»№»бҪөөНКэҫЭЧӘ»»ЖчөДУРР§О»Кэ (ENOB)ЎЈ АэИзЈ¬Из№ыПөНіРиТӘ 100MHz 14ЈЁЧоРЎЦөЈ©О»өД ENOBЈ¬ОТГЗҫНРиТӘ¶¶¶ҜРЎУЪ 80 ·ЙГлөДКұЦУЈЎХвҝЙНЁ№эјЩЙиТ»ёцОЮК§ХжөДАнПлПөНіҪшРРјЖЛгЈ¬ИГ SINAD әН SNR КэЦөПаөИЈЁјы№«КҪ 2Ј©ЎЈ ҪУПВАҙЈ¬К№ ENOB өИУЪ 14Ј¬ОТГЗҝЙФЪҙуФј 86db ПВјЖЛгіцЧоРЎ SNRЎЈҪ«Ҫб№ыҙшИ빫КҪ 1Ј¬јЖЛгіцҙуФјОӘ 80fs өД tJ ЦөЎЈ

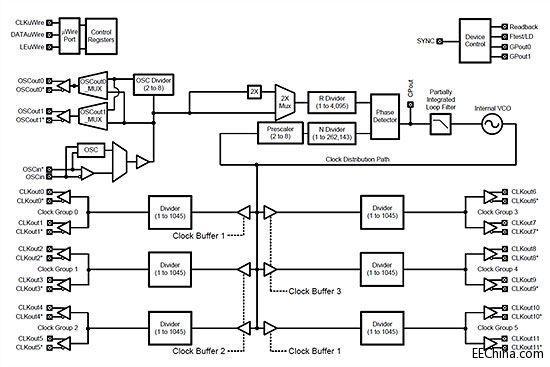

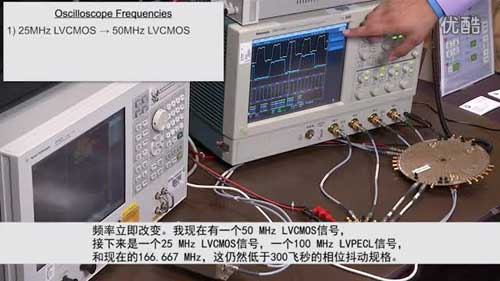

№«КҪ 1 ФЪКэЧЦРЕәЕҙҰАн№эіМЦРЈ¬ІЙСщКұЦУУлҙҰАнКұЦУЦ®јдРиТӘУРТ»¶Ё№ШБӘЎЈТІҫНКЗЛөЈ¬ОЮВЫКЗФЪК®·ЦЦ®Т»ЛЩВКПВ»№КЗФЪИ«ЛЩВКПВІЙСщЈ¬СщЖ¬¶јұШРлФЪЖдЛЩВКөДұ¶КэПВҪшРРҙҰАнЈ¬¶шЗТТӘПаО»Т»ЦВЎЈХвҫНРиТӘТ»ёцЎ°ЦчЎұКұЦУЈ¬ЖдҝЙУГАҙСЬЙъПөНіЦРөДЛщУРЖдЛьКұЦУЎЈ ДъҝЙК№УГОВ¶ИІ№іҘҫ§МеХсөҙЖч (TCXO) әНөНПаО»ФлЙщ PLL КөПЦХвТ»өгЈ¬ҝЙҪ«ЦчКұЦУПФЦшФцјУЦБёьёЯөДЖөВКЎЈИ»әуЈ¬ДъҝЙ¶ФёГЧоРВёЯЖөВККұЦУҪшРРПВ·ЦЖөЈ¬ТФМṩ¶јУлЦчКұЦУПа№ШБӘөДКЈУаПөНіКұЦУЎЈХвСщЈ¬ІЙСщКұЦУТФј°ёчЦЦКэЧЦҙҰАнКұЦУ¶јПа»ҘҫЯУР№ШБӘРФЎЈ ПЦФЪУРәЬ¶аКұЦУҪвҫц·Ҫ°ёЈ¬ө«әЬ¶а¶јРиТӘКұЦУ»әіеЖч»тЖдЛьКұЦУ·ЦЕд·Ҫ·ЁЈ¬ЖдҝЙҪөөНХыМ嶶¶ҜРФДЬЎЈДъҝЙК№УГИз LMK03806 өИТ»ҝоЖчјюАҙҝЛ·юХвёцОКМвЈ¬ЖдФЪН¬Т»ЖчјюЦРХыәПБЛЛщУРЦчКұЦУ·ўЙъЖчәНКұЦУ·ЦЕд№ҰДЬЈЁҙшЗэ¶ҜЖчЈ©Ј¬ИзНј 1 ЛщКҫЎЈёГЖчјюҝЙФЪ 300MHz ПВФЛРРөДН¬КұЈ¬ҫЯУРІ»Чг 50fs өД RMS ¶¶¶ҜЈЁ1.875MHz ЦБ 20MHzЈ©ЎЈҙЛНвЈ¬Дъ»№ҝЙНЁ№э¶ФКдіцҪшРРұаіМАҙЦ§іЦ LVDSЎўLVPECL »т LVCMOS Іў¶ФЖдҪшРРН¬ІҪЈ¬ТФ»сөГ№ІУГЙПЙэСШЎЈ Нј 1 ЎӘ LMK03806ЈЁҫЯУРКұЦУ·ўЙъЖчЎўКұЦУ·ЦЖөЖчәНЗэ¶ҜЖчЈ©өД·ҪҝтНј

Нј 1 ЎӘ LMK03806ЈЁҫЯУРКұЦУ·ўЙъЖчЎўКұЦУ·ЦЖөЖчәНЗэ¶ҜЖчЈ©өД·ҪҝтНј ТтҙЛЈ¬ДъПВҙОЙијЖІЙСщПөНіКұЈ¬ұрНьБЛҝјВЗКұЦУ¶¶¶ҜРФДЬЈ¬ТтОӘХв»бУ°ПмХыМе¶ҜМ¬·¶О§ЎЈ ЖдЛьЧКФҙЈә ФД¶БОТГЗөДЧоРВІ©ҝНПөБРЎ¶¶ЁКұҫц¶ЁТ»ЗРЎ·Ј¬ХЖОХёь¶аКұЦУјјЗЙЈ¬ИзИзәОІвБҝ¶¶¶ҜТФј°ИзәОК№УГ·ЦКэ PLL ҙҙҪЁөчЦЖІЁРОөИЈ» №ЫҝҙЎ¶ИзәОІвБҝЙИіц»әіеЖчЦРөДёҪјУ¶¶¶ҜЎ·КУЖөЈ» ҪшТ»ІҪБЛҪвОТГЗГжПтОЮПЯј°УРПЯНЁРЕЎў№ӨТөТФј°ЖыіөУҰУГөДКұЦУІъЖ·ПөБРЎЈ |

НшУСЖАВЫ