主流DSP存储器测试方法学习指南:TI KeyStone

发布时间:2014-7-23 10:40

发布者:wangjiamin

|

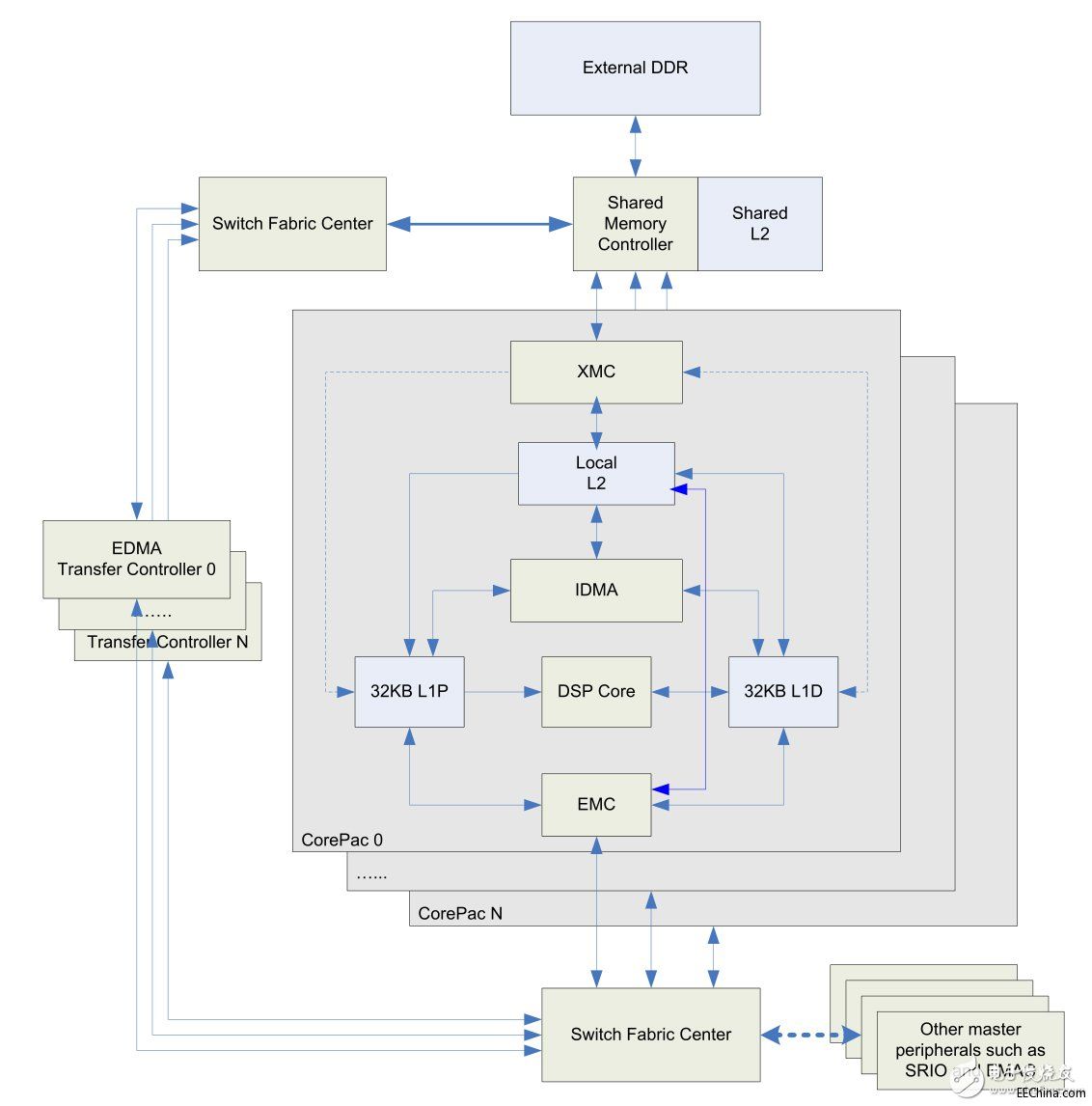

存储器相关的问题是DSP 应用中非常普遍的问题。本文介绍KeyStone I 系列DSP 上一些存储器测试的方法。 1 KeyStone DSP 存储器系统简介 KeyStoneDSP 存储器架构如图1 所示

对不同的DSP,存储器的大小可能不同,DSP 核和EDMA 传输控制器的个数也可能不同。表1比较了KeyStoneI 系列中常用的3颗DSP。

2 存储器测试算法 本文介绍几种存储器测试算法,并讨论这几种算法的用途。 2.1 数据测试 下面是数据测试的伪代码: for(memory range under test) fill the memory with a value; for(memory range under test) read back the memory andcompare the readback value to the written value 通常,这个测试会被执行几次,每次填充的值不一样。常用的填充值包括0x55555555,0xAAAAAAAA, 0x33333333, 0xCCCCCCCC, 0x0F0F0F0F,0xF0F0F0F0, 0x00FF00FF,0xFF00FF00FF00, 0xFFFFFFFF, 0。 这个测试可以用来检测数据比特粘连(bit-stuck)问题,例如,如果, writtenvalue = 0, readbackvalue = 0x8, 表示bit3 粘连到1. 如果 writtenvalue = 0xFFFFFFFF, readbackvalue = 0xFFFFFFFE, 表示bit0 粘连到0. 如果能正确的写入并读出0x55555555(或0xAAAAAAAA),说明相邻的两个比特没有粘连;如果能正确写入并读出0x33333333(或0xCCCCCCCC),说明相邻的4 个比特没有粘连;如果能正确写入并读出0x0F0F0F0F(或0xF0F0F0F0),说明相邻的8 个比特没有粘连… 这个算法既可以用来测试数据总线连接,也可以用于测试存储器单元。当用于测试存储器单元时则每一个存储单元都需要写读所有的值,这将是比较耗时的测试;而用于测试数据总线连接时,只需要把所有的值都写读一遍就可以了(地址不限)。 ........ 更多精彩内容请看附件

主流DSP存储器测试方法学习指南:TI KeyStone.pdf

(518.56 KB)

主流DSP存储器测试方法学习指南:TI KeyStone.pdf

(518.56 KB)

|

网友评论