Imagination ·ўІјИ«ЗтµЪТ»їоДЪЦГУІјюРйДв»ЇјјКхµД MCU ј¶ CPU IP ДЪєЛ

·ўІјК±јдЈє2014-2-28 10:25

·ўІјХЯЈєeechina

|

MIPS Warrior M-class ДЪєЛїЙОЄ IoTЎўїЙґ©ґчЙи±ёЎўЖыіµµИ№г·єµДИлГЕј¶ЦЗДЬЗ¶ИлКЅУ¦УГґшАґИ«РВµД°ІИ«РФУлїЙїїРФ Imagination TechnologiesРыІјЈ¬НЖіцИ«ЗтµЪТ»їоДЪЦГУІјюРйДв»ЇјјКхµДОўїШЦЖЖчЈЁMCUЈ©ј¶ CPU IP ДЪєЛ ЎЄЎЄ їЙОЄёчЦЦИлГЕј¶У¦УГґшАґИ«РВµДБй»оРФЎў°ІИ«РФУлїЙїїРФЎЈХвїоµН№¦єДЎўРЎЗЙЎўјґК±µД MIPS M-class M51xx ДЪєЛКЗИлГЕј¶ MIPS Series5 Warrior CPU µДКЧЕъіЙФ±Ј¬ДЬґпµЅ MCU ј¶ґ¦АнЖчµДЧоёЯ CoreMark/MHz »щЧјІвКФ·ЦКэЎЈM51xx ДЪєЛКЗ№¤ТµїШЦЖЎўОпБЄНшЈЁIoTЈ©ЎўїЙґ©ґчЙи±ёЎўФЖјЖЛгЎўОЮПЯНЁРЕЎўЖыіµЎўґжґўєНЖдЛыУ¦УГµДАнПлСЎФсЎЈ

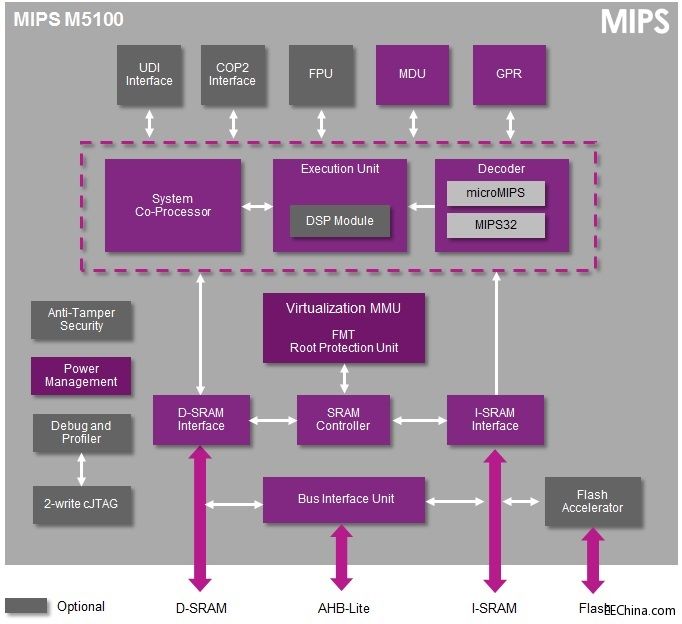

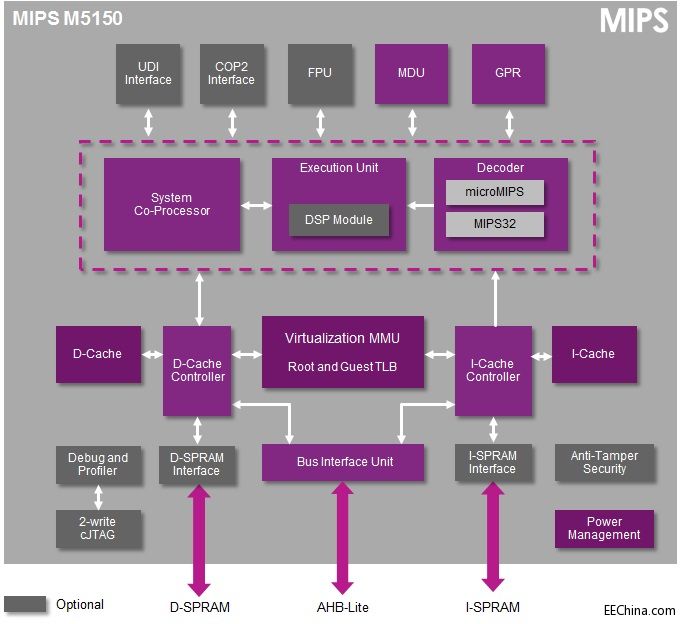

Imagination КРіЎУЄПъЦґРРё±ЧЬІГ Tony King-Smith ±нКѕЈєЎ°ЖѕЅи MIPS Series5 M-class IP ДЪєЛµДНЖіцЈ¬ОТГЗПаРЕЅ«ДЬОЄЗ¶ИлКЅКАЅзґшАґИ«РВµДЙијЖЛјО¬ЎЈѕЩАэАґЛµЈ¬РйДв»ЇТ»Ц±±»КУОЄ·юОсЖчµИёЯј¶У¦УГЛщІЙУГµДЗїґујјКхЎЈИ»¶шЈ¬Imagination Ф¤јыµЅБЛ CPU µД·ўХ№ЗчКЖЈ¬Ѕ«іЇПтёьПИЅшµД¶аДЪИЭ°ІИ«РФУл¶аЦґРРУтА©Х№Ј¬ХвѕНКЗОЄКІГґОТГЗѕц¶ЁФЪИ«ПµБРµД MIPS Series5 CPU ІъЖ·ЦРХыєПРйДв»ЇјјКхЈ¬°ьАЁРВїоµДИлГЕј¶ M51xx ПµБРДЪєЛЎЈЎ± Ў°ОТГЗµДЦШТЄКЪИЁїН»§УлєПЧч»п°йТС¶ФРВїо M-class CPU µДУЕТмРФДЬУлµН№¦єДМШРФІъЙъЕЁєсРЛИ¤ЎЈЅбєПРйДв»ЇЎўНкХыµДёЎµгФЛЛ㵥ԪєНПИЅш DSP №¦ДЬЈ¬ТФј°ОТГЗЧФјєєНГчµј№ъјКУл Green Hills Software µИЙъМ¬ПµНі»п°йМṩµДНк±ё№¤ѕЯИнјюЈ¬ОТГЗ·ЗіЈУРРЕРДЈ¬Ѕ«ДЬФЪЧоїбУлЧоѕЯґґРВµДРѕЖ¬єНЦХ¶ЛІъЖ·ЦРїґµЅёь¶аµДMIPS З¶ИлКЅ CPUЎЈЎ± КЧПИНЖіцµД M-class ДЪєЛОЄ M5100 Ул M5150ЎЈM5100 ХыєПБЛТ»ёцјґК±ЦґРРµҐФЄєН SRAM їШЦЖЖчЈ¬ІўХл¶ФµНіЙ±ѕЎўµН№¦єДОўїШЦЖЖчУ¦УГЅшРРЧоУЕ»ЇЙијЖЎЈM5150 ІЙУГУл M5100 ПаН¬µДЦґРРµҐФЄЈ¬УЦФцјУБЛїЙ±аіМL1 ЦёБоcacheУлКэѕЭcacheїШЦЖЖчЈ¬ТФј°Хл¶ФёЯРФДЬ Linux Ул RTOS З¶ИлКЅПµНіУ¦УГµДґжґўЖч№ЬАн№¦ДЬЎЈ Imagination µДЙПТ»ґъИлГЕј¶ MIPS ДЪєЛѕНТСід·Ц·ґУііцёГ№«ЛѕФЪЗ¶ИлКЅґ¦АнБмУтµДЗїґуКµБ¦Ј¬ґЛДЪєЛїЙМṩͬАаБмПИµДРФДЬР§ВКЈ¬ІўТС»сµГєЬ¶аУ¦УГµД№г·єІЙДЙЎЈImagination ТСЅ« M51xx ДЪєЛКЪИЁёш¶ајТїН»§Ј¬УГАґїЄ·ўЗ¶ИлКЅґ¦АнЎўЖыіµµИёчЦЦУ¦УГЎЈ УлЖдЛыµД MIPS Series5 ДЪєЛПаН¬Ј¬M-class ДЪєЛІЙУГДЪЦГУІјюРйДв»ЇјјКхµД MIPS Release 5 јЬ№№ЎЈM51xx ДЪєЛН¬СщУµУР 5 ј¶БчЛ®ПЯјЬ№№Ј¬УµУРЙПТ»ґъ MIPS microAptiv ПµБРДЪєЛПаН¬µДёЯРФДЬЎўНк±ёµДКэЧЦРЕєЕґ¦АнЈЁDSPЈ©/SIMD МШРФЈ¬ТФј°їЙТФ°С 32 О»ґъВлµДИЭБїјхЙЩ30%µД microMIPS ЦёБојЇјЬ№№ЈЁISAЈ©ЎЈ РйДв»ЇЈєККУ¦ОґАґµДЙијЖРиТЄ ФЪ MCU ј¶µДДЪєЛЦРјУИлУІјюРйДв»ЇјјКхЈ¬їЙОЄ№г·єµДУ¦УГМṩёьјСµД°ІИ«РФУлїЙїїРФЎЈёщѕЭ¶ајТєПЧч»п°йµД·ґАЎТвјыЈ¬Imagination ПаРЕЈ¬І»№ЬґУµН¶ЛµЅёЯ¶ЛУ¦УГЈ¬¶ФУЪРйДв»ЇјјКхµДРиТЄ¶јЅ«ИХТжМбЙэЎЈХв±гКЗImagination ѕц¶ЁФЪИ«ПµБР MIPS Series5 Warrior ДЪєЛЦРДЪЦГУІјюРйДв»ЇјјКхµДФТтЎЈ°ьАЁИлГЕј¶ M-classЎўЦР¶Л I-class ТФј°ёЯ¶Л P-class ДЪєЛЈ¬АґОЄЛщУРµД SoC єНПµНіІъЖ·ґтФмТ»ЦВµД°ІИ«РФУлРйДв»ЇІЯВФЎЈ АыУГРйДв»ЇјјКхЈ¬¶аёцОґѕРЮёДµДІЩЧчПµНіУлУ¦УГіМРт¶јДЬФЪµҐТ»ЎўїЙРЕАµµДЖЅМЁЙПН¬К±¶АБўЗТ°ІИ«µШФЛРРЎЈХвДЬОЄПµНіїЄ·ўґшАґєЬ¶аєГґ¦Ј¬°ьАЁЈє • ѕЯ±ёїЙ¶АБўЦґРР¶аЦШИООсµДДЬБ¦ • єбїз¶аёцїНМеЈЁguestsЈ©µДЦЗДЬЧКФґЕдЦГ • °ІИ«µДПВФШУлЙПґ« • IP ±Ј»¤ MIPS РйДв»ЇјЬ№№ДЪЦГБЛУЕПИј¶»ъЦЖЈ¬Чо¶аїЙЦ§іЦ 7 ёц°ІИ«/·З°ІИ«їНМеЈ¬ОЄКµК±К±№¦ДЬРФМṩЧоУЕ»ЇµДЦ§іЦЎЈ ФЪ IoT »тїЙґ©ґчЙи±ёµИїХјдКЬПЮµДµН№¦єДПµНіЦРЈ¬РйДв»ЇјјКхДЬУГАґ№№ЅЁ¶аёцїНМе»·ѕіЈ¬ЖдЦРТ»ёцФЛРРКµК±ДЪєЛЈ¬№ЬАнґ«ёРЖчКэѕЭµД°ІИ«ґ«Кд;БнТ»ёцїНМеФЪ RTOS µДїШЦЖПВЈ¬ОЄПµНіМṩ¶аГЅМ幦ДЬЎЈ¶ФУЪТЄЗуёьёЯ°ІИ«ј¶±рµДУ¦УГАґЛµЈ¬РВїо M-class ДЪєЛ»№ѕЯ±ё·АґЫёДМШРФЈ¬ДЬХл¶Фґ¦АнЖчФЛРРЧґМ¬µДІ»ХэіЈ¶БИЎМṩПаУ¦µДґлК©ЎЈґЛНвЈ¬НЁ№э·АЦ№НвІїµчКФМЅХл¶БИЎєНСЇОКДЪєЛДЪІїЈ¬РВїо M-class ДЪєЛµД°ІИ«µчКФ№¦ДЬЅшТ»ІЅМбЙэЖд°ІИ«МШРФЎЈ FPUЈєёЯ¶ЛРФДЬЎўѕ«ЗЙіЯґз РВїо M51xx ДЪєЛ»№їЙМṩёЎµгФЛЛ㵥ԪЈЁFPUЈ©СЎПоЈ¬їЙН¬К±Ц§іЦµҐѕ«¶ИєНЛ«ѕ«¶ИЦёБоЈ¬АґФцЗїїШЦЖПµНіµДґ¦АнІЩЧчЎЈХвТ» FPU ТСНЁ№эСйЦ¤Ј¬ІўДЪЦГФЪёЯ¶ЛµД MIPS ДЪєЛЦРЎЈ їЄ·ў№¤ѕЯЈєВъЧгЛщРиЎўТ»У¦ѕгИ« Imagination єН¶ајТ MIPS З¶ИлКЅЙъМ¬ПµНіµДєПЧч»п°йТСОЄ M51xx ДЪєЛМṩ№г·єµДїЄ·ў№¤ѕЯТФј°Ц§іЦ.°ьАЁMentor GraphicsєН Green Hills Software µД±аТлЖчЎўїЄ·ў°еУлµчКФМЅХлЈ¬јУЙПLinux єН¶аЦЦ RTOS ПµНіЈ¬ТФј° Imagination µД MeOSЎЈґЛНвЈ¬Imagination УлБмПИµДµЪИэ·Ѕ hypervisor їЄ·ўЙМТІТСДЬМṩ»тХэФЪЅшРРїЄ·ў M-class ДЪєЛККУГµД hypervisorЈ¬ТФРЦъїН»§ід·Ц·ў»УУІјюРйДв»ЇјјКхµДУЕКЖЎЈЖдЦР°ьє¬¶аїоїЄФґ hypervisorЈ¬АэИз KVM ЈЁKernel-based Virtual MachineЈ¬»щУЪДЪєЛµДРйДв»ъЈ©Ј¬ТФј°ОўДЪєЛ hypervisorЎЈЦ§іЦ M5150ДЪєЛµДїЄ·ЕФґ hypervisor ПЦТСѕНРчЎЈ №©У¦Зйїц MIPS M5150 єН M5100 ДЪєЛјґИХЖрТСїЙМṩКЪИЁЎЈёь¶аРЕПўЈ¬Зл·ГОК info@imgtec.comЎЈ |

НшУСЖАВЫ