低侧栅极驱动器设计 - 第2部分,电路选择

发布时间:2014-1-3 14:19

发布者:eechina

关键词:

栅极驱动

|

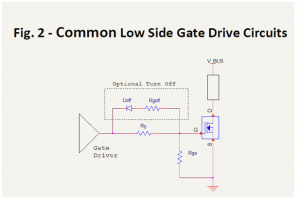

在第1部分,我们探讨了MOSFET的基本属性,并建立了应用于选择低压栅极驱动器时的一些重要参数。现在让我们介绍一些与之配合使用的常见电路。 常见电路 使用低侧栅极驱动器来驱动MOSFET作为负载开关通常可通过符合基本要求的简单电路来完成: 1) 需要的导通和关断时间 2) 导通和关断期间漏极dV/dt限制 3) 最小化栅极和漏极的振铃和振荡 4) 限制栅极电压过冲,但在导通时提供足够的稳定的栅极电压 在某些应用中,只有通过串联栅极电阻才能符合这些要求。在其他设计中,可能需要 “栅极快速关断”电路,从而允许非对称导通和关闭特性,如下所示(Doff和 Rgoff)。 常见的栅极驱动电路如图2中所示。

Rg 对于大多数应用,出于经济性和简洁性考虑,导通和关断使用同样的无源栅极驱动电路。至少必须考虑串联Rg(栅极串联电阻)。这会限制最大Vdd电压时栅极驱动器需要的峰值驱动电流。Rg也可调整以限制漏极dV/dt。 此外,串联栅极电阻提高了MOSFET中的ESD(静电放电防护)能力,包括漏极端。 通常Rg的最小值通过希望的输出电流最大值来设定。在许多设计中,Rg大于此值,以调整导通时间或限制漏极dV/dt。 Doff和Rgoff 有时需要增加关断加速电路。这通常用于半桥应用,在半桥应用中,一个设备在导通前另外一个设备必须彻底关断,以避免图腾柱直通和/或允许上端MOSFET的有一定反向恢复时间。 Rgs(栅极至源极) Rgs称为栅极下拉电阻。许多商用低端栅极驱动器应用忽略Rgs。但好处是多方面的: 1) 地电压不稳定的应用容易出现一些故障,栅极至源极电阻可保护栅极开路。还会在上电时建立确定的状态,而此时控制信号可能仍处于未知状态。 (注意,在MOSFET栅极内部本身为开路时,这并不提供保护。) 2) 温和抑制栅极振铃,振铃是器件本身和用户布板造成的寄生电感引起。 对于用MOSFET做输出应用的的栅极驱动器,如常见的高压集成电路(HVIC),Rgs的值可能很低,从而使上端输出可能获得很大的静态电流。在MillerDrive®或复合应用输出中,双极性器件(IGBT,BJT等)提供高峰值电流,而上端MOSFET提供稳态输出电流。这会限制导通状态时Rgs的值,因此阻尼效果不大。某些栅极驱动器在输出和接地之间有内部电阻,如飞兆MillerDrive®拓扑。但是,这个电阻通常是100k,不足以减少许多应用中的栅极振铃。 在栅极振铃在区域II出现的设计中,漏极电压也可能振荡,导致热损耗增加,导通时间延长。但是,Rgs和Rg也会形成一个分压网络,从而降低导通状态中的最终栅极电压。因此Rgs通常需要>> Rg。 并联MOSFET栅极驱动中的Rgate和Rgs 在一个大电流栅极驱动器用于驱动多个MOSFET的设计中,使用独立栅极电阻(Rg)可改进并联MOSFET之间导通和关断时间匹配。这是因为Rg可以适用器件Vth中细微不同而带来的影响。此外,尽可能靠近每个器件的单独Rgs电阻可用于减少从由于PCB到不同的栅极走线长产生的杂散电感引起的栅极的温和振铃。 具有无源栅极网络的基本仿真 设计人员经常问“我应该使用哪种栅极驱动器”? 要回答这个问题,我们必须先问“您需要什么Rg和V”? 由于具有MillerDrive®的低端栅极驱动器的源极电阻较低,它们可以在Spice中建模(对于大多数应用)作为虚拟缓冲器,其中输出电阻主要由Rg定义。Spice参数可用于设置上升和下降时间,以及传导延迟(甚至是双通道器件中的传导不匹配。(请参阅图3)

当峰值栅极电流已知并且确定了栅极驱动器的总功耗后,设计人员即可选择器件与设计匹配。然后会考虑一些因素,如栅极驱动器输出源电阻、输入控制拓扑和输入逻辑电平,以匹配设计实施。然后可快速参考飞兆选型指南以选择合适的器件。可在以下网址找到: http://www.fairchildsemi.com/Assets/zSystem/documents/collateral/productOverview/High-Speed-Low-Side-Gate-Drivers-Product-Overview.pdf 可进行迭代建模,以调整有Rg串联的栅极驱动器的大致输出电阻。 布局思路 在实际布局中应注意导通和关断阶段的电流路径,包括MOSFET的电流路径。基本原理相当简单: 1) 栅极驱动器应放置在MOSFET附近。使用双通道器件时,这可能具有挑战性。 2) 集成栅极驱动器的Vdd引脚上的旁路电容为开通瞬间提供电流。这需要旁路电容靠近栅极驱动器并足以吸收导通时的电流尖峰。这些通常是具有低串联电阻的陶瓷电容。 3) Rg、Rgs、Doff和Rgoff需要紧密放置在MOSFET的附近。在驱动并联MOSFET的应用中,需要特别注意这一点。 4) 关断阶段将释放栅极和源极之间的电荷。通过栅极驱动器GND引脚的电流环路在回到源极终端需要从源极引脚单独提供电流路径,不能与源极端的大电流共路径。 5) 由于此紧密环路中有电流尖峰,布局时其他信号应远离栅极驱动器电路以避免受到耦合干扰。 6) 当开关频率很高并且辐射噪音需要注意时,栅极驱动器IN引脚的串联输入电阻能提供一定作用。 HVIC栅极驱动器对布局和元件值有相似要求。AN-6076,供高电压栅极驱动器IC使用的自举电路的设计和使用准则是可做为应用低侧栅极驱动器的良好参考。对于箝位感性负载,请参阅飞兆AN-6069,低端门极驱动器的应用和比较评价。 如果在电源开关电路、电机驱动和基本负载控制等应用中使用飞兆低压栅极驱动器、HVIC和MOSFET时有任何疑问,请联系当地飞兆代表。 |

网友评论