乘法器与调制器

发布时间:2013-9-10 14:22

发布者:eechina

|

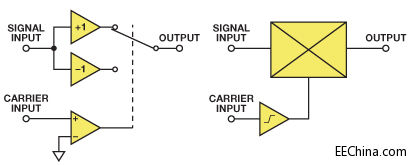

作者:ADI公司James Bryant 虽然许多有关调制的描述都将其描绘成一种乘法过程,但实际情况更为复杂。 首先,为清晰起见,若信号Acos)和未调制载波cos(ωt)施加于理想乘法器的两路输入,则我们将得到一个调制器。这是因为两个周期波形Ascos(ωst) 和 Accos(ωct)施加于乘法器(为便于分析,假定比例因子为1 V)输入端,产生的输出为: Vo(t) = ½AsAc[cos((ωs + ωc)t) + cos(ωs – ωc)t))] 若载波Accos(ωct)幅度为1 V (Ac = 1),则该式进一步简化为: Vo(t) = ½As[cos((ωs + ωc)t) + cos((ωs – ωc)t)] 但在大多数情况下,调制器是执行此功能更好的电路。调制器(用来改变频率的时候也称为混频器)与乘法器密切相关。乘法器的输出是其输入的瞬时积。调制器的输出是该调制器其中一路输入的信号(称为信号输入)和另一路输入的信号符号(称为载波输入)的瞬时积。图1所示为调制函数的两种建模方法:作为放大器使用,通过载波输入上的比较器输出切换正增益和负增益;或者作为乘法器使用,并在其载波输入和其中一个端口之间放置一个高增益限幅放大器。两种架构都可用来形成调制器,但开关放大器架构(用于AD630 平衡调制器中)运行较慢。大多数高速IC调制器含有一个跨导线性乘法器(基于吉尔伯特单元),并在载波路径上有一个限幅放大器,用来过驱其中一路输入。该限幅放大器可能具有高增益,允许低电平载波输入——或者具有低增益和干净的限幅特性,从而要求相对较大的载波输入以正常工作。详细信息请参考数据手册。

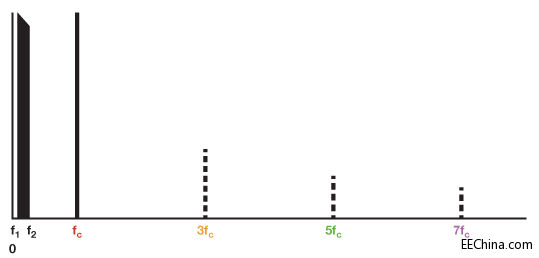

图1. 调制函数的两种建模方法 出于某些原因,我们使用调制器而非乘法器。乘法器的两个端口均为线性,因此载波输入的任何噪声或调制信号都会与信号输入相乘,降低输出;同时,大多数情况下可忽略调制器载波输入的幅度变动。二阶特性会导致载波输入的幅度噪声影响输出,但最好的调制器都会尽可能减少这种影响,因此不纳入本文的讨论范围。简单的调制器模型使用由载波驱动的开关。(理想)开路开关具有无限大的电阻和零热噪声电流,且(理想)闭路开关具有零电阻和零热噪声电压;因此,虽然调制器的开关并非理想,但相比乘法器而言,调制器依然具有较低的内部噪声。另外,比起乘法器,设计与制造类似的高性能、高频率调制器也更为简便。 与模拟乘法器相同,调制器将两路信号相乘;但与模拟乘法器不同的是,调制器的乘法运算是非线性的。当载波输入的极性为正时,信号输入乘以+1;而当极性为负时,则乘以–1。换言之,信号乘以载波频率下的方波。 频率为ωct 的方波可使用傅里叶序列的奇次谐波表示: K[cos(ωct) – 1/3cos(3ωct) + 1/5cos(5ωct) – 1/7cos(7ωct) + …] 对该序列求和:[+1, –1/3, +1/5, –1/7 + ...] 为 π/4。因此,K数值为4/π,这样当正直流信号施加到载波输入时,平衡调制器可作为单位增益放大器使用。 载波幅度并不重要,只要它足够大,可驱动限幅放大器即可;因此,由信号Ascos(ωst)和载波 cos(ωct)驱动的调制器产生的输出即为信号与载波平方的乘积: 2As/π[cos(ωs + ωc)t + cos(ωs – ωc)t – 1/3{cos(ωs + 3ωc)t + cos(ωs – 3ωc)t} + 1/5{cos(ωs + 5ωc)t + cos(ωs – 5ωc)t} – 1/7{cos(ωs + 7ωc)t + cos(ωs – 7ωc)t} + …] 该输出包含下列项的频率之和与频率之差:信号与载波、信号与载波的所有奇次谐波。理想的完美平衡调制器中不存在偶次谐波乘积。然而在真实调制器中,载波端口的残余失调会导致低电平偶次谐波乘积。在许多应用中,低通滤波器(LPF)可滤除高次谐波乘积项。请记住,cos(A) = cos(–A), 因此 cos(ωm – Nωc)t = cos(Nωc – ωm)t,并且无需担心“负”频率。滤波处理后,调制器输出可计算如下: 2As/π[cos(ωs + ωc)t + cos(ωs – ωc)t] 它和乘法器输出的表达式一致,只是增益稍有不同。在实际系统中,增益采用放大器或衰减器进行归一化,因此此处无需考虑不同系统的理论增益。 在简单的应用中,显然使用调制器优于使用乘法器,但如何定义“简单”?调制器用作混频器时,信号和载波输入分别为频率等于f1 和 fc的简单正弦波,未经滤波处理的输出包含频率和 (f1 + fc) 与频率差 (f1 – fc) ,以及信号与载波奇次谐波的频率和与频率差 (f1 + 3fc), (f1 – 3fc), (f1 + 5fc), (f1 – 5fc), (f1 + 7fc), (f1 – 7fc)。经LPF滤波之后,预计仅得到基波项 (f1 +fc) 和 (f1 –fc)。 然而,若 (f1 + fc) > (f1 – 3fc),将无法使用简单的LPF区分基波与谐波项,因为某个谐波项的频率低于某个基波项。这并非属于简单的情况,因此需进一步分析。 如果假设信号包含单一频率f1,或假设信号更复杂,分布在频段f1至 f2中,则我们便可分析调制器的输出频谱,如下图所示。假设完美平衡的调制器不存在信号泄漏、载波泄漏或失真,则输出不含输入项、载波项和杂散项。输入以黑色表示(或在输出图中以浅灰色表示,哪怕实际上并不存在)。 图2显示输入—位于 f1 至 f2 频段内的信号,以及频率为 fc的载波。乘法器不含下列奇次载波谐波:1/3(3fc), 1/5(5fc), 1/7(7fc)…,以虚线表示。请注意,小数1/3、1/5和1/7表示幅度,而非频率。

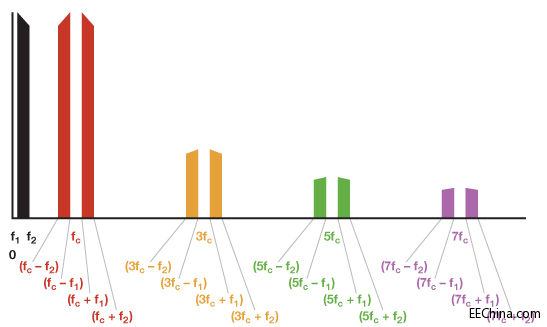

图2. 输入频谱,显示信号输入、载波和奇次载波谐波 图3显示乘法器或调制器的输出,以及截止频率为2fc的LPF。

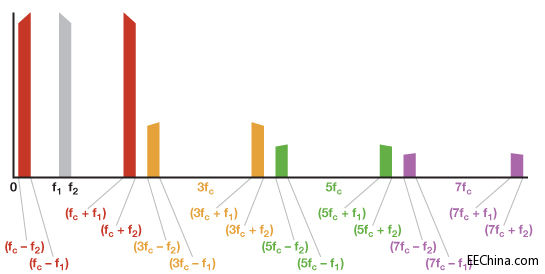

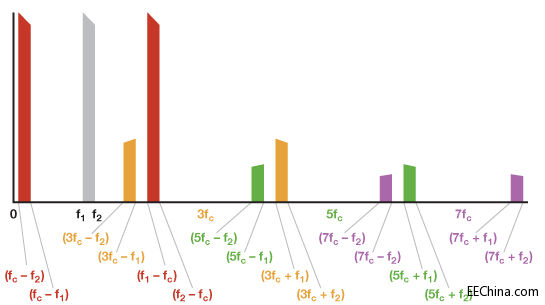

图3. 使用LPF的乘法器或调制器输出频谱 图4显示未经滤波处理的调制器输出(但不含7fc以上的谐波项)。

图4. 未经滤波处理的调制器输出频谱 若信号频带f1 至 f2位于奈奎斯特频带(直流至 fc/2)内,则截止频率高于2fc的LPF将使调制器具有与乘法器相同的输出频谱。若信号频率高于奈奎斯特频率,则情况更复杂。 图5显示信号频带正好低于fc时将发生的情况。依然有可能分离谐波项和基波项,但此时需使用具有陡峭滚降特性的LPF。

图5. 信号大于fc/2时的输出频谱 图6显示由于fc位于信号通带内,谐波项叠加 (3fc – f1) < (fc + f1),因此,基波项不再能够通过LPF与谐波项分离。所需信号此时必须通过带通滤波器(BPF)进行选择。 所以,虽然调制器在大部分变频应用中优于线性乘法器,但设计实际系统时必须考虑到它们的谐波项。

图6. 信号超过fc时的输出频谱 参考文献 Analog Dialogue Brandon, David. “Multichannel DDS Enables Phase-Coherent FSK Modulation.” Analog Dialogue, Volume 44, Number 4, 2010. Gilbert, Barrie. “Considering Multipliers (Part 1).” Analog Dialogue, Volume 42, Number 4, 2008. Product Pages Mixers/Multipliers Multipliers/Dividers Modulators/Demodulators RAQs Multipliers and Modulators Caveat Emptor Tutorials MT-079: Analog Multipliers MT-080: Mixers and Modulators 作者简介 James Bryant [james@jbryant.eu] 从1982年起担任ADI公司欧洲地区的应用经理。他拥有英国利兹大学的物理学和哲学学位,他还是注册工程师(C.Eng.)、欧洲注册工程师(Eur.Eng.)、电机工程师协会会员(MIEE)以及对外广播新闻处(FBIS)会员。除了热情钻研工程学外,他还是一名无线电爱好者,他的呼叫代号是G4CLF。 |

网友评论