Silicon Labs推出业界最低抖动且完全兼容同步以太网标准的时钟

发布时间:2013-8-19 11:44

发布者:eechina

|

新型Si5328精确时钟倍频器和抖动衰减器显著降低电信级以太网交换机和路由器成本和复杂度 Silicon Labs(芯科实验室有限公司)今日宣布针对基于同步以太网(SyncE)标准的高速网络设备推出业界最低抖动、最低功耗和最高频率灵活性的定时解决方案。通过提供任意频率合成和行业领先抖动性能(263fs RMS)的组合优势,新型Si5328精确时钟倍频器和抖动衰减器能够满足电信级以太网交换机和路由器对超低功耗物理层参考时钟的需求。与竞争对手SyncE时钟产品相比,Si5328的尺寸和功耗都减少了80%以上,这为业界提供了同类产品中最佳的兼容SyncE标准的定时解决方案,非常适用于边缘路由器、多业务交换机、无线回程系统、数字用户线路接入复用器(DSLAM)和GPON/GEPON光线路终端(OLT)设备等。

电信基础设施市场正迅速从传统的同步光纤网络/同步数字层级网络(SONET/SDH)过渡到更高速度、更符合成本效益的以太网。网络过渡背后的关键实施技术是同步以太网,它被用在千兆以太网(GbE)、10GbE、40GbE和100GbE电信级以太网交换机和路由器中分配精确时钟。每个电信级以太网交换机和路由器都需要一个高性能的同步以太网时钟去提供漂移滤波、分配时钟,以及提供低抖动以太网物理层参考时钟。Silicon Labs拥有针对以太网物理层需求(速度从GbE到100GbE)而优化设计的业界最低抖动、最高频率灵活性的SyncE定时解决方案,可完全满足这类应用需求。

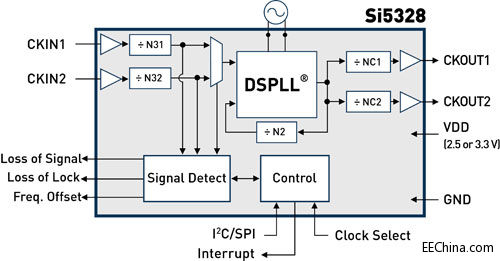

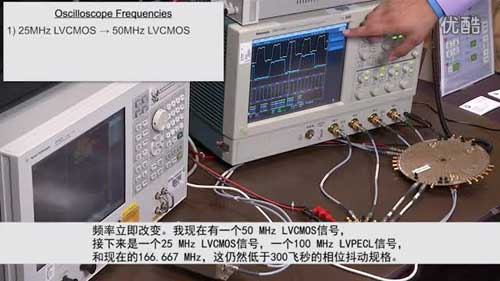

Si5328完全兼容ITU-T G.8262 SyncE时钟要求,包括EEC的选项1和2。当搭配3级温度补偿晶体振荡器(TCXO)时,Si5328满足SyncE标准中对抖动、漂移和保持特性的所有要求。凭借片内集成的具有可选择环路带宽(0.1Hz和1-10Hz)的环路滤波器,Si5328可用于任何需要遵循SyncE标准的网络系统。这种集成特性省去一些昂贵的分立定时板卡锁相环(PLL),并且确保制造商的网络产品能够部署到世界各地的终端客户中。 利用Silicon Labs专利的DSPLL®技术,Si5328 SyncE时钟能够从任意8kHz-710MHz输入频率中生成任意8kHz-808MHz输出频率。这种特有的频率灵活性和任意速率能力使得网络系统设计人员能够同步和生成几乎所有传统电信或SyncE的频率,简化了从GbE到100GbE的系统设计。Si5328可以通过I2C或SPI接口重新进行数字化配置,无需增加BOM成本。 高集成度Si5328时钟单芯片极大的简化了PCB设计,其DSPLL架构消除了片外晶体和环路滤波器件,减少了PCB面积,同时也最大限度的提高了板级噪声抑制能力。此外,Si5328可选择的输出信号格式(LVPECL、LVDS、CML和CMOS)可轻松连接到主流的以太网收发器接口,节省了昂贵的电平转换器和其他滤波器件。通过采用单一2.5V或3.3V供电,Si5328不再需要竞争对手SyncE定时解决方案中通常所需的多电源和分立滤波电路。 Silicon Labs副总裁兼定时产品线总经理Mike Petrowski指出:“随着当今电信基础设施迅速从传统标准转向SyncE,设备制造商需要完全符合SyncE标准的时钟解决方案,它不仅要提供低抖动性能,同时也要降低设计的复杂性和功耗。 Silicon Labs新型Si5328时钟倍频器提供了最先进的SyncE定时解决方案,在抖动性能、BOM成本、封装和功耗方面,为设计人员提供了无与伦比的设计裕量。” 价格和供货 Silicon Labs的SyncE Si5328时钟现已量产,支持紧凑型6毫米x 6毫米QFN包装,包括两个速度等级。Si5328C-C-GM支持最大346MHz时钟频率输出,在1万颗采购量时,单价为7.50美元。Si5328B-C-GM支持最大808MHz时钟频率输出,在1万颗采购量时,单价为9.38美元。Silicon Labs也提供了易于使用的评估平台以加速SyncE应用开发。Si5328-EVB评估板价格为每套250美元。 更多有关Silicon Labs Si5328 SyncE时钟倍频器和抖动衰减器的信息,或者订购样片和评估板,请浏览网站:www.silabs.com/timing。 关于Silicon Labs定时IC产品系列 Silicon Labs提供业界最完整的“一站式”定时IC产品组合,包括可编程XO/VCXO、基于CMEMS®技术的单晶片MEMS振荡器、频率灵活的时钟发生器、抖动衰减时钟、PCIe时钟、缓冲器和物理层定时器件。凭借Silicon Labs专利的DSPLL和MultiSynth技术,这些定时IC省去了许多昂贵的片外分立器件,同时提高了性能、最大限度的减少了电路板空间和设计复杂度。为帮助开发人员缩短产品上市时间,Silicon Labs还提供了易于使用的网络工具,允许用户定制振荡器和时钟发生器。定时IC样片可在两周内交付,消除了定制器件交付时间较长的问题。 |

网友评论