利用FPGA简化3GPP-LTE基带开发

发布时间:2010-4-8 16:29

发布者:嵌入式公社

|

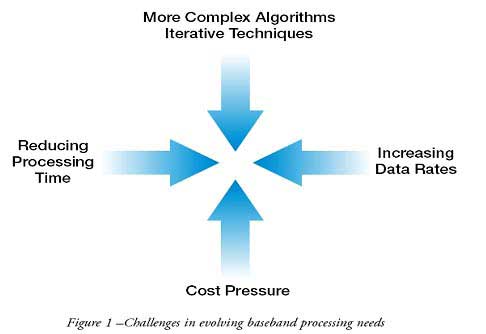

基带处理信号通道是设计人员面临的最大挑战,但同时,它也为实现基站收发信台的创新提供了绝佳机会。因此,目前其已然成为OEM厂商实现产品差异化的关键。随着人们逐步认识到,许多针对之前2G和3G系统的技术将无法满足3GPP LTE,即第4代无线技术的性能和延迟要求,基带架构设计领域的竞争也开始愈演愈烈。 处理通道不仅需要比以往强大得多的处理能力,而且所有功能必须在更短的时间内完成。要想解决系统架构师所面临的一系列挑战,就要开发一个系统,来满足运营商积极的投资和运营成本削减目标。图1显示了基带处理系统设计面临的主要压力。 基于FPGA的解决方案可以满足上述要求,同时还能避免常见的性能问题和瓶颈。很多公司正在实施类似计划,如赛灵思最新推出的LTE上行链路通道解码器和LTE下行链路通道编码器LogiCORE,希望通过在单一IP解决方案中纳入多种关键的 Layer-1功能,来消除FPGA普及道路上的种种障碍。 硅技术的进步是无线通信技术能够取得成功的关键,因为它可以将甚至更复杂的算法技巧从实验室带到实际产品中得以推广。例如3G网络中Turbo迭代码纠错技术,在10年内完成了从最初发现到商业化推广的整个过程。创新步伐始终都在持续加快,最为引人注目的是通过各种MIMO天线技术将空间维度(spatial dimension)概念应用到无线通信网络中。 但是,随着4G空中接口的出现,压力不断增加,以至于传统的以DSP为中心的可编程通道卡架构难以应对。FPGA和DSP之间的传统分割遭遇了性能瓶颈,这种制约的影响很大,因为二者之间需要传输的数据量非常大。 那么,我们如何才能消除类似瓶颈?关键在于简化Layer-1系统架构,并消除芯片间所有不必要的数据传输。这样的简化流程会引发一些与基于DSP的架构可扩展性有关的问题。设计人员需要IP、软件和技术支持等更强大的组合,来帮助他们完成向Layer-1系统架构的转变,在这其中,多数功能都在可编程的硬件环境中实现而非DSP。 简化Layer-1设计 让我们更深入分析一下将FPGA单纯用作协处理器,从DSP处理器卸载Turbo解码功能时可能发生的问题。在一个典型的LTE基带设计(如图2)中分析这种分区的有效性时,赛灵思的系统架构师们发现,仅仅是通过SRIO连接将数据从DSP处理器转移到FPGA后再返回,就会占用可用延时预算中超过20%的资源。令人震惊的是,这还不是最坏的情况。如果加上使用更高调制方法(如64-QAM) 编码、1/3码率20MHz LTE频段下的2个MIMO代码字等混合数据,这一比例会迅速提升,从而使情况恶化。 一种应对办法就是简单地添加更大型的“管道”,部署更多高速的千兆位收发器进行数据传输。虽然以这种方式构建系统完全可行,但它会导致系统功耗不必要的增加,因为这种情况下需要相对比较消耗功率的高速串行连接来回传送数据,而且桥接功能是重复的,因此需要更多硬件资源。 还有一种更为理想的较好解决方案。通过将Layer-1的大部分功能整合到FPGA中,设计人员就可以避免不必要的开销,节省的资源可以用来提高系统吞吐量、缩短延迟,同时降低功耗。仅降低功耗这一项就可以直接转变为系统可靠性提升、成本降低,以及运营成本的节省。 这种架构方法完全消除了对 DSP的需要——当然,如果设计人员愿意的话,也可以加入DSP来执行一些低速率功能。利用这种划分方法,FPGA实现了整个Layer-1基带处理功能,将MAC和HARQ处理等其它较高层的功能留给了更具成本效益的通用处理器或网络处理器——这些处理器也可以处理额外的回传连接功能。将所有高性能、对时间要求严格的功能集成到单一平台上,FPGA有效地避开了延迟和带宽局限;同时,分区也变成了一项简单得多的任务。 迄今为止,采用这种方法的主要障碍是对简化流程(从设计概念到硬件)的需求。此外,对已经习惯以DSP为中心设计流程的设计人员来说,他们需要IP和开发工具的帮助才能更容易地利用FPGA的强大功能,并在其中迅速高效地开发基带功能。 赛灵思的LTE上行链路通道解码器和LTE下行链路通道编码器LogiCORE,可以消除设计人员在考虑采用FPGA时的顾虑,因为它可以将多种关键的Layer-1功能集成到单一IP解决方案中,而这个解决方案可以通过Xilinx CORE Generator工具中的图形用户界面进行灵活定制。利用这种设计流程,对FPGA了解有限的工程师们就可以将精力集中于更广泛的系统设计,从而大大减轻开发和集成的工作量。 未来发展方向 快速、低延迟连接是LTE的关键要求,而且在超4G的时代将依然如此。随着这些以数据为中心的无线系统的演进,许多采用传统DSP和FPGA分区方法的公司将发现,在不同芯片间传输数据的开销高得难以接受。对于希望在产品设计中寻求额外优势的设计人员来说,他们可以更轻松地使用基于FPGA的解决方案。摆脱了传统系统设计方法束缚的工程师,将开发出崭新的产品,远离那些将继续困扰竞争对手的性能问题和开发瓶颈。

F1: 不断演进的基带处理需求带来的挑战

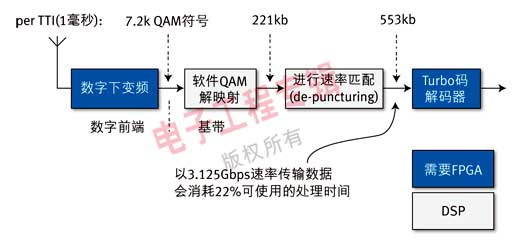

F2: 在典型LTE系统中,在FPGA和DSP间传输数据所需要的速率 LogiCOREs 内部 赛灵思最近推出的LTE通道编码器和解码器LogiCOREs是专为3GPP rel8 E-UTRA eNB基带处理设计的,符合3GPP TS 36.211 v8.2.0和TS 36.212 v8.2.0(2008-03)规范。它们将支持带宽高达20 MHz、采用普通(短)CP、64-QAM调制技术和两个MIMO代码字的不同配置。这两种产品都可以处理FDD和TDD帧结构,因此非常适合从TD- SCDMA标准演进而来的系统。 这种编码器和解码器都作为独立的参数化IP块提供,可以通过Coregen软件工具轻松集成到客户的设计中。为了简化设计集成,赛灵思可以为它们提供全面的测试、模拟和C模型,帮助完成系统模拟。 有关新的 LogiCORES的更多详尽信息可从赛灵思IP中心(www.xilinx.com/ipcenter)获取。设计人员可以从Wireless End-Market网页(www.xilinx.com/esp/wireless)上查看更多无线参考设计和解决方案。 作者:赛灵思公司无线产品营销高级经理David Nicklin,2009年06月 |

网友评论