博客

项目01的cpu子板

|

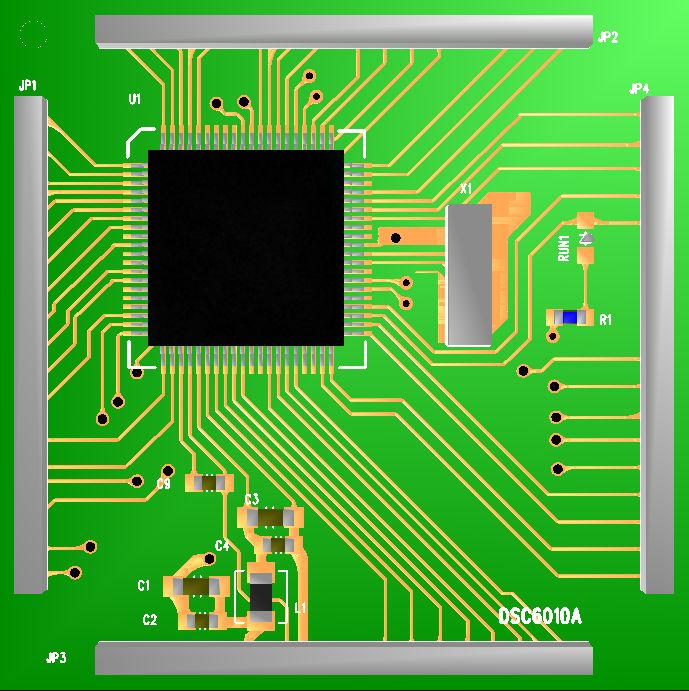

为了保证设计的灵活性,在项目01中广泛采用了子板设计,包括通信子板和cpu子板及其他一些功能板。当然,通信子板和其他功能板都有现成的产品,不用我在从头开始,但是CPU子板是没有的。

用了两天的时间,把cpu的资源划分了一下,幸运的是,cpu的80个管脚绝对可以满足项目需求,不幸的是,嗯,想把这80个管脚引出来还真是麻烦。

好在不用画封装,只管调用公司现有的设计库就可以了,省去了不少功夫。

用了大半天的时间,把子板设计好了,心得就是:如果对单片机各个引脚的功能都有一个清晰的认识的话,可以显著降低画板的难度。要知道,虽然画板只用了10多个小时,可是用着思考管脚功能定义上的时间可是整整两天呢,因为既要保证将功能一致的管脚集中起来,还要保留充分的灵活性。正所谓磨刀不误砍柴工。

看我画的板子,还说得过去吧。JP1、JP2是数字量输入输出;JP4是通讯;JP3是AD采样和程序调试口。

嗯,反正自己很满意,吃饭去了。

用了两天的时间,把cpu的资源划分了一下,幸运的是,cpu的80个管脚绝对可以满足项目需求,不幸的是,嗯,想把这80个管脚引出来还真是麻烦。

好在不用画封装,只管调用公司现有的设计库就可以了,省去了不少功夫。

用了大半天的时间,把子板设计好了,心得就是:如果对单片机各个引脚的功能都有一个清晰的认识的话,可以显著降低画板的难度。要知道,虽然画板只用了10多个小时,可是用着思考管脚功能定义上的时间可是整整两天呢,因为既要保证将功能一致的管脚集中起来,还要保留充分的灵活性。正所谓磨刀不误砍柴工。

看我画的板子,还说得过去吧。JP1、JP2是数字量输入输出;JP4是通讯;JP3是AD采样和程序调试口。

嗯,反正自己很满意,吃饭去了。

全部作者的其他最新博客

- • 辛苦多日,终于有了成果

- • 第一次当HR

- • 板子好难画

- • 看来大家都不喜欢纯技术型的日志

- • 项目01的总体方案