博客

一个SDRAM的乒乓操作

|

-------------------------------------------------------------------编写者:禾木

很多论文做图像操作都要两个独立通道的sdram的操作。

但是从产品角度看来,第一个:两个sdram 会增加fpga的引脚分配的困难性。第二个两个sdram导致成本更高。

本文章提出一种单个sdram的乒乓操作。不过这个需要满足以下条件才能使用。

1. 输入和输出SDRAM的两个总数据带宽是sdram的读写操作带宽的80%以下。超过了该数据带宽会导致sdram无法及时切换读写。这个计算方法要考虑sdram的位数,和输入,输出的数据位数,时钟。占空比。

比如,一端输入的是PAL的CCIR656数据,格式为YCbCr,4:2:2格式,时钟为27MHz,位数为8位。由于4:2:2格式,格式为Cb Y Cr。格式中表示,Y和色差信号要两个时钟周期才能到达,所以CCIR的数据带宽为13.5M*16位,经过4:4:4插值算法后,带宽变成13.5M*32位。

另外一端的输出为RGB 800*600 @75Hz。时钟为49.5Mhz,所以带宽为54M*32位。

上述两个加起来就是63M。而sdram的时钟是120MHz,带宽为120M*32。明显可以满足该要求。

2.输入和输出数据必须同时,而且切换sdram的区需要同时。乒乓操作的意思就是一个读,另外一个在写。但不能同时读写在一个区,否则会覆盖以前的内容。

如果sdram的带bank区,在时间1内可以在bank0区写入数据,而bank1读取数据。在时间2内,读bank0,写bank1的。也可以直接使用行地址切换,因为bank区切换不需要Trow切换时间。而row切换需要时间。

上述的例子中,PAL的帧率为25HZ,VGA输出为75HZ,VGA是PAL的倍数关系,不需要增加额外的帧内容。PAL在BANK0-BANK1区域写入奇偶完整一帧,VGA在bank1-bank0区已经读了三次内容。VGA读完完成以后,切换BANK区域。

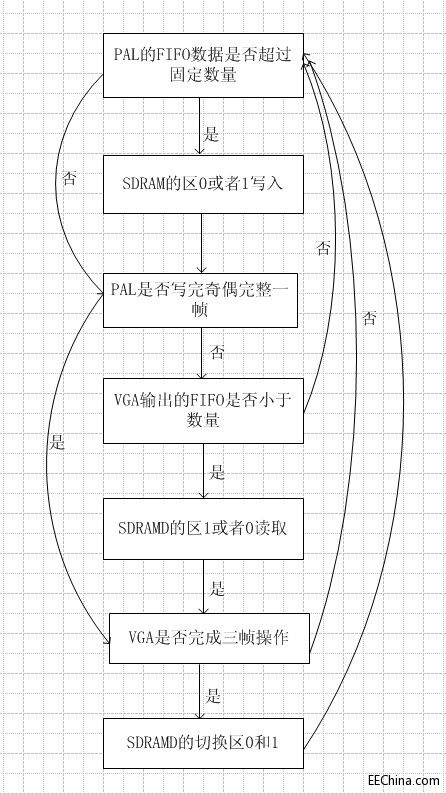

用一个SDRAM的过程,用 以下的流程图表示。

跟两个单独的SDRAM操作不同在于,读写操作不能只等待一个过程,需要及时操作。发现PAL的输入的FIFO满足以后,马上写入数据,如果不满足判断vga输出fifo是否少了固定的数据,是的情况写入固定的数据。

再给大家找个实际工程项目。有个LED的DVI发送卡,选型了选了赛灵思的SPARTAN-6的芯片FT256封装的。因为DVI需要10位的支持,所以导致两个SDRAM不能单独通道。后来把两个SDRAM的地址和命令的线共用,而数据线是分离的。也就是说两个SDRAM的并成一个大的SDRAM的,数据位数为64位。

该工程中,输入数据为DVI数据,带宽最大为108*32b,而输出为两个以太网口125*8*2,也就是62.5M*32b。因为SDRAM的总线是64位,所以SDRAM带宽为250M*32,是可以满足上述要求。

需要上述两个项目,可以申请我个人设计开发板,支持两个单独的SDRAM的。代码是有两个独立SDRAM和单个SDRAM的。