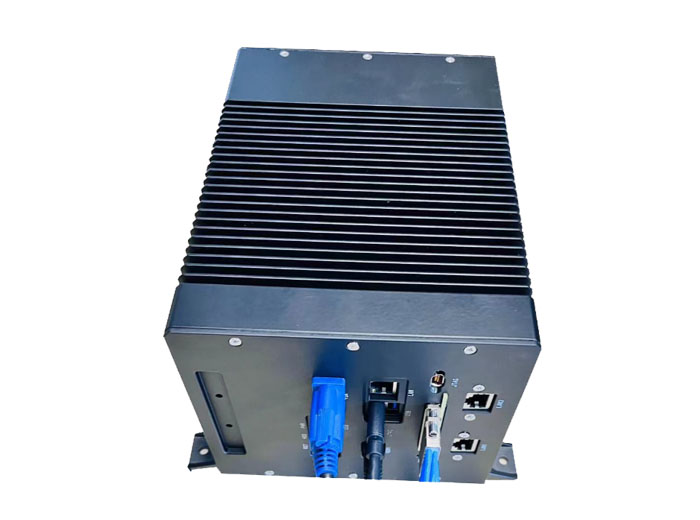

一、产品概述 设备基于3U VPX的导冷结构,集成FPGA接口预处理卡,GPU板卡、飞腾ARM处理卡,实现光纤、差分电口或者Camera link的图像接入,FPGA信号预处理,GPU AI计算,飞腾ARM的采集管理存储。 二、系统组成 系统组成包括:3U VPX机箱电源、3U VPX背板、 1块3U VPX V7采集处理板、1块3U VPX AGX orin GPU计算主板、1块3U VPX飞腾处理器计算板。

2.1基于XC7V690T的3U VPX信号处理板(274)

本板卡系我司自主研发的基于3U VPX导冷架构的信号处理板,适用于高速图像处理等。芯片采用工业级设计。该处理板包含1片Xilinx公司的Virtex7系列FPGA-XC7V690T-2FFG1761I。板载两组64位宽DDR3,每组容量4GB,一个HPC FMC接口。VPX接口连接4组x4 GTH,24组LVDS,一路RS422,一路1000Base-T。板卡的电气与机械设计依据VPX标准(VITA 46.0),支持导冷,能够满足用户在特殊环境下的使用需求。

板卡功能 | 参数内容 | 主处理器 | Xilinx XC7V690T-2FFG1761I | 板卡标准 | VPX VITA 46.0 | 电气规范 | PCIe 2.0,3.0 X4 | FMC接口 | FMC ANSI/VITA 57.1 – 2008 ,ASP-134486-01

HPC中LA,HA,HB全部接口和DP0~DP7 8路高速接口 | 板载缓存 | 两组DDR3,每组512Mx64bit(4GB), MT41K512M8RH-125-IT | 加载Flash | BPI加载模式,BPI Flash 2Gb | VPX接口 | P1: GTX x16, 支持PCIe、SRIO协议

P2: LVDS x24,一路RS422,一路1000Base-T | 仿真器接口 | 1x 6Pin JTAG接口,间距2.54mm | LED | 两个,电源状态指示灯,FPGA状态指示灯(可编程) | 复位方式 | 外复位 | 板卡尺寸 | 100mm x 160mm x20mm | 板卡重量 | (含散热片) | 板卡供电 | +12V@4A | 板卡功耗 | 48W | 工作温度 | Industrial -20℃到+70℃ |

光纤收发子卡、2711子卡、Cameralink子卡

2.2 基于3U VPX的AGX Orin GPU计算主板(735)

Jetson AGX Orin 采用 NVIDIA Ampere 架构 GPU 和 Arm Cortex-A78AE CPU,以及新一代深度学习和视觉加速器。高速 IO、204GB/s 的内存带宽以及 32GB 的 DRAM 能够馈送多个并发 AI 应用程序管道。采用 Jetson AGX Orin,您现在可以部署更大型、更复杂的模型,解决自然语言理解、3D 感知和多传感器融合等问题。Jetson Orin算力高达275 TOPS,是上一代多个并发 AI推理管道性能的8倍,加上支持多个传感器高速接口,可为新时代机器人提供理想的解决方案. GPU | 2048-core NVIDIA Ampere architecture GPU with

64 Tensor Cores | CPU | 12-core Arm Cortex-A78AE v8.2 64-bit CPU

3MB L2 + 6MB L3 | 显存 | 64GB 256-bit LPDDR5 204.8GB/s | 存储 | 64GB eMMC 5.1 | DLA最大频率 | 1.6 GHz | AI性能 | 275 TOPS | DL加速器 | 2x NVDLA v2 | 视频加速器 | 1x PVA v2 | 视频编码 | 2x 4K60 (H.265), 4x 4K30 (H.265)

8x 1080p60 (H.265), 16x 1080p30 (H.265) | 视频解码 | 1x 8K30 (H.265), 3x 4K60 (H.265), 7x 4K30 (H.265)

11x 1080p60 (H.265),22x 1080p30 (H.265) | PCle | x8 PCle Gen4 | 显示接口 | HDMI | 网络 | RJ45 接口 (高达1 GbE) |

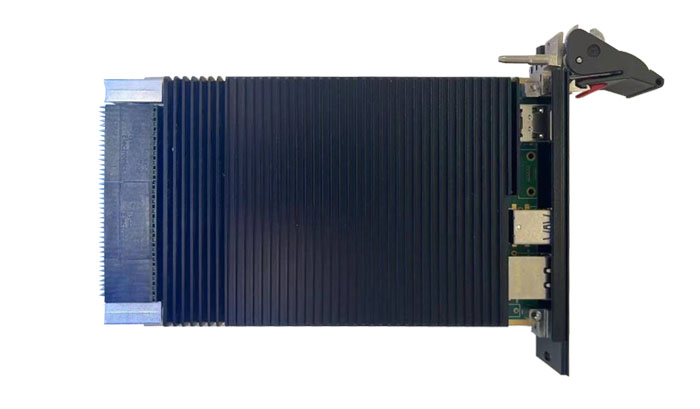

2.3 3U VPX飞腾处理器刀片计算机

2.3.1 产品概述 该产品是一款基于国产飞腾FT2000 4核或腾锐D2000 8核的高性能3U VPX刀片式计算机。产品提供了4个x4 PCIe 3.0总线接口,同时可配置为1个x16或2个x8 PCIe3.0接口,因此具有很强的扩展性,极大地满足多负载多节点的应用需求。产品结构完全符合VITA 46.0规范,有很强的可靠性、可维护性、可管理性,并与军用计算机的抗振动、抗冲击、抗宽温环境急剧变化等恶劣环境特性进行完美融合。 2.3.2 功能指标 ● 3U 5HP VPX规格。 ● 支持FT-2000/4 四核处理器和腾锐D2000 八核处理器 FT-2000/4标准版,2.6GHz,16W 腾锐D2000/8标准版,2.3GHz,25W ● 板载16GB双通道DDR4内存,频率2400MHz。 ● 支持2个VGA接口,最大分辨率1920x1080@60Hz;其中1路VGA为后出接口。 ● 支持4个x4 PCIe3.0接口,可配置成1个x16 PCIe 3.0或2个x8 PCIe 3.0。 ● 前面板支持1路10/100/1000Mbps网络接口,后出2路10/100/1000Mbps网络信号,其中1路后出网口与前面板网口二选一切换。 ● 板载1个mSATA接口,支持SATA3.0;后出2路SATA3.0信号,用于扩展存储。 ● 前面板支持2个USB3.0接口;后出2路USB3.0接口信号。 ● 提供2路RS232后出串口,其中1路可选RS422/RS485模式。 ● 提供1路RS232后出CPU管理串口。 ● 前面板带复位按键和LED指示灯。 ● 单板管理功能(可选功能)。 ● 支持银河麒麟、UOS、Centos、ubuntu、VxWorks系统。 (本项目使用ubuntu操作系统) 三、软件开发内容

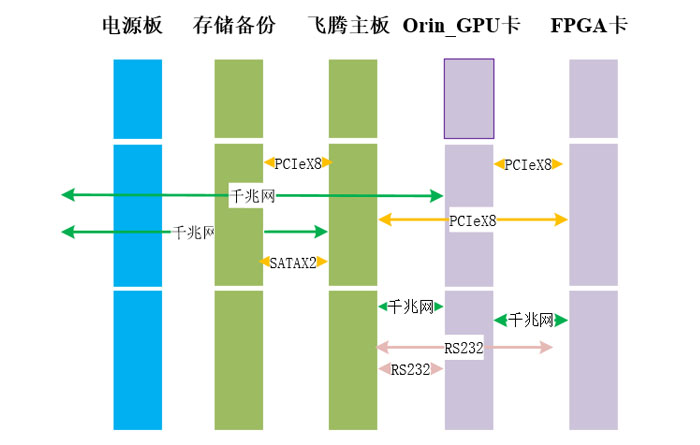

3.1光纤收发整体流程设计 2路QSFP+光纤接口,一路作为发送端口,一路作为接收端口,每路接口作为4个X1通道互不影响。 接收端:数据流从光纤接收端进来,存到FPGA的DDR中,然后通过PCIE导入到GPU中。 发送端:数据存在飞腾主板中,飞腾通过PCIE写入FPGA的DDR中,FPGA取走数据,通过光纤发送端口发送出去。 GPU接收的数据通过千兆网发送到飞腾主板中。

3.2 TLK2711收发整体流程设计

4路TLK2711接口,2路作为发送端口,2路作为接收端口,每路接口互不影响。 接收端:数据流从TLK2711接收端进来,存到FPGA的DDR中,然后通过PCIE导入到GPU中。 发送端:数据存在飞腾主板中,飞腾通过PCIE写入FPGA的DDR中,FPGA取走数据,通过TLK2711发送端口发送出去。 GPU接收的数据通过千兆网发送到飞腾主板中。

3.3 FPGA流程框架 如图所示,FPGA程序可以大体划分为PCIe端点控制器XDMA、DDR3读写控制以及TLK2711收发控制三部分。FPGA与PC的PCIe通信采用Xilinx的XDMA IP,逻辑模块间采用AXI总线互联方式。XDMA0数据链路为飞腾主板主控数据链路,XDMA1数据链路为Orin_GPU卡主控数据链路。 Orin_GPU卡主控数据链路:tlk2711子卡的接收端口接收到图像数据缓存到第一组ddr3中,大小为4GB,对0-4GB的ddr3空间读写,gpu把图像数据读出并作处理。链路数据流向分为数据发送(FPGA-PC)(这里飞腾主板和Orin_GPU卡都称为PC): 数据接收过程描述(FPGA-PC):图像数据以1.6Gbps线速率通过rxp接口,wr_fifo把16bit数据位宽转化为128bit数据位宽,fdma_ctrl的写ddr3模块把数据写入到0-4GB的地址空间,通过定义的寄存器信号告诉主机软件取出对应地址空间的数据,通过dma的C2H通道直接写入主机内存。 飞腾主板主控数据链路:飞腾主板把图像处理结果写入板卡第二组ddr3中,fpga逻辑读出ddr3中的数据通过tlk2711子卡的发送端口发送出去。(这里飞腾主板和Orin_GPU卡都称为PC)。 数据发送过程描述(PC-FPGA):为了实现数据发送,主机软件从主机内存固定位置读出图像处理数据发送到DMA的H2C通道,写入到板载第二组DDR3的0-4GB的空间,主机软件通过寄存器通知fdma_ctrl的读ddr3模块取出对应地址ddr3的数据,通过rd_fifo把数据128bit位宽变化到16bit后,给到tlk2711子卡的发送模块,最后数据以1.6Gbps的线速率通过txp口发送出去。

3.4 软件PCIE读流程 软件启动开始接收,软件通过寄存器使能FPGA开始接收数据(光纤或者TLK2711数据),软件开始轮询FPGA写入完成寄存器,当读到FPGA完成标志,说明FPGA已经写入数据,软件读取DDR中数据,完成一次读取数据交互流程。 之后重复单次流程,直到数据接收完整。

3.5 软件PCIE写流程 软件启动开始发送数据(光纤或者TLK2711数据),软件把数据写入DDR中, 通过寄存器使能FPGA开始发送,软件开始轮询FPGA读取完成寄存器,当读到FPGA完成标志,说明FPGA已经把DDR的数据取走,这样就完成一次写入数据交互流程。之后重复单次流程,直到数据发送完整。

3.6飞腾GPU数据交互 在背板设计中,飞腾主板和GPU千兆网互联和RS232互联。考虑传输速度,使用千兆网进行传输。使用TCP/IP协议,飞腾处理器为TCP服务端,GPU为TCP客户端主动进行链接请求。 3.7 客户端界面 客户端具有状态信息显示,控制四通道光纤数据发送或者双通道TLK2711接口数据发生功能。上位机自动识别FPGA子卡类型,切换操作界面。 四通道光纤子卡界面 双通道TLK2711子卡界面

|