博客

modulesim仿真clk周期与testbench程序设置不一致问题-并行块与串行块

||

问题:

#5 clk=!clk;

#10 Rsetn=1;

end

begin-end是串行块,串行块中的语句顺序执行,执行了5+10=15个周期以后clk的值才会更新,所以才会有300ns的clk周期出现。用fork-jion并行块就没问题了。

请教:testbench的时钟周期跟modelsim仿真的时钟周期不一致问题。

我的tesbench是这样写的,

`timescale 10 ns/ 1 ns

module digital_led_test();

reg Rsetn;

reg clk;

wire [7:0] CODE;

wire [1:0] L_EN;

digital_led i1 (

.CODE(CODE),

.L_EN(L_EN),

.Rsetn(Rsetn),

.clk(clk)

);

initial

begin

clk=0;

Rsetn=0;

end

initial

begin

$display("\tclk,\tRsetn,\tCODE[7:0],");

$monitor("\t%b,\t%b,\t%d",clk,Rsetn,CODE[7:0]);

end

always

begin

#5 clk=!clk;

#10 Rsetn=1;

end

endmodule

我的原意是是输出每5个周期(5*10ns=50ns)翻转一次,那么一个时钟周期应该是100ns。

但是modelsim仿真出的clk的波形周期却和我原意不一样。

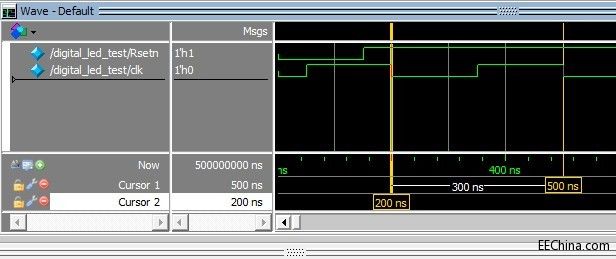

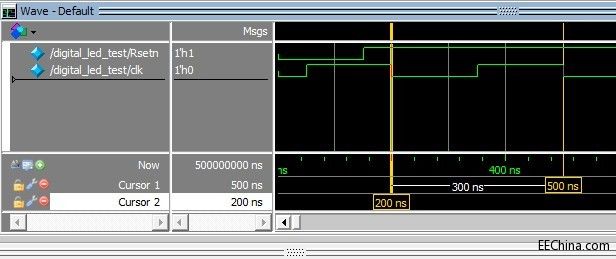

下面是用modelsim仿真的波形。

modelsim仿真理论上不太可能出错,那么就是我前面的计算方法有问题,可能是我理解的问题。

请各位大神指教我前面的计算方法哪里出错了,新手,要是问的太低级还请见谅,不吝赐教!先谢过!

我的tesbench是这样写的,

`timescale 10 ns/ 1 ns

module digital_led_test();

reg Rsetn;

reg clk;

wire [7:0] CODE;

wire [1:0] L_EN;

digital_led i1 (

.CODE(CODE),

.L_EN(L_EN),

.Rsetn(Rsetn),

.clk(clk)

);

initial

begin

clk=0;

Rsetn=0;

end

initial

begin

$display("\tclk,\tRsetn,\tCODE[7:0],");

$monitor("\t%b,\t%b,\t%d",clk,Rsetn,CODE[7:0]);

end

always

begin

#5 clk=!clk;

#10 Rsetn=1;

end

endmodule

我的原意是是输出每5个周期(5*10ns=50ns)翻转一次,那么一个时钟周期应该是100ns。

但是modelsim仿真出的clk的波形周期却和我原意不一样。

下面是用modelsim仿真的波形。

modelsim仿真理论上不太可能出错,那么就是我前面的计算方法有问题,可能是我理解的问题。

请各位大神指教我前面的计算方法哪里出错了,新手,要是问的太低级还请见谅,不吝赐教!先谢过!

解答:

always

begin#5 clk=!clk;

#10 Rsetn=1;

end

begin-end是串行块,串行块中的语句顺序执行,执行了5+10=15个周期以后clk的值才会更新,所以才会有300ns的clk周期出现。用fork-jion并行块就没问题了。

fork-jion并行块是并行执行,

例:

begin

regb=rega;

regc=rega;

end

//执行结束rega=regb=regc;

//begin-end串行块中的每条语句前面的延时都相当于前一条语句执行结束的时间。当第二条语句执行行,regb的值已经更新。

fork

regb=rega;

regc=regb

jion

//执行结束regb=rega,regc=regb原值。

//fork-jion并行块,每条语句前面的延时都是相对于该并行块的起始执行时间,第二条语句执行时regb的值仍然是fork-jion执行起始的值。