博客

DCDC传导EMI测试超标?来看实战整改案例解析!

||

一. 概述

电子产品工作都离不开电源,电源 DC-DC 模块应用也越发广泛,但在产品最终测试 EMC 时, DC-DC 模块却成了 EMC 超标的一个重要因素,因此在设计时 DC-DC 的 EMI 噪声抑制必须引起重视。本文将根据博主实际整改经历主要介绍 DCDC 模块噪声来源并提供一些整改意见,给具有相同 EMI 问题的同仁一个参考。

二. 问题描述

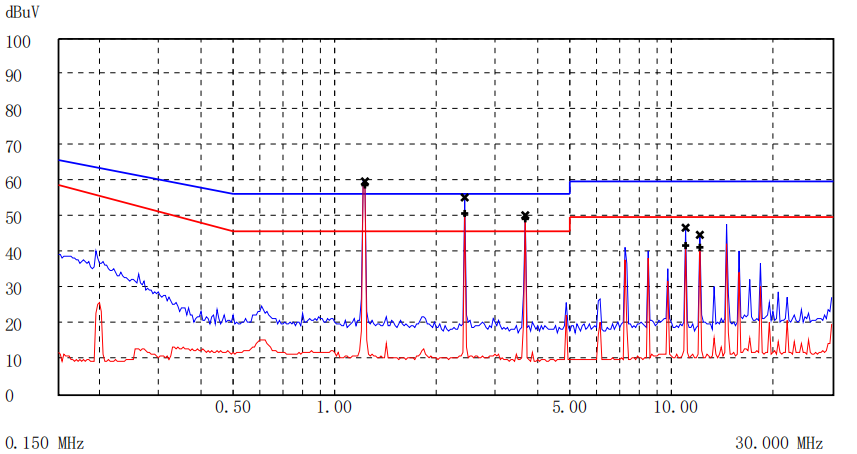

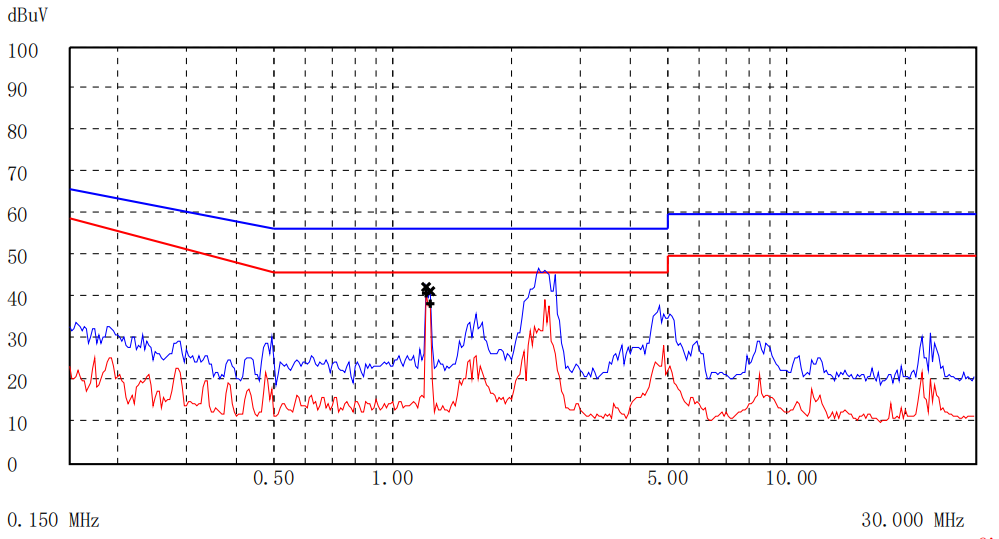

进行 EMI传导测试时在 1.2MHz、2.4MHz、3.6MHz 左右传导超标,在 1.2 M 及其倍频处出现尖峰(测试标准 EN55014)。

三. 问题定位

1. 将外设逐个关闭,测量其传导。结果在关闭其他外设仅进行供电的情况下其频段点对应尖峰仍然存在。

2. 单独启用 DCDC,测量其传导。结果测出噪声频谱与传导检测频谱基本一致,确认噪声为 DCDC 模块导致。

四. 问题分析

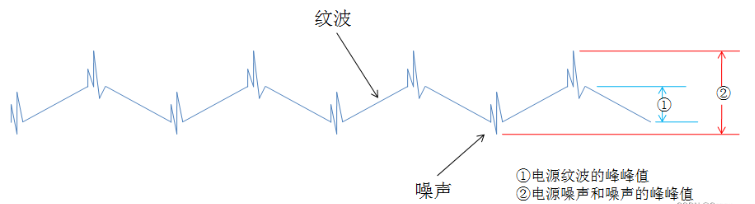

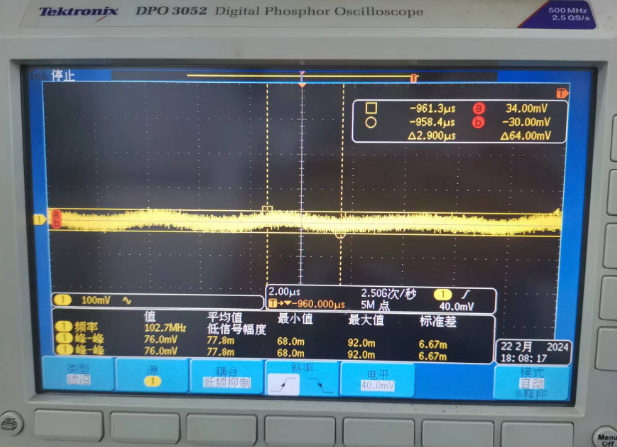

图 5 是通过示波器测量的 DCDC 纹波时域图,可以看到并没有很明显的开关噪声幅值

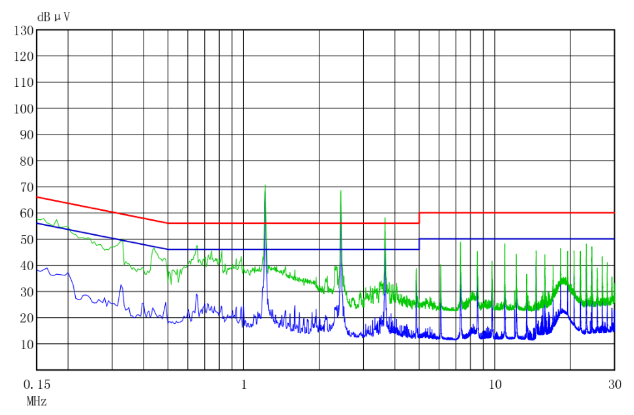

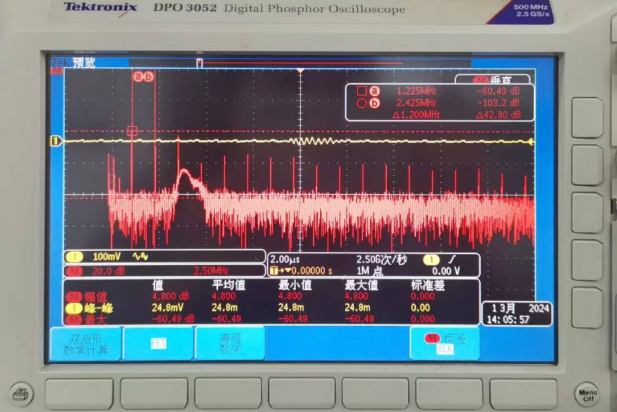

图 6 是通过示波器测量的电源输出端的频谱,在百兆的高频段未出现高的幅值,出现尖峰的频率点确实是落在 1.2 M 及其倍频处。

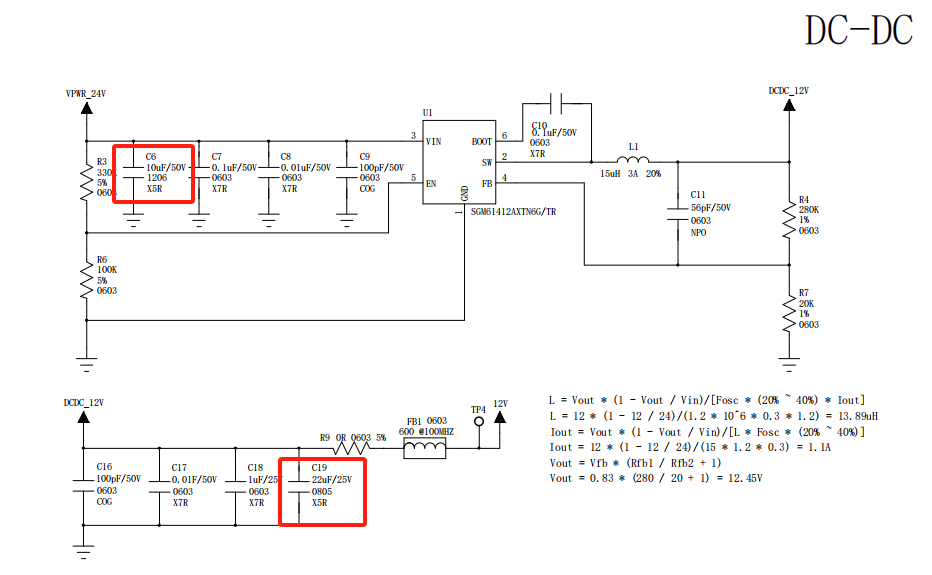

此时确认是由 DCDC 的 1.2MHz 开关频率引起的纹波电流噪声,纹波频率等于开关电源的工作频率。纹波是开关电源的固有属性,无法从根本上消除,但它也是一种有规律的、可预测的信号变化,可以通过滤波等方法降低其影响。在 DCDC 芯片的参考设计中通常会加入滤波电容来滤除纹波噪声干扰,大容量电容滤除较低频的纹波电流,较小电容可以滤除更高频率的纹波电流输出。例如在博主使用的 DCDC 模块参考设计中就中加入了 22uF 电容来滤除 1.2 MHz 的电流噪声,并且加入了其余容值的电容来滤除其他频段的噪声。

图 7 所示是在设计初期加入的滤波电容,已经涵盖了多段频率范围,防止多个频段的噪声,那为什么已经加入了滤波电容,在电源线上仍会有该频率的尖峰呢?

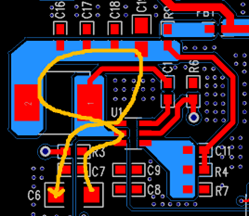

仔细查看博主 DCDC 模块 PCB 布局会发现问题所在,PCB 设计时在顶层滤波电容及 DCDC 芯片的噪声电流回路中出现了交叉及隔断现象,虽然有在地层进行接通,但由于噪声的回流不是最短路径,不一定会按照设想的回路进行传输,滤除后噪声回到芯片地路径变长,回流路径变大,噪声回到 DCDC 地引脚的路线无法确定,最终噪声电流通过电源线以差模噪声和共模噪声的形式传输干扰,表现为传导超标。

五. 问题解决

1. 选择合适的电路元件:如选择具有抖频展频功能的芯片,更适合在设计初期考虑使用。

2. 增加吸收回路:如 RC 吸收电路,更适合滤除由振铃等导致的高频信号。

3. 加入磁珠:磁珠的阻抗频率特性等更适合解决辐射干扰问题。

4. 修改PCB 布局:给噪声的回流提供更短路径,减小回流面积是个比较好的方法,最好是在设计初期就考虑,在此例中由于需重新布局,无法确定是否会引入辐射噪声,因此为进行修改

5. 滤波技术

由 DCDC 产生的噪声,是经 DCDC 芯片的输入电路再经线束传到接收机的,因此要解决此问题可在 DCDC 的输入路径上增加滤波电路。

① 加入共模电感及 X 电容,主要滤除共模噪声,经过测试可滤除大部分噪声,但成本稍高,取值为经验值。

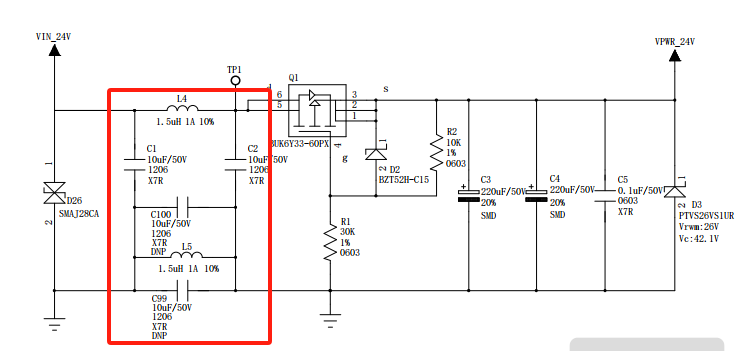

② 加入 LC 滤波电路,本例在总电压输入端加入 LC 低通滤波电路

图 9 加入 LC 低通滤波器

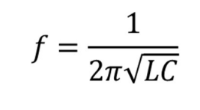

电容和电感取值根据 LC 低通滤波器的截止频率计算,电容尽量选取在滤除频率点 处阻抗值低的,电感尽量选取处阻抗值高的:

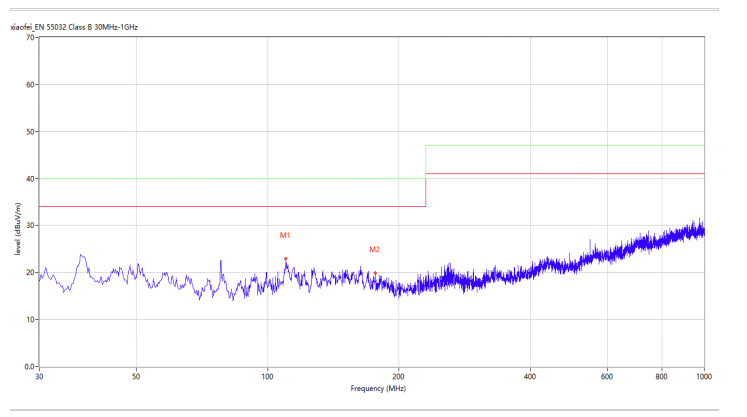

图 10 截止频率

实际的器件选型还需要根据测试的滤除效果和成本进行调整,本例中测得电感值为 1.5uH 贴片电感和 10uF 电容组成的 LC 低通滤波器效果可将 1.2MHz 噪声减低至法规线以下。

图 11 整改后检测机构传导波形

六. 总结

DCDC开关电源由于其固有的开关特性,成为低频段噪声的一个重要来源,因此在电路设计中需要进行重点考虑和处理,在DCDC输入前端增加滤波电路是一个有效的解决办法。