基于Zynq-7000高速数据采集解决方案 —米尔MYD-C7Z010/20-V2开发板

发布时间:2022-10-21 16:57

发布者:eechina

近年来,科技日新月异,随着机器视觉、人工智能的迅速发展,相关行业对数据采集系统的性能要求更加苛刻,要求能够同时采样的通道更多,采样的精度和速度要求更高。在雷达,航天,视频传输,工业控制等领域,采样率、分辨率、传输速率成为评价超高速数据采集系统的最重要技术指标,所以芯片的选择就变得尤为重要,既需要具备高精度、高采样速率等模块,又需要可以嵌入操作便捷、用户体验更友好的操作系统,实现良好的人机交互功能。

Zynq-7000是Xilinx推出的一款全可编程片上系统(All Programmable SoC)。该芯片集成了ARM Cortex A9双核与FPGA,所以ZYNQ是一款SoPC芯片。其架构如下图:

Zynq-7000架构图 Zynq-7000 器件配备双核 ARM Cortex-A9 处理器,该处理器与基于 28nm Artix-7 或 Kintex®-7 的可编程逻辑集成,可实现优异的性能功耗比和最大的设计灵活性。Zynq-7000 具有高达 6.25M 的逻辑单元以及从 6.6Gb/s 到 12.5Gb/s 的收发器,可为多摄像头驾驶员辅助系统和 4K2K 超高清电视等大量嵌入式应用实现高度差异化的设计。Zynq-7000 SoC 系列集成 ARM 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。这既能通过ARM处理器搭载Linux系统实现良好的人机交互功能,还能通过灵活的FPGA硬件设计,实现高速数据采集系统的采集工作。 米尔MYC-C7Z010/20-V2核心板

MYC-C7Z010/20-V2(核心板) 基于Zynq-7000 SoC平台,米尔电子升级开发出MYC-C7Z010/20-V2核心板及开发板,基于 Xilinx Zynq-7000 SoC 高性能低功耗处理器,集成 PS 端单核/双核 Cortex-A9 ARM+ PL 端 Artix-7 架构可编程逻辑资源,最高主频可达 866MHz;使用10层沉金工艺生产的PCB板,独立的接地信号层;该款核心板主要应用在雷达、导弹、通信、声纳、遥感、地质勘探、振动工程、无损检测、智能仪器、生物医学工程等众多领域。

MYC-C7Z010/20-V2核心板简介

基于 Xilinx Zynq-7000 SoC 高性能低功耗处理器,集成 PS 端单核/双核 Cortex-A9 ARM+ PL 端 Artix-7 架构可编程逻辑资源; PS 端最高主频可达 866MHz; 支持 USB 2.0、SDIO、千兆网等多种高速接口,同时支持 I2C、SPI 等常见接口; 支持两路 12bit MSPS ADC,多达 17 个差分输入通道; 多达 54 个复用 I/O 引脚,用于外设引脚分配; PS 端可通过 EMIO 配置 PL 端 IO,支持共享内存,支持 PS 端和 PL 端数据协同处理; PL 端可编程逻辑单元数量区间为 23K-85K,内部集成的 Block RAM 可达 4.9MByte; 可通过 PS 端配置及烧写 PL 端程序,且 PS 端和 PL 端可以独立开发,互不干扰; 核心板体积极小,大小仅 75mm*55mm; 连接稳定可靠,采用工业级精密 B2B 常规连接器,保证信号完整性; 提供 PL 端与 PS 端的片内通信开发教程。 配套MYD-C7Z010/20-V2开发板 (1) 提供核心板引脚定义、可编辑底板原理图、可编辑底板 PCB、芯片 Datasheet,缩 短硬件设计周期; (2) 提供系统烧写镜像、内核驱动源码、文件系统源码,以及丰富的 Demo 程序; (3) 提供完整的平台开发包、入门教程,节省软件整理时间,上手容易; (4) 提供详细的异构通信开发教程,很好的解决开发瓶颈; (5) 提供基于 Qt 的图形界面开发教程。

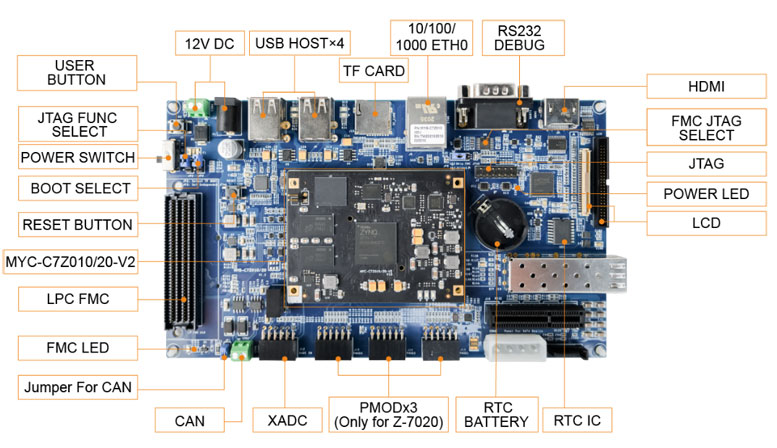

MYD-C7Z010/20-V2(开发板) 附MYD-C7Z010/20-V2资料: SOC:Xilinx Zynq-7010/20 高性能双核ARM Cortex-A9处理系统(PS),FPGA架构:可编程逻辑单元 XC7Z010(28K,约43万逻辑门 )XC7Z020(85K,约1.3M逻辑门)。 系统内存:1GB DDR3 SDRAM(512MB*2)、 存储: 4GB eMMC,QSPI 默认32MB,TF CARD槽(支持外部启动) 网络:一路千兆网口 视频:HDMI接口,LCD接口 USB:USB HOST*4 JTAG:1路PS/PL复用 JTAG接口(进行编程调试下载) 供电:核心板:5V/0.5A,开发板:12V/0.5A 尺寸:190mm x 110 mm

|

网友评论