系统级可编程能力助力嵌入式应用

发布时间:2009-12-21 15:42

发布者:贾延安

|

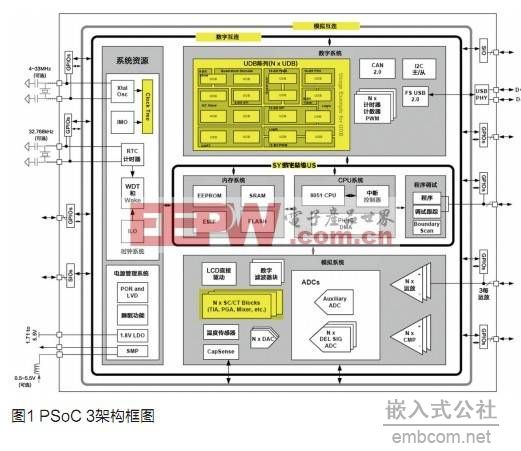

在您曾经从事的嵌入项目中,有多少在项目生命周期各阶段成功过渡而不需要重做系统设计、物料清单、布线等呢?如果您的答案与嵌入业界的大部分人一样低于百分之百,则您可以考虑采用嵌入设计的一种新方法,它有望节省您的时间、金钱和烦恼。本文中,我们将探讨您日常面对的嵌入设计挑战,并以实用的方式探讨如何运用系统级的可编程能力克服这些挑战。首先,简介什么是真正的可编程能力。 真正的系统级可编程能力 我们将这一话题分为三部分分别进行说明:编程能力、系统级、真正。可编程能力不应与可配置能力混淆,而是指使用基本结构块构建功能的能力。该定义下,这些基本结构块在硬件中实施,并通过配置寄存器、数据路径和信号路径共同用于构建某个功能。例如,图1中描述了赛普拉斯(Cypress)下一代PSoC设备架构PSoC 3 和 PSoC 5中实施真正系统级可编程能力的基本结构块。图中突出显示的这些基本结构块包括高性能的8位8051 (PSoC 3) 或32位ARM Cortex M-3 (PSoC 5) 处理器、可编程时钟树、Universal Digital Block (UDB,通用数字块)、可编程模拟块和可编程路由和相互连接(模拟、数字和系统总线)。

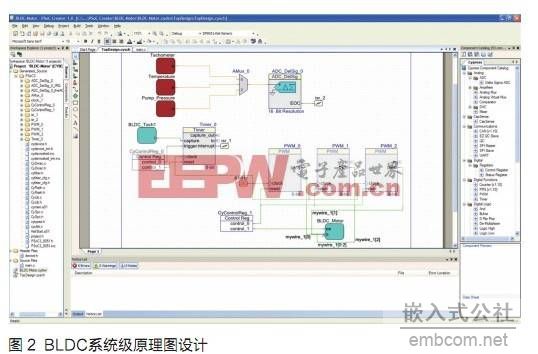

PSoC 3和 PSoC 5架构中的时钟系统使一组模拟和数字时钟支持各种外围设备,例如ADC、PWM、计数器等。八个单独源的 16 位时钟分频器用于数字系统外设,四个单独源的 16 位时钟分频器用于模拟系统外围设备,所有分频器与一套四个内部或二个外部时钟脉冲源连接,形成强大的时钟数。 每个 UDB 是一个非常强大、灵活的数字逻辑时钟。PSoC 3 和 PSoC 5 架构中的每个 UDB 包括一个基于 ALU 的八位数据路径、两个细粒度 PLD、一个控制和状态模块以及一个时钟和复位模块。这些元件可以共同执行低端微控制器的功能,也可以将它们与其他UDB连接起来实现更大的功能,或者由他们实现数字外围设备,例如定时器、计数器、PWM、UART、I2C、SPI、CRC等,某些PSoC 3和 PSoC 5设备家族采用24个UDB,您甚至可以在8051或ARM Cortex-M3 处理器的基础上实现 24 核处理器,或内部 DMA(一个非常强大的架构)。 PSoC 3和 PSoC 5的模拟能力与带一套可编程模拟外围设备的高精度固定功能模拟(基准电压精确度为工业温度和电压范围的± 0.1%)结合,可用于实现混频器、转阻(trans-impedance)放大器、缓存、运算放大器等。灵活、高精度模拟能力的综合运用可以实现许多独特、强大的设计。 最后,PSoC 3和 PSoC 5架构的路由和相互连接(如图1所示)由系统总线构成,允许任何GPIO成为数字、模拟、CapSense或LCD驱动I/O,这是真正强大的功能,实现显著的成本节约(4层到2层PCB)以及更简便的板布线,真正路由自由。 那么,系统级的含义是什么呢? 很久以来,我们已拥有组件级的可编程能力,形式为可编程数字逻辑(CPLD、FPGA等)、可编程模拟(开关电容及类似功能)、可编程时钟、可编程处理器等。系统级的可编程能力即是指在单个平台、单个设备中的所有这些可编程组件通过一个易用、分级原理图设计、软件开发环境进行控制和配置。图2为无刷直流电机控制(BLDC)应用示例的系统级示意图。查看该图时,您无需考虑这些单个组件实例化的细节,您应将重点放在对外围功能的需求上。无论是读取转速表、温度或泵压力读数向电机控制功能提供一个反馈回路,或是使用单个PWM控制器驱动三相电机,您在处理系统设计挑战时无需担心独立 IC 或外围组件等低级别细节。

最后,定义中的真正用于帮助区分这一级别的可编程能力和具备可配置固定功能外围设备的设备。这意味着如果您不需要某个功能,您可以将分配给该功能的资源用于其他目的,如果您决定不适用某个功能,这设备中不会存在被浪费的功能。设备中唯一被浪费的空间(如果有)由基本结构块组成,可随时用于设计中的变更或实现新的功能。 实际应用 您面临着多个设计挑战。第一个挑战是适应变更—要求、路线、设计、可用材料的变更;另一个挑战是如何快速销售—击败竞争者并在正确的时机推出产品以获得最大的效果;第三个挑战是模拟的复杂性—选择、配置和使用正确的部件用于正确的用途;最后,必须保护您的设计IP(知识产权),以防止竞争者复制您的设计并偷走您的市场份额。赛普拉斯的 PSoC 可编程片上系统和开发软件可以满足这些挑战要求,以下将以实用的方式探讨真正的系统级可编程能力和 PSoC 如何应对这些挑战。 适应变更 嵌入式工程师生涯中唯一不变的事就是变更,通过良好规划应对变更并利用工具获得适应变更的能力是您取得真正成功的唯一途径。如图2所示,变更对 PSoC 工程师来说可能是对某个外围设备的简单修改—可能是增加某个 ADC 的分辨率或者在复杂情况下向设计加入一个额外功能,例如通过 USB 的控制接口或者 LCD 段显示和电容式感测按钮。通过真正系统级的可编程能力,您能够应对变更并利用它来开发您所能设想的最好产品。 快速上市 快速上市所面临的最大挑战并不总是关于概念或想法,而是如何根据这些想法创造出产品。PSoC 工程实现方案快速原型制造,简便的芯片中调整和编程,使用系统级的软件开发环境。通过这两种能力,您能够简便地试验硬件解决方案以了解真实的需求并将产品投入生产。 模拟复杂性 PSoC(可编程片上系统)平台及其软件开发环境通过直观的系统级基于原理图的设计方法,使模拟电路和功能易于使用。如图2所示,模拟外围设备的实例化与在PSoC Creator 中设计画布上拖放组件同样简单,然后进行您所实施功能的外围配置设置,该示例中 ADC 的配置:分辨率、转换率、时钟脉冲源等。转阻放大器、滤波器、模拟复用器、比较仪、DAC和其他外围设备的实例化同样简单。 设计IP的保护 PSoC通过设备中嵌入的系统可编程能力,提供额外的安全层。如果竞争者查看模具时,他们只能看到组成PSoC设备本身的组件,却无法看到初始化和实例化使用 PSoC Creator 所开发系统的固件。PSoC 设备中的固件还受到多种程度的保护,并由内存时钟定义以符合整个设备的多个保护层次:无保护(在开发期间使用)、外部读取保护、外部读/写保护以及完全保护(禁止外部读/写或内部写入)。通过这些层次的保护,在 PSoC器件中实施的设计秘密能够轻易地抵御标准反向工程技术。 结论 赛普拉斯的 PSoC 可编程片上系统和及其开发软件通过新型 PSoC 3 和 PSoC 5 架构提供系统级编程能力,帮助您轻易地克服每日在嵌入式设计中所遇到的困难,并使您将精力集中在真正重要的产品上。这些新的架构扩展了世界上仅有的可编程嵌入设计平台,打破了设计限制。在一块芯片中,您可以利用高精度可编程模拟,包括12位至20位 delta-sigma ADC、包括几十种插入式外围设备的数字逻辑库、同类最佳的电源管理以及丰富的连接资源;所有这些均配合PSoC 3 和PSoC 5中分别集成的高性能单周期 8051或ARM Cortex-M3处理器中。 参考文献: [1] PSoC Creator软件工具[R/OL].www.cypress.com [2] ANUP.Implementing CAN Bus Communication using PSoC 3 [R/OL].(2009-9-21).http://www.cypress.com/?rID=38599 [3] PSoC 3 / PSoC 5 LCD Drive Solutions[R/OL].(2009-9-21). http://www.cypress.com/?rID=37989 [4] PSoC 3 Magnetic Card Reader[R/OL].(2009-9-20). http://www.cypress.com/?rID=38595 [5]Gu D.CY3253 BLDC BLDC Sensorless Speed Control Kit[R/OL].(2009-9-29). http://www.cypress.com/?rID=3983 作者:Jim Davis 赛普拉斯半导体公司 时间:2009-12-11 来源:电子产品世界 |

网友评论