ISE时序约束笔记7——Path-Specific Timing Constraints

发布时间:2016-2-18 14:11

发布者:designapp

|

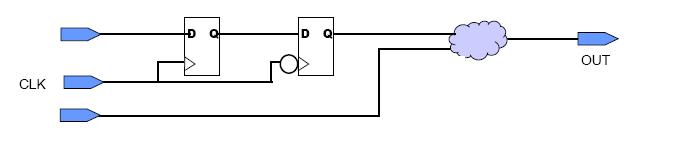

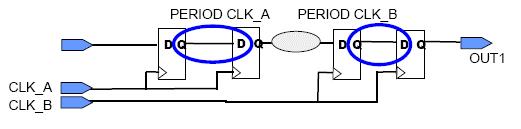

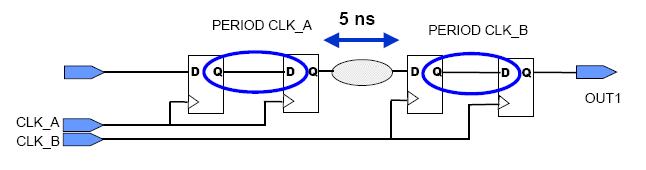

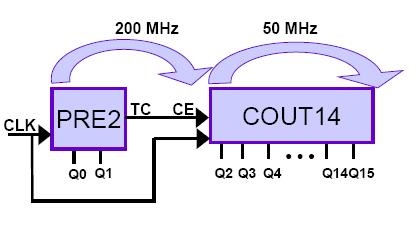

时钟上升沿和下降沿之间的时序约束 周期约束可以自动计算两个沿的的约束——包括调整非50%占空比的时钟。 例:一个CLK时钟周期约束为10ns,能够应用5ns的约束到两个寄存器之间。 不需要特定路径应用到这个例子中。  相关时钟域的约束 为一个时钟进行周期约束——以这个周期约束确定相关的时钟。 执行工具将根据它们的关系来决定如何处理跨时钟域。 DCM有多个输出: ——确定DCM输入时钟的周期约束 ——执行工具将会从这个周期约束推导出其输出的约束 ——所有的约束将会和原始的周期约束相关 不相关时钟域的约束 在这个例子中,周期约束不覆盖到处于两个时钟域之间的任何延时路径。——这是默认的处理方式。 你必须添加一个约束覆盖到相关时钟域之间的路径中。——例如,频率相同,但是CLK_B有一些相位偏移。 在两个不相关的时钟域你就必须添加一些同步电路。  约束两个时钟域之间的路径。 ——使用Groups by NETs选项为CLK_A和CLK_B定义groups,如果你为每个时钟添加完周期约束,这个步骤将自动完成。 ——在这个寄存器的groups之间指定快速/慢速例外约束。  多周期路径约束 多周期约束应用在连续几个时钟周期内寄存器不需要更新的情况。 ——总是至少需要一个时钟周期才更新。 ——通常的,这样的寄存器由时钟使能信号控制。 一个分段计数器就是这样的一个例子。 ——COUT14每隔4个时钟周期才更新一次。 ——这些寄存器间的路径就算是多周期路径。  False 路径 False路径选项将用于防止约束覆盖到特定路径 时序约束优先级 从高到低为: 1. False路径——将会覆盖任何其它的约束路径 2. FROM THRU TO 3. FROM TO 4. 管脚指定OFFSETs 5. Groups OFFSETs(由寄存器或者PADS生产的groups) 6. 全局PERIOD和OFFSETs——最低优先级约束 这里特权同学提醒大家注意的是,通常类似下面这样的计数器绝对不可以归为多周期约束: reg[15:0] counter; always @ (posedge clk or negedge rst_n) begin if(!rst_n) counter else counter end 虽然我们想想似乎counter[1]也是2个clk变化一次,counter[2]也是4个clk变化一次……但是,我们想想看,如果从counter=1到counter=2没有在一个clk完成,那么肯定就会影响到counter=2到counter=3的变化,对吧?所以,这样的计数器不能算做多周期约束例外。 提纲里描述的多周期例外的计数器应该是这样一个模型: reg[15:0] counter; always @ (posedge clk or negedge rst_n) begin if(!rst_n) counter[1:0] else counter[1:0] end always @ (posedge clk or negedge rst_n) begin if(!rst_n) counter[15:2] else if(counter[1:0] == 2’b11) counter[15:2] end 上面两个always块里的数据互不干扰,并且都正常工作,只有下一个always块检测到前一个always块里的counter[1:0]==2’b11时才进位加1。 写到这里,特权发现单从功能上来说,这两个例子是没有差别的,说白了,任何一个计数器都可以建模成后面的形式。或者说,我的问题其实没有说明白,反而被自己的例子给驳倒了。 呵呵,换个角度思考这个问题,到底什么时候是多周期例外,什么时候不是?这个其实还是要看情况的,如果你的系统实时性较高,可能会在某一特定的时钟周期用到16位计数器的计数值(如a = (counter == 16’hffff)?1b’1:1’b0; ),那么这个计数器的高位就不能算作多周期例外。而如果比如在我的一个工程里,有这样的计数器用法:cuonter[2:0]没16个clk的后8个clk需要自增加(从0到15),而高位counter[18:3]当然只有在16个clk变化一次,因为这里counter是用于作为一个地址产生器,也就是说,我的地址是每16个clk的后8个clk用到,那么这里的counter[18:3]就是一个8clk的多周期例外实例。 说白了,还是要具体问题具体分析。 |

网友评论