PlanAhead教程5:网表分析与ChipScope内核插入

发布时间:2014-1-10 11:42

发布者:eechina

|

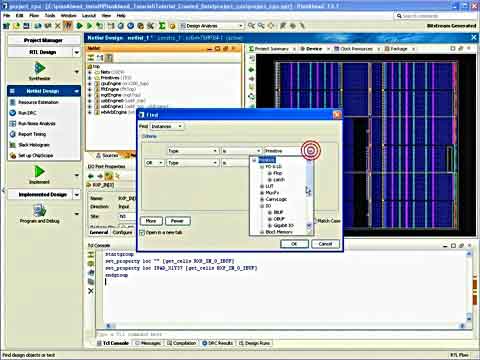

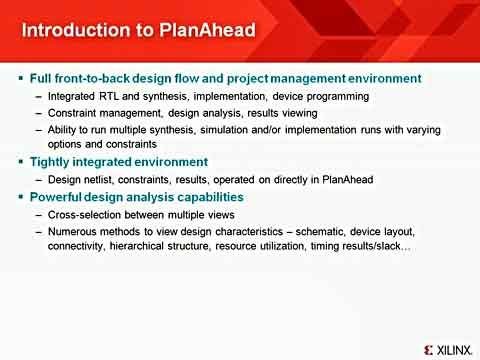

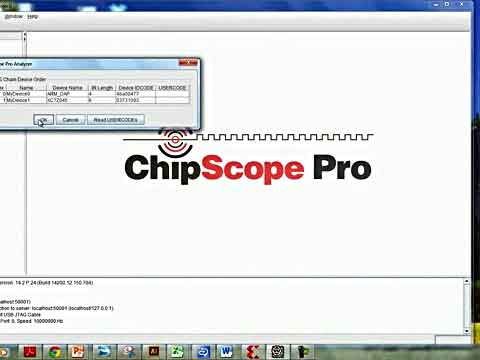

PlanAhead 拥有广泛的功能,能够帮助设计人员成功实现设计收敛。其中包括具有综合交叉探测功能的 GUI,能够帮助您进行设计分析、跟踪时序冲突以及 DRC 等问题,然后再将问题追根溯源到原理图、网表以及约束条件。使设计人员能够对 pblock 以及单元例程的位置约束等物理约束条件进行实验。 此外,PlanAhead 还能够自动插入 ChipScope 调试内核,以更好地调试运行于器件之上的设计后实现比特流。 |

网友评论