TI 采用新型“金刚狼 (Wolverine)”MCU 平台可使 MCU 总功耗锐减 50%

发布时间:2012-10-10 19:16

发布者:1770309616

|

Jacob Borgeson,德州仪器(TI)MSP430 产品市场工程师,MSP430 产品市场工作组 引言 德州仪器 (TI) 于上世纪 70 年代推出了微控制器 (MCU),并已在众多的平台中运用了此项技术,包括超低功耗 MSP430™ MCU 产品系列。MSP430 MCU 十多年来一直是业界超低功耗技术的领先者,而且每一代新型架构皆专注于创造全新的功耗与效率指标记录。 MSP430 架构业已提供了仅在需要时才唤醒的智能外设、允许 MCU 内部的模块以不同频率运作的灵活定时、以及先进的电源管理技术等,这些只是其诸多创新成果中的几个而已。虽然贵为业界领袖,但 TI 并未因此沾沾自喜固步自封,而是一如既往地投入巨资不断地开发最先进的超低功耗技术。 凭借“金刚狼 (Wolverine)”MCU 平台(因其运用了激进的节能技术而拥有了这一代号),TI 创立了下一代 MSP430 架构(见图 1)。这款新型平台将 MCU 的功率与能源消耗锐减了一半以上,从而使超低功耗性能迈上了一个新台阶。 * 据美国史密森研究所 (Smithsonian Institution) 提供的资料。

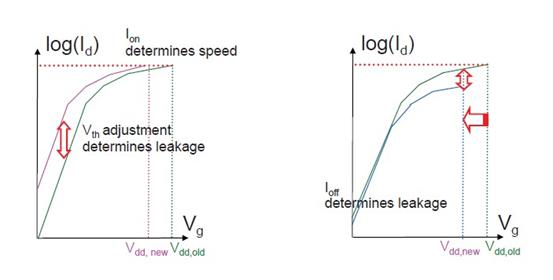

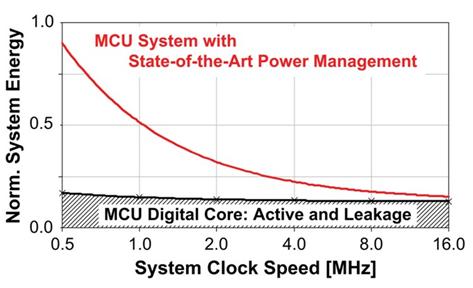

图 1:凭借“金刚狼”MCU 平台(因其运用了激进的节能技术而拥有了这一代号),TI 创建了下一代 MSP430 架构,其将 MCU 的功率与能源消耗锐减了一半以上,从而使超低功耗性能迈上了一个新台阶。 运行模式功耗低至 100μA/MHz 待机流耗低于 400 nA(RTC 和欠压保护模式) FRAM 每位能耗下降了 250 倍 可在不到 7μs 的时间里从待机模式唤醒至运行模式 TI“金刚狼”平台之所以实现了引人注目的功耗性能提升,凭借的是其新型 130 nm 超低漏电 (ULL) 工艺技术、集成型低功耗非易失性存储器以及利用先进的电源管理与高精度低功耗模拟组件得以增强的 MSP430 原生优势。 13 nm 超低漏电 (ULL) 工艺技术 鉴于超低功耗器件有 99.9% 的时间都处于待机模式,因此在较小的工艺几何尺寸下,漏电流便成为了决定功率效率的一个关键因素。低功耗设计的挑战源于晶体管漏电流的指数性增加(因栅极长度的不断缩减及栅极氧化物所致)。 漏电流基于电子在节点之间必须移动的距离,而随着这个距离的不断缩小,电子在节点之间的泄放越来越容易。以基于 25 nm 或 45 nm 工艺的 PC 用高性能微处理器 (MPU) 为例,其必须使用特殊的材料来控制漏电。对于 MCU,漏电流从 180 nm CMOS 工艺节点开始变成了一个重要的考虑因素。 通过其在 65 nm、45 nm 和 28 nm 工艺节点上设计的 GHz 智能手机处理器和数字信号处理器 (DSP),TI 对于较小工艺节点下的漏电流了如指掌,而且 TI 的工程师们把学到的有关这些较小工艺几何尺寸下的漏电流特性的知识,全部都应用到了“金刚狼”的 130 nm 工艺中。 历史上,MCU 设计人员往往将其创新的着重点放在提高性能和密度上。自 1965 年以来,摩尔定律 (Moore‘s Law) 一直在推动着晶体管和芯片性能的提升。虽然这种改进的步伐在过去的 10 年间有所放缓,但工艺技术每 18 个月将性能提升一倍的历史,已经有 30 多年了。 就 130 nm“金刚狼”平台而言,TI 通过专为提升功率效率而设计,并针对较低漏电流和其他硅工艺固有特性而优化的电路,恢复了摩尔定律在改善功耗(而非性能)指标方面的作用。尽管没有像采用传统方法时那样将性能提升一倍,但 TI 却代之以功耗的减半(也就是将功耗指标改善了一倍),同时保持了现今 MSP430 MCU 架构的高性能。 结果,与其他 130 nm CMOS 工艺相比,各个晶体管的最小漏电流将至少减低10 倍,而运行功耗则总体下降了 15%(图 2)。

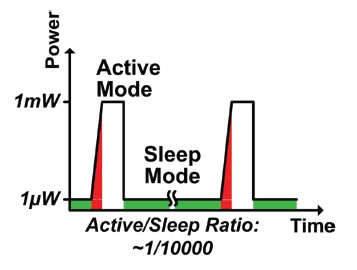

图 2:采用低漏电法虽未提高性能,却可以保持低的功率损失,同时充分利用工艺尺寸缩小带来的运行功耗下降优势。结果是:漏电流减低 10 倍,而运行功耗总体下降了 15%。 超低功耗的基础 为了获得新型 130 nm 工艺技术的最大优势,TI 对其整个设计工具套件库进行了全面的重新设计,旨在将着重点集中在功率效率而非高性能上。这些工具套件(包括标准单元库、电容器、模拟组件和 I/O)基于基础级晶体管配置,其形成了用于设计当今复杂 MCU 的主要构件。 针对 130 nm 工艺的新型工具套件具有丰富的模拟组件,以实现诸如高精度模数转换器 (ADC) 等外设和用于大幅降低功耗的内部电源管理电路。例如:“金刚狼”模块产品组合包括一个每秒钟能完成 20 万次采样而流耗仅为 75μA 的高精度 12 位 ADC。同样,具有日历显示和报警功能的实时时钟 (RTC) 模块能够以仅仅 100 nA 的流耗运行。130 nm 的超低漏电工艺与丰富的混合信号集成相组合,有助实现业界最低的总系统功耗。 先进的电源管理 功率效率并非只适用于 CPU 的功耗。有功电流同样取决于系统执行定时的效率、高精度模拟外设和通信接口。如欲最大限度地降低各种不同工作负载条件下的功耗,运用先进的电源管理技术是必不可少的。 “金刚狼”架构提供了 MSP430 MCU 电源管理模块的一种增强型版本。除了支持 7 种操作模式之外,“金刚狼”电源管理模块还能提供先进的电源门控 (power gating),并采用了一个高响应性的自适应稳压器。在内部,MCU 被分割成了几个功率域,以使系统能够根据应用的特殊需求动态地管理器件的每个部分。 当使系统在尽可能长的时间里处于待机模式时,就最大限度地降低了总体系统功耗。然而,系统每次在待机模式与运行模式之间切换都会产生功耗。特别地,供应给电路的电压不但达到预期电平而且重新预置子系统或外设,以再度变至运作状态,都需要时间。在这段时间里,电路吸取的功率日益增大,却并未完成任何有用的工作(见图 3)。这些唤醒损耗将导致性能下降、响应性减慢和功率效率走低,特别是在那些频繁地在“运行”与“待机”模式之间切换的系统中。

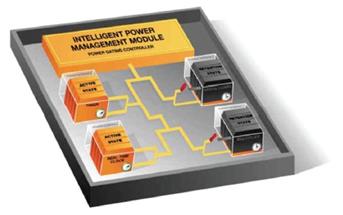

图 3:当系统被唤醒时,它将吸取功率而不执行任何有用的任务。这些唤醒损耗将导致性能下降、响应性减慢和功率效率走低,特别是在那些频繁地在“运行”与“待机”模式之间切换的系统中。 为了降低唤醒损耗,“金刚狼”采取了一种不同的方法。传统上,在不用的时候整个模块或外设都会被关断。通过采用电源门控控制器,使更多的模块或外设以一种“保持”模式运行,“金刚狼”改善了功率效率。在该模式中,对那些处于运行状态并请求时钟的模块保持全面供电。而对于那些处于空闲和未用状态的模块则施以“保持水平”的供电。这意味着将只对专门用于保持模块状态的逻辑电路供电。 电源门控可以在不牺牲性能的情况下实现显著的节能。设想一个在待机模式中处于使用状态的定时器。当此定时器主动请求一个时钟时,电源门控控制器检测到该请求并把定时器保持于一种全面运行的状态。然而,一旦定时器功能完成,则将其供电降至“保持水平”,同时维持配置状态以尽可能地降低功耗。当再次需要定时器时即可快速提供,从而最大限度地减少唤醒损耗。电源门控对于开发人员是透明的,可使他们充分利用业界领先的功率效率,而无须对每个模块或外设进行手动控制(见图 4)。

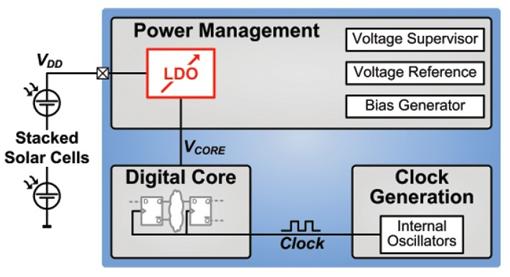

图 4:这是以一种简单的可视化方式显示的运转中的先进电源门控功能。将器件中的未使用部分维持于“保持状态”,从而使它们能以比采用其他架构时快得多的速度唤醒。 超低功耗 MCU需要具备的另一项重要功能是拥有对变化的应用负载做出快速响应的能力。利用可在不需要主 CPU 完整性能的情况下降低其供电功率的技术,即可实现大幅节能。然而,“金刚狼”平台中的智能电源模块可自动适应应用负载的变化(比如:当一个高频模块上电时),而不需要开发人员以手动的方式调节该功率(见下页上的图 5)。 操作速度根据以下条件进行调节: · 应用要求 · 最大可用功率 在低数字功率下具有低稳压器开销

图 5:“金刚狼”智能电源管理模块可自动适应应用负载的变化,从而实现“透明”的功率调节。 具体而言,负责为 MCU 的数字内核供电的自适应低压降稳压器 (LDO) 可根据需要增加其负载,从而对变化的功率要求做出响应。事实上,“金刚狼”能自动检测应用的电流需求并根据需要提供时钟与功率。

图 6:“金刚狼”能自动检测应用的电流需求,随后动态地调节自适应 LDO 以与应用的功率及定时要求相匹配,从而最大限度地提升功率效率。 凭借很高的精细度,该 LDO 能够与各种各样的应用负载相匹配。另外,这种方法还免除了增设诸如缓冲电容器(其在从低负载电流切换至高负载电流时使用)等外部组件的需要。与电源门控一样,该节能技术同样以一种对开发人员“无缝且透明”的方式实现了电源管理的自动化。 铁电随机存取存储器 (FRAM) MCU 程序代码和主要系统参数通常存储于非易失性存储器之中,最常用的是闪存或 EEPROM。闪存的写入速度偏慢,而且功耗高、可写入次数少,因而不适用于数据存储。因此,MCU 通常至少具有两类存储器:用于存储代码的闪存和用于存储数据的 SRAM。 为了克服闪存的局限性,TI 在“金刚狼”架构中集成了一个全新的非易失性存储位 - 铁电随机存取存储器 (FRAM)。TI 投资研发 FRAM 技术已有 15 年了,而且除了其目前提供的具有嵌入式 FRAM 的 MSP430FR57xx 器件之外,自 2007 年以来 TI 还与 Ramtron 公司合作生产独立型 FRAM 器件。 FRAM 与 DRAM 很相似,只是它利用一种结晶状态(而不是电荷)来存储数据。所以,它具有与 DRAM 相似的读/写存取和快速周期。 FRAM 同样也是一种随机存取存储器,其每个位都可个别地读或写。此外,FRAM 还采用一种简单的单步写过程。这意味着它不需要像使用闪存时那样在进行写操作之前进行一次单独的擦除操作。 与闪存相比,FRAM 具有很高的效率(见表 1)。闪存的写操作需要 10 V~15 V 的电压和一个充电泵,这增加了几 ms 的充电时间。另外,闪存的写入还是一种多级操作,期间必须禁用中断。这一因素使得闪存的块写入变得复杂化,因为系统必须将此类写入划分为若干个可在其间启用中断的较小区块,这样就不会丢失关键的信号或事件。 表 1:非易失性存储器技术的比较

2 - 总功耗 FRAM、SRAM 和闪存的数据代表了器件内部嵌入式存储器的性能 与此截然不同的是,FRAM 的写操作只需要 1.5 V 电压。再加上其写入速度是闪存的 100 倍,因此实际的写操作能耗下降了 250 倍。另外,由于在 FRAM 操作期间中断可以运行,所以还能在不增加编程复杂性的情况下保持系统可靠性。 看看非易失性存储器在汽车信息娱乐系统中的使用情况,FRAM 与闪存的效率对比便能一目了然。当汽车断电时,需要收集和存储多种系统数据,以便能够在汽车重新通电时复原。在系统所保存的这些数据当中,包括了驾驶者和乘客设定的温度值、收音机预设电台、GPS 位置和收音机音量等。 由于汽车并不知道其电源将在什么时候被切断,因此必须使用一个电容器并在汽车通电时对其进行充电。在写入数据的过程中,该电容器负责为闪存和 MCU 供电。需要保存的数据越多,电容器就越大。此外,闪存相对较慢的写入速度对于所能保存的数据量也有影响。 在采用相似电容器的情况下,FRAM 可凭借其高写入速度和功率效率实现 900 倍于闪存的数据存取量。这使得开发人员能够采用较小(而且较便宜)的电容器,设计不太复杂的系统。写操作能力上的这种巨大差异可造就一种全新的低功耗应用,包括那些需要实时数据录入和/或采用能量收集技术的应用。而且,较快的写操作能力还意味着系统可以在更长的时间里处于睡眠模式。 不过,使用 FRAM 也会影响系统的设计方法。闪存的写寿命有限(可写入次数约 10 万次),之后可靠性将开始下降。故此,系统参数常常仅在系统断电时保存到闪存中。而 FRAM 实际上没有限制的写寿命(可写入次数约 100万亿次)则可使开发人员重新考虑其存储系统参数的方式。具体来说,就是可以把所有的数据早早存储在非易失性 FRAM 中(即使在其经常变化时也不例外),而不是把参数存储在 SRAM 中并在断电时保存至闪存。由于不必主动保存参数且不再需要使用电容器,因此这种方式将更进一步地节省成本。 系统唤醒也得到了改善。在上述的汽车应用中,上电时无需将设定值恢复至数据存储器,因为它们已在公用的 FRAM 内存空间里提供。对于可用功率严重受限的应用(比如那些采用能量收集技术的应用),这同样使其效率有所提高。由于在睡眠期之间不需要为存储和恢复数据消耗功率,因此应用可以使用较小的能量收集电路运作,从而降低系统的复杂性与成本。FRAM 使得开发人员能够以“延长操作寿命、降低系统成本和提高产品可靠性”的方式重新考虑其系统架构的设计,这里所述只是一个例子而已。 FRAM 另一项重要功能是可兼用作程序存储器和数据存储器。在基于闪存的系统中,根据代码长度和数据量来优化系统的能力,其受限于 MCU 所集成的闪存和 SRAM 的数量。 快速写存取和实际上无限的可写入次数使 FRAM 既可用作程序存储器,也可用作数据存储器。MSP430FR58xx 系列(首批基于“金刚狼”的器件)将提供 64 K 字节的存储器,并为开发人员在代码与数据之间分配该存储器赋予了全面的灵活性。 同时,这还使得设计人员能够采用具有不同于先前可用之内存比 (memory ratio) 的较小 MCU。此外,TI 还集成了一个存储器保护单元 (MPU),用于避免数据操作意外改写系统代码以及用于提供额外存储器保护的可锁式代码段。 基于“金刚狼”的器件还将具有一个 SRAM 区块。该存储器可用于那些真正需要 SRAM 的无限制可写入次数的应用(以满足特定操作的要求)。该 SRAM 区块亦可用于帮助简化现有 MSP430 MCU 设计方案的移植。 实际的处理效率 对于超低功耗应用而言,功耗的减半实际上远比处理器速度的倍增更合乎需要。通过提高系统进入睡眠状态及从睡眠状态唤醒的速度,开发人员可在相同的时间和功耗情况下完成更多的处理任务,从而实际上加快了处理速度。这也为开发人员管理其设计中的功率提供了更多的控制手段。针对嵌入式应用,开发人员能够充分利用基于“金刚狼”的高效率器件并调节至其所需的确切性能水平,而无须使用智能手机级的 MCU。 “金刚狼”器件将与现有的 MSP430 MCU 工具和软件相容,从而使开发人员可充分“享用”无所不包的 MSP430 MCU 生态系统。芯片与工具链中的内置硬件将帮助开发人员实时跟踪电能使用状况(获得准确的功率分配图),这样在估计系统功耗和有效操作寿命时就不再需要依靠猜测了。TI 还将提供专为分析代码而设计的优化工具,以确保功率效率。 在过去的 10 年里,TI 以开发超低功耗技术为己任。“金刚狼”帮助实现了性能与透明电源管理技术的重大突破,开发人员因此能够把更多的时间投入到设计其应用的核心功能上,而减少花费在优化功耗上的时间。 “金刚狼”平台使 MCU 的功耗锐减 50%,从而真正改变了超低功耗技术领域的面貌。这种高功率效率与低功耗能量收集技术的进步相结合,使业界朝着“无电池世界”又迈近了一步。 更多详情 可通过下面的网址获取更多相关信息:www.ti.com/wolverine 。 |

网友评论