基于高吞吐率WLR测试的 ACS集成测试系统(二)

发布时间:2012-9-19 15:51

发布者:majake2011

|

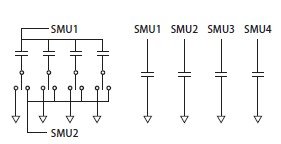

多器件TDDB和NBTI 图4示出了多器件TDDB测试结构的共用 SMU和SMU-per-pin配置。在开关(共用SMU) 情况下,SMU1提供连续应力至测试序列的全 部结构,SMU2顺序测量每个器件。在顺序分 析结构的过程中,开关延时和有限的测量速 度合在一起会限制每个结构的测量速度。因 此,必须分析这些延时并折合至寿命分析以保证准确推测寿命。而且,如果一个结构遭 受灾难性的故障,本组的其它结构将遭受电 压瞬变、暂时失去应力条件并可能使测量结 果不准确。SMU-per-pin架构不受开关延时 和结构不良连接的影响,但更重要的是测量 速度非常快,这对于采集高速渐进击穿现象 而言至关重要。

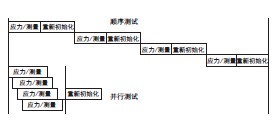

图4. 使用左半部的共用SMU架构以及右半部的SMU-per-pin 架构进行TDDB测试。 NBTI测试面临不同的问题。NBTI测试 结构是一个MOSFET,其中在栅极施加应力 并在漏极进行测量,源极和衬底接地。由 于劣化恢复问题,NBTI要求极高的测量速 度。特性分析带来的应力中断时间应尽量 短。测量速度越快,劣化测量的准确度越 高。2 很明显,共用SMU系统在应力和测量 周期之间引入了延时,并在特性分析之间 的应力持续期带来了可变性。即便使用可 能造成损害的热开关技术3,也必须测量应 力周期长度的变化并在寿命分析过程中加 以考虑。 并行测试和多个组 并行测试提高了测试仪和探测器的利 用率并通过同时测量多个器件提高了吞吐 量。所提高的吞吐量相对标准可靠性测试而言可能是图5所示顺序测试流的好几倍。 对于仅包含应力-测量序列的简单测试 而言,采用共用SMU方法能以更快速的源、 更短的建立延时和更高的积分速率缩短测 试时间。但这样做付出的昂贵代价是测量 误差升高。另一种并行测试方法可以在先 前测试一个器件的时间内提供4个器件的 测试结果。当然,这假定了测试时间比开 销(例如,探测器移动)时间长得多。增 加被测器件的数量,尤其在时间较长的可 靠性测试中,能节省大量时间并得到更多 的统计数据样本。

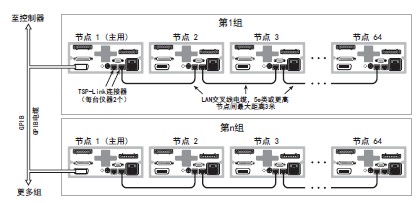

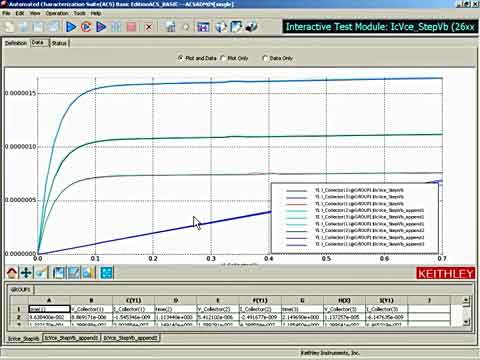

图5. 在顺序测试与并行测试之间的时间差 并行SMU-per-pin ACS集成测试系统的实现 使用多个GPIB组的2600系列源表实现 ACS集成测试系统的并行测试。通常使用4 个SMU(2台2600系列仪器)一组来测量4 端FET或4个电容器。组内的2600系列仪器 用TSP-LinkTM 连接起来作为一台仪器那样进行控制。此方法实现了系统可扩展性而且简化了ACS内的测试管理。因此,可以 建立多组SMU-per-pin测试系统。 对于并行测试而言,测试脚本预装载 至每台2600主机并保存在它的存储器内。 触发后,控制器将启动一个函数调用每个 组的主机,主机将运行脚本来协调其它 2600仪器。然后,此控制器扫描总线并 接收来自2600主机的测试结果。

图6. 采用GPIB和TSP-Link连接的多组2600系列仪器设置示例。每组在相同时间开始运行(相同或不同的)脚本。 结论 面市时间延长和测试成本压力增大意 味着测试工程师必须用更少的投入做更多的事。利用吉时利久经验证的仪器和测量, ACS集成测试系统填补了基于交互式实验 室工具与高吞吐量生产测试工具之间的空白。 图1所示的ACS系统表示了一种SMU-per -pin配置,这对于缩微CMOS可靠性测试非 常有利。工程师使用此系统就拥有了极大的系统灵活性和吞吐量,不仅能提供数量 巨大的统计数据,还实现了性能卓越的独 立器件测量。 想与吉时利测试测量专家互动?想有更多学习资源?可登录吉时利官方网站http://www.keithley.com.cn/ |

网友评论