QPSKЕїжЦЦїЕФFPGAЪЕЯж

ЗЂВМЪБМфЃК2010-3-22 11:51

ЗЂВМепЃКЮваОвРОЩ

|

1 в§бд ЫФЯрОјЖдвЦЯрМќПи(QPSK)ММЪѕвдЦфПЙИЩШХадФмЧПЁЂЮѓТыадФмКУЁЂЦЕЦзРћгУТЪИпЕШгХЕуЃЌЙуЗКгІгУгкЪ§зжЭЈаХЯЕЭГЁЃЫцзХГЌДѓЙцФЃМЏГЩЕчТЗЕФГіЯжЃЌFPGAдкЪ§зжЭЈаХЯЕЭГжаЕФгІгУШевцЙуЗКЃЌФПЧАвбЬсГіСЫЖржжЛљгкFPGAЪЕЯжQPSKЕФЗНЗЈЁЃ БОЮФЛљгкFPGAЪЕЯжжБНгЪ§зжЦЕТЪКЯГЩ(DDS)ЃЌЭЈЙ§ЖдDDSаХКХfдиВЈаХКХ1ЪфГіЯрЮЛЕФПижЦЪЕЯжЕїЯрЃЌГ§DAзЊЛЛЭтЃЌЦфЫќЙ§ГЬОљПкЁКвдFPGAЪЕЯжЁЃ 2 QPSKЕїжЦЕФЛљБОдРэ QPSKВЩгУЫФжжВЛЭЌЕФдиВЈЯрЮЛРДБэЪОЪ§зжаХЯЂЃЌУПИідиВЈЯрЮЛДњБэ2БШЬиаХЯЂЃЌЦфЪЕЯжгаСНжжЗНЗЈЃЌЯрЮЛбЁдёЗЈгые§НЛЕїжЦЗЈЃЌЯрЮЛбЁдёЗЈгжЗжЮЊAЁЂBСНжжЗНЪНЁЃБОЮФВЩгУЯрЮЛбЁдёЗЈBЗНЪНРДЪЕЯжQPSKаХКХЃЌШчЭМ1ЫљЪОЁЃ

ЭМ1ЯрЮЛбЁдёЗЈВњЩњQPSKаХКХ 3 QPSKЕїжЦЕчТЗЕФFPGAЪЕЯж 3ЃЎ1ДЎВЂзЊЛЛЕчТЗ

ЭМ2ДЎВЂзЊЛЛЕчТЗ ЕїжЦаХКХ(DATA)аЮГЩЫЋБШЬиТыиЃQIПкЁПгЩЭМ2ЫљВЛДЎВЂзЊЛЛЕчТЗЪЕЯжЁЃ МйЩшфЬжЦаХКХЮЊ01100011ЃЌЦфЪБађЭМШчЭМ3ЫљЪОЁЃДгЪБађЭМПЩвдПДГіЃЌДгЕк3ИіЪБжгТіГхПЊЪМЃЌУП2ИіЪБжгТіГхЃЌдкQ3ЁЂQ6ЭЌЪБЪфГіDATAЕФСЌај2bitЪ§ОнЃЌЩњГЩЫЋБШЬиТыдЊQIЃЌЫЋБШЬиТыдЊЫйТЪЮЊЪБжгаХКХ(CLKl)ЦЕТЪЕФвЛАыЁЃЮЊСЫХфКЯКѓУцЕФЯрЮЛЕїжЦЕчТЗЃЌЪБжгаХКХ(CLKl)ЦЕТЪЮЊЯЕЭГЪБжгЦЕТЪkЕФIЃЏMЃЌПЩвдЭЈЙ§MЗжЦЕЕчТЗЪЕЯжЁЃ

ЭМ3ДЎВЂБфЛЛЕчТЗЪБађЭМ 3ЃЎ2ЫФЯрдиВЈВњЩњЦї ЫФЯрдиВЈВњБЯЦїЩѕИЩDDSЙЙГЩЃЎШчЭМ4ЫљЪОЁЃ

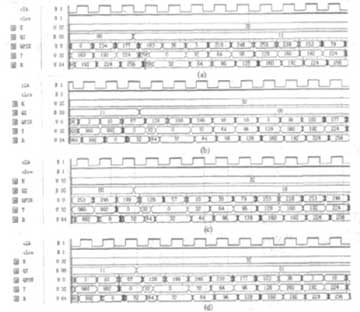

ЭМ4ЛљгкDDSЕФЫФЯрдиВЈВњЩњЕчТЗ (1)НЈСЂе§ЯвВщевБэ ROMе§ЯвВщевБэДцДЂСЫвЛИіЭъеће§ЯвВЈжмЦкЕФГщбљжЕЃЌЩшЯрЮЛРлМгЦїЕФЪ§ОнЯпПэЖШЮЊNЃЌдђга2вЛИіВЩбљЕуЁЃЯШгУЦфЫћЙЄОпМЦЫуГіет2nИіВЩбљЕуЕФЗљЖШжЕЃЌдђЯрСк2ИіВЩбљЕуЕФЯрЮЛдіШ§ИіЪБжгКѓЃЌЯргІЕФдиВЈГѕЪМЯрЮЛЁЂЗљЫвжЕгыРэТлЗжЮіЪЧвЛжТСПЮЊ2ІаЃЏ2nЃЌетбљЃЌИїВЩбљЕуЕФЮЛжУОЭШЗЖЈСЫИУВЩбљЕуЕФЯрЮЛЃЛвдROMвРДЮДцДЂ2nИіВЩбљЕуЕФЗљЖШжЕЃЌБуНЈСЂСЫИїВЩбљЯрЮЛ(ДцДЂЦїЕижЗ)гыЗљжЕЕФгАЩфЙиЯЕЁЃ ШЛКѓгУQuartus 5ЃЎ1НЈСЂmifЮФМўЃЌЕїгУLPM_ROMФЃПщЃЌНЋmifЮФЭЃЕФЪ§ОнФкШнаДШыLPM_ROMЁЃ (2)ЯрЮЛРлМгЦї ЩшЯрЮЛРлМгЦїЕФГѕЪМжЕЮЊ0ЃЌРлМгВНГЄЮЊЦЕТЪПижЦзжKЃЎдђУПвЛИіЪБжгжмЦк(1ЃЏfclkЃЉЕФЯрЮЛдіСПЮЊKЁС2Іа2nЃЌвЛИіЭъеће§ЯвВЈжмЦкашвЊНјаа2Іа(Kx2ЃЏ2n)=2NЃЏKДЮРлМгЃЌЫљвдЪфГіаХКХжмЦк10t=(IЃЏfclk)X2NЃЏKЃЌЪфГіаХКХЦЕТЪfout=KxfclkЃЏ2nЁЃ (3)ТпМбЁЯрЕчТЗ ЫЋБШЬиађСаQIзїЮЊЯрЮЛПижЦзжгУгкЫФжжЯрЮЛдиВЈЕФбЁдёПижЦЁЃБОЮФШЁNЃК10ЃЌЯШМЦЫуГіет210=1024ИіВЩбљЕуЕФЗљЖШжЕЃЌСПЛЏЮЊ8ЮЛЖўНјжЦЪ§БэЪОЁЃЯрЮЛЮЊІа/4КЭ3ІаЃЏ4ЪБЃЌЖдгІЗљЖШжЕЮЊ38ЃЌДцДЂЕижЗЗжБ№ЮЊ000111111lКЭ0101111111ЁЃ БОвхжагУVHDгяОфРДЭъГЩТпМбЁЯрЕчТЗЁЃ if clk"event and clk=ЁЏlЁЏthen b<=QI(1)ЃЛ c<=QI(0)ЃЛ if (clklh='1' or clkll='1' or clk2h=1ЁЏor clk21='1')then -- УПИіЫЋБШЬиТыдЊЕФЩЯЩ§би case QI is whenЁБ00ЁБ=>uuu<=ЁБ100111111lЁБЃЛreset<=ЁЎ1ЁЏЃЛ--5ІаЃЏ4диВЈ whenЁБOlЁБ=>uuu<-ЁБ01011111IlЁБЃЛreset<=ЁЎ1ЁЏЃЛ--3ІаЃЏ4диВЈ whenЁБ10ЁБ=>UUll<=ЁБ1101111111ЁБЃЛreset<=ЁЎ1ЁЏЃЛ--7Іа/4диВЈ whenЁЏЁЏ11ЁБ=>uuu<-ЁБ0001111111ЁБЃЛreset<=ЁЎIЁЏЃЛ --4диВЈ when others=>uuu<=ЁБ0000000000ЁБЃЛreset<=ЁЎlЁЏ end easeЃЛ else uuu<=uuu+ЁА0001000000ЁБЃЛreset<=ЁЎ0ЁЏЃЛ endifЃЛ (5)ЯрЮЛЕїжЦЦї дкУПИіЫЋБШЬиТыдЊЕФЩЯЩ§биВњЩњвЛИДЮЛаХКХ(RESET)ЪЙDDSЕФХяЮЛРлМгЦїЧхСуЃЌдђЪфГіВУВЈаХКХЕФГѕЪМЯрЮЛНігЩЯрЮЛПиАЦзжПижЦЃЌвдБЃжЄГѕЪМЯрЮЛЮЊ0lТыдЊЖдгІЕФдиВЈЯрЮЛЃЛЖјЦфЫќЧщЬсЯТНЋЦфгыЯрЮЛРлМгЦїЕФЪфГіЯрМгЃЌЙВЭЌзїЮЊдиВЈаХКХЕФЯрЮЛЃЌДгЖјЪЕЯжЕїЯрЁЃ 4 ЗТецЪЕбщМАНсТл ЗТецЪЕбщжаЃЌШЁfclk=294912HzЃЌM=48ЃЌK=32ЃЌдђfclk=fclk/M=6144HzЃЌдиВЈЦЕТЪfout=KxfclkЃЏ2N=9216HzЁЃЭЈЙ§Quartusll 5ЃЎ1ШэМўЗТецЃЎЕУЕНЗТецНсЙћШчЭМ5ЫљЪОЁЃ дкЭМ(5)жаЃЌЕБQIЮЊ11ЪБЕФЕквЛИіЪБжгЃЌRESETаХКХЖдDDSМФДцЦїИДЮЛ(T=0)ЃЌРлМгЦїжаЕФМгЗЈЦїЪфГіR=32ЃЌВЂБЃГжвЛИіЪБжгЃЛЕкШ§ИіЪБжгКѓQPSKЪфГіЮЊ218ЃЌетгыQIЮЊ11ЪБЃЌдиВЈГѕЪМЯрЮЛЮЊІаЃЏ4ЁЂЗљЖШжЕЮЊ218ЪЧвЛжТЕФЁЃМфбљЃЌЕБQIЮЊ00ЁЂlOЁЂOlЕФЗТецНсЙћЗжЙаШчЭМ5(b)ЁЂ5(c)ЁЂ5(d)ЫљЪОЃЌдкQIТыдЊЕНДяШ§ИіЪБжгКѓЃЌЯргІЕФдиВЈГѕЪМЯрЮЛЁЂЗљЖШжЕгыРэТлЗжЮіЪБвЛжТЕФЁЃЫфШЛQPSKаХКХгаШ§ИіЪБжгЕФбгГйЃЌЕЋгЩгкИїQIТыдЊЕФбгГйЖМЪЧвЛжТЕФЃЌВЂВЛгАЯьQPSKЕФЪЕЯжЃЛСэвЛЗНУцЃЌбгГйЪБМфВЛЕНЯЕЭГЪБжгжмЦкЕФШ§ЗжжЎвЛЃЌПЩвдКіТдЁЃ

ЭМ5ЗТецЪЕбщВЈаЮ 5 НсЪјгя БОЮФВЩгУFPGAЪЕЯжQPSKЕїжЦЦїПЫЗўСЫДЋЭГЕФФЃФтЕїжЦЦїЕФЬхЛ§ДѓЁЂГЩБОИпЁЂЯЕЭГЕїЪдФбКЭЩњВњжмЦкГЄЕШШБЕуЁЃБОЮФзїепДДаТЕудкгшГ§СЫDAзЊЛЛЭтЃЌЯЕЭГШЋВПгЩFPGAЪЕЯжЃЌЖдгкЦфЫќЕїжЦЗНЪН(ШчDQPSKЁЂ8PSKЁЂQAMЕШ)ЕФFPGAЪЕЯжЃЌвдМАFPGAдкШэМўЮоЯпЕчжгЕФгІгУОпгавЛЖЈЕФВЮПММлжЕЁЃ зїепЃКаЛКЃЯМ РДдДЃКЮЂМЦЫуЛњаХЯЂдгжОбЎПЏ |

ЭјгбЦРТл