运放稳定性连载17:电容负载稳定性:输出引脚补偿(1)

发布时间:2012-8-13 11:36

发布者:eechina

|

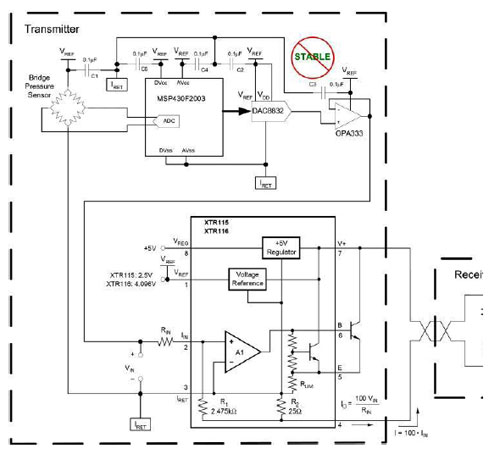

作者:德州仪器公司 Tim Green 本系列文章的第9部分是大家熟悉的电子工程的第5章保持电容负载稳定性的六种方法”。这六种方法包括:Riso、高增益及CF、噪声增益、噪声增益及CF、输出引脚补偿以及带双向反馈的Riso。我们将在本部分介绍输出引脚补偿。这种保持电容负载稳定性方法不同于输出运算放大器“缓冲”网络,输出运算放大器“缓冲”网络通常用于功率运算放大器(带有所有NPN输出级)输出,其目的是在驱动电容负载时防止意外高频振荡。本系列文章的后面章节将详细介绍“缓冲”网络的使用情况。 有时,在现实生活中,我们并非总能够接近运算放大器的 -输入和/或 +输入,因此无法在模拟工具栏中使用其他补偿方法。我们将会在本部分探讨用于发射极跟随器输出运算放大器及CMOS RRO运算放大器的输出引脚补偿方法。发射极跟随器应用需要在独特的4~20mA构建块集成电路上采用一个参考输出。CMOS RRO应用涉及一种用于电源反馈的差动放大器。这两种依范例定义的情况都属于现实应用。为此,我们可以断定唯一的保持电容负载稳定性的方法只能是输出引脚补偿。除了一阶分析与TINA Spice模拟之外,我们还可以利用“预测”结果来进行实际实施。 双极性发射极跟随器:输出引脚补偿 我们的双极性发射极跟随器输出引脚补偿实例如图9.1所示。XTR115/XT116是一种可以将输入电压变化转换成4~20mA模拟信号的双线4~20mA集成电路。由于4~20mA发送器用于驱动长距离线路,因此需要7.5~36V的大工作电压范围。此外,XTR115/XTR116配有子稳压器,可为传感器调节电路提供5V的供电电压,以及2.5V(XTR115)或4.096V(XTR116)的高精度参考电压。 4~20mA信号范围是既定的行业标准,用于工厂(普遍存在50或60Hz高电压噪声)等嘈杂环境中长距离(1英里或1.6公里以上)模拟信号的传输。由于该标准是采用电流控制的传输,因此使用两条线路可以避免电压噪声耦合。它采用两条相同的线路来传输功率与信号。由于使用的模拟信号范围规定为4~20mA,因此其中4mA的信号可驱动信号调节电路并触发两条线路发送器端的传感器。功率由接收机提供,而接收机同时还能接收4~20mA的模拟信号,该信号已根据传感器测量的实际参数(如:桥接压力传感器发送的压力)进行了分级。4~20mA信号在接收机端通常由A/D转换器转换为1V~5V的电阻器(250欧姆)电压。 通常在此类4~20mA传感器发送器中采用微控制器读取并将线性常数应用到实际传感器中。微控制器必须是低功耗控制器,以便允许某些电流触发传感器,原因是我们的总调节电路电流预算必须低于4mA。MSP430F2003提供一种低电压、低静态电流微控制器。该微控制器具有一个用于读取桥接变化的板上ADC。在微控制器应用了线性常数之后,即与DAC8832(一款用于生成XTR115/XTR116所需模拟输入电压的低功耗DAC)进行通信。DAC8832 由一种零漂移、低功耗、单电源的运算放大器(OPA333)进行缓冲。由于我们的系统是一套完美的系统,因此可驱动任何器件,其中包括XTR115/XTR116的精确VREF引脚。我们之所以选择XTR115 (2.5V VREF) 是因为MSP430F2003 只能在1.8V~3.3V范围内工作。目前MSP4302003的板上ADC以及DAC8832将采用XTR115高精度2.5V参考电压。我们的典型总调节电路静态电流为562uA,可以保留3.4mA的电流用于触发桥接传感器。目前我们唯一的难题是需要添加许多本地旁路电容器,以便在XTR115的VREF引脚驱动的众多集成电路附近实现良好的高频旁路。 XTR115 VREF 引脚是否稳定?

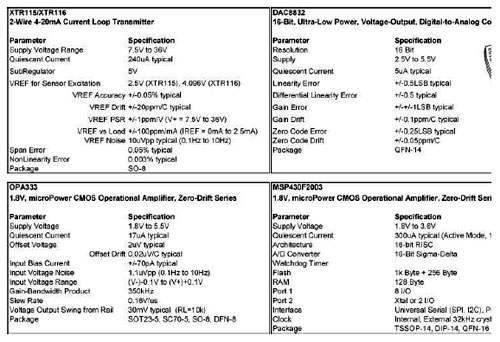

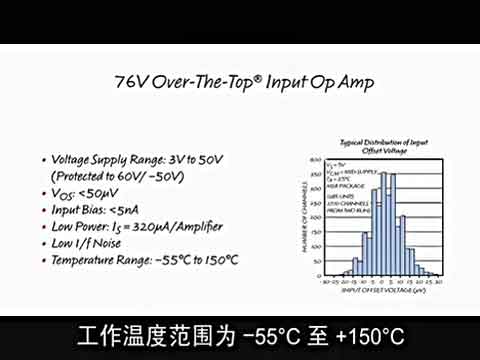

图 9.1:4-20mA桥接传感器应用 图9.2详细说明了 4~20mA 桥接传感器信号调节器应用中采用的集成电路的主要规格。

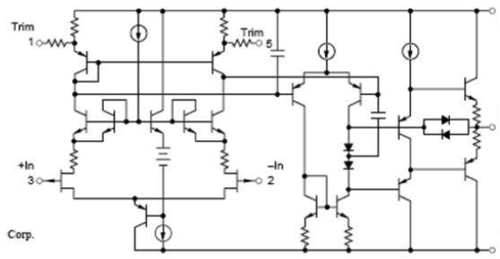

图 9.2:4~20mA调节电路IC主要规格 XTR115 VREF引脚是图9.3所示的发射极跟随器输出拓扑运算放大器的输出引脚。

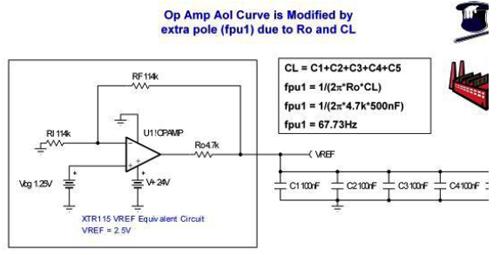

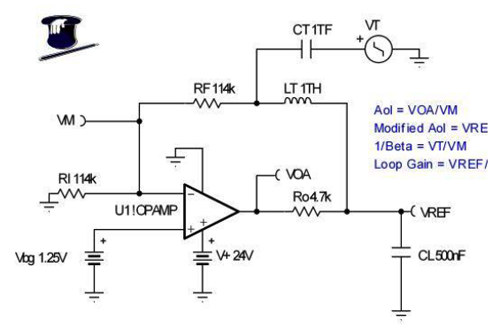

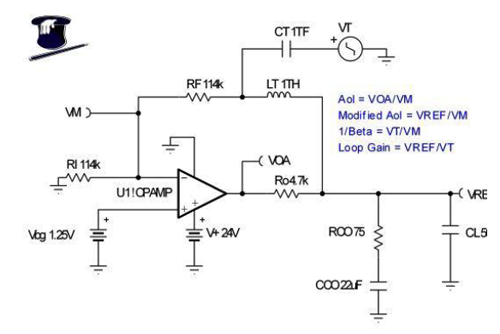

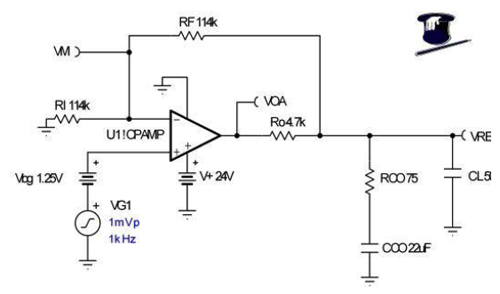

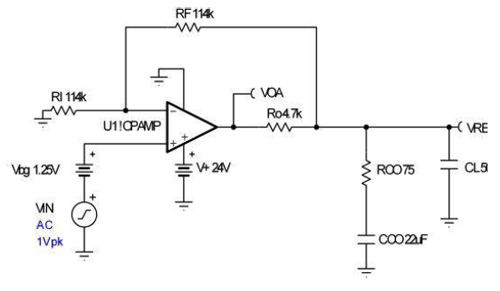

图 9.3:XTR115 VREF引脚:发射极跟随器输出运算放大器 图9.4显示了XTR11 VREF引脚的等效示意图。VREF是缓冲的1.25V带隙参考电压,经过2倍放大后产生XTR115 2.5V参考输出电压。发射极跟随器输出级的Ro为4.7k欧姆。我们是从工厂获得上述信息、RF与RI值以及U1的Aol曲线的,因为XTR115的产品说明书并未详细介绍所有资料。我们的总电容负载CL为500nF。Ro与CL互动,形成 XTR115 VREF运算放大器的 Aol 修正曲线中的第二个极,即fpu1。请注意:我们无法接入U1的 - 输入或 + 输入,因为它是XTR115的内部器件。所以我们只能使用一个引脚来补偿放大器稳定性(输出引脚:VREF)。另外,我们希望使VREF引脚保持极高的精度,因此在CL前面将该引脚与任何电阻串联均不是理想的解决方案。

图 9.4:XTR115 VREF引脚:电容负载等效示意图 我们将采用图9.5所示的TINA Spice电路检验运算放大器的Aol曲线以及由于CL导致 Aol修正曲线。我们通过LT(相关DC频率时短路、相关AC频率时开路)以及CT(相关DC频率时开路、相关AC频率时短路)使用我们的Spice AC分析方法。

图9.5:AC稳定性检查:原始电路 图9.6显示了运算放大器Aol曲线以及由于CL导致的Aol修正曲线。在fcl1可以看到,就我们的一阶稳定性标准而言不稳定的每十倍频程40db的闭合速率。根据预测,CL导致的fpu1为67.73Hz,其从检测的角度来看在本图中是正确的。

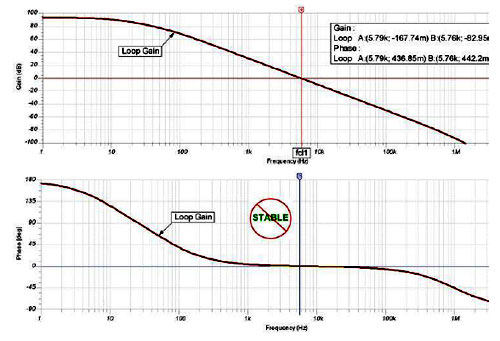

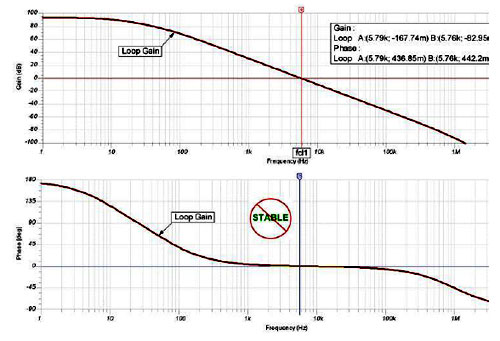

图 9.6:Aol与修正Aol:原始电路 我们检查了图9.7所示的环路增益图,并可以证实了当相位裕度在fcl1位置几乎为零时(0.442度)对稳定性的担心。

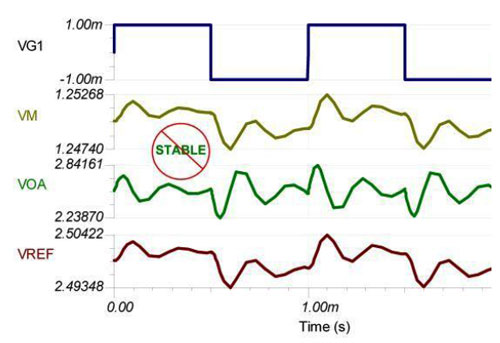

图 9.7:环路增益图:原始电路 我们在图9.8进行瞬态稳定性测试 ,即在附带500nF CL的闭环电路中注入一个较小的方形波。

图 9.8:瞬态稳定性测试:原始电路 图9.9中的瞬态稳定性图再次表明我们的电路并不稳定。我们的运算放大器输出在响应小步阶变化时从未稳定过。请注意:VOA以大约2.5V幅度变化,表明我们的DC电平对于本电路而言是正确的。

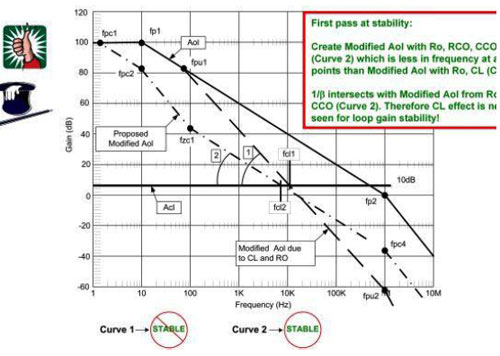

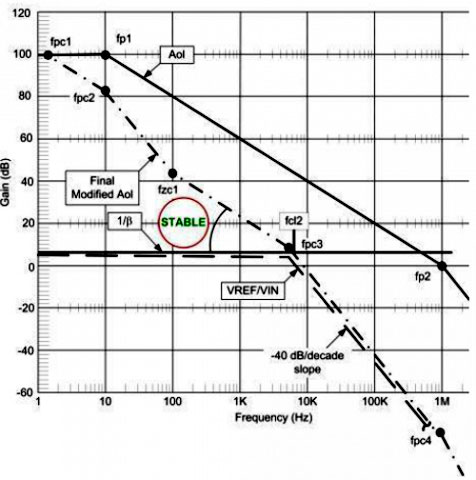

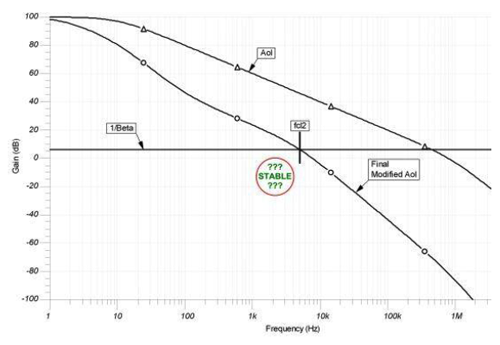

图 9.9:瞬态稳定性图:原始电路 我们在图9.10中明确了用于双极性发射极跟随器输出放大器的输出引脚补偿方法。首先我们用fpu1来修正运算放大器原始 Aol 修正曲线,fpu1是由于Ro与CL产生的极点(参见曲线 1)。一旦创建了该曲线,我们就可以绘制从曲线1与0dB交叉点开始的第二条曲线(曲线2)。从上述起点我们按照每十倍频程 -20dB 的斜率绘制出比fp1(运算放大器Aol低频极点)高一个十倍频程的点,我们在此处把斜率修改到每十倍频程-40dB。在频率为fp1时我们将斜率改回每十倍频程-20dB,直到与运算放大器的DC Aol值相交叉。上述建议的Aol修正曲线(曲线2)满足我们所有经验标准??通过使极点与零点相互保持在一个十倍频程之内,从而保持环路增益相位在环路增益带宽范围不低于45度。另外,我们建议的Aol修正曲线(曲线2)还可满足在 fcl2 闭合速率为每十倍频程20dB的一阶稳定性标准。

图 9.10:输出引脚补偿:双极性发射极跟随器 图9.11说明了我们如何利用RCO及CCO获得建议的Aol修正曲线。另外我们还需要考虑另外一个极点,因为CCO在某些高频情况下会短路,而且CL与RCO将形成一个附加高频极点。即使此极点在fcl2之外出现,我们的情况仍然正常。

图 9.11:AC稳定性检查:输出引脚补偿 由于知道Ro与CL,因此可以利用图9.12所示公式以及图9.10(曲线2)建议的Aol修正曲线计算出补偿分量RCO与CCO以及由RCO与CL形成的超高频极点。

图 9.12:输出引脚补偿公式:双极性发射极跟随器 我们在图9.13中采用输出引脚补偿方法绘出预测曲线。由于XTR115之内的闭环运算放大器以2倍增益运行(6dB),闭环VREF/VIN曲线始终保持平直,直到在fcl2位置与Aol修正相交,由于环路增益已经等于零,因此此后该曲线随Aol修正曲线一直降低。

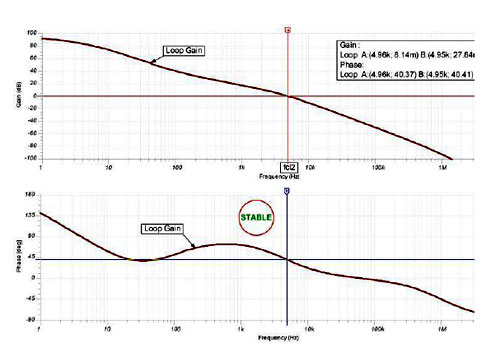

图 9.13:最终预测曲线:输出引脚补偿 图9.14是在采用图9.11所示电路的情况下,我们的AC稳定性分析TINA Spice模拟结果。在fcl2位置时可以看到每十倍频程20dB的闭合速率,但是我们应当通过相位图了解详细情况。

图 9.14:Aol与Aol修正:输出引脚补偿 图9.15所示的环路增益图证明我们的输出引脚补偿方法可以产生稳定的电路。在fcl2位置时相位裕度为40度,相位在环路增益带宽范围内不会过多低于45度。如果需要,我们可以细微调节输出引脚补偿值,以便在fcl2获得更高的相位裕度。

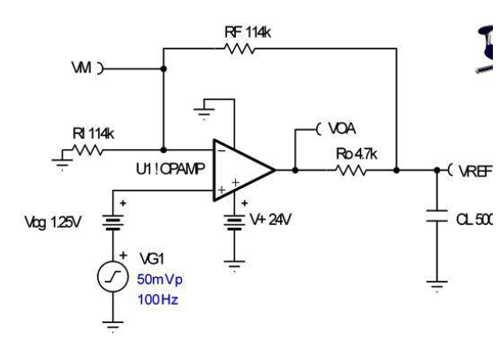

图9.15:环路增益:输出引脚补偿 图9.16中的电路采用瞬态稳定性测试来检查采用了输出引脚补偿的最终电路。

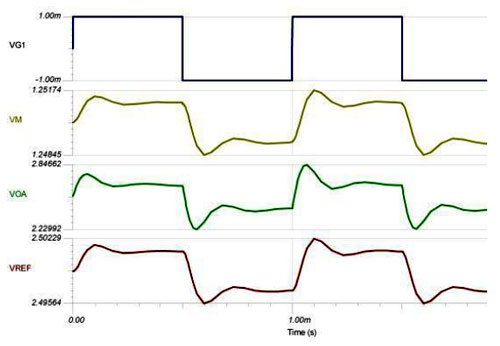

图9.16:瞬态稳定性测试:输出引脚补偿 图9.17所示的瞬态稳定性测试结果证明了我们的环路增益检查,即输出引脚补偿可以产生稳定的电路。一个较低的过冲以及无过度振铃的一个下冲看起来接近典型的、45度相位裕度补偿电路。

图9.17:瞬态稳定性图:输出引脚补偿 图9.18所示的TINA Spice电路使我们能够检查最终的VREF/VIN闭环AC响应是否符合在图9.13中的预测。

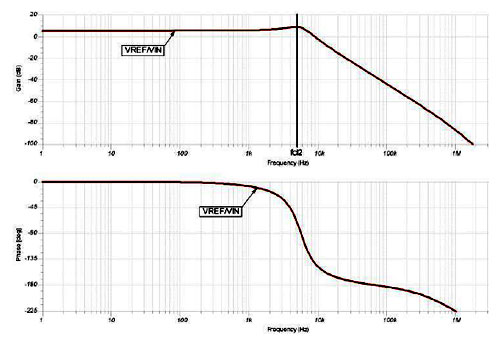

图 9.18:VREF/VIN AC电路:输出引脚补偿 根据图9.13,我们估计fcl2约为5kHz,因此预计对于VREF/VIN而言在该点会出现陡然降低。在图9.19中,我们可以看出闭环AC响应符合预测结果。在AC闭环响应中存在轻微峰化现象,不过其对于本应用不会造成影响。同样,如果我们希望减少这种峰化现象,就需要再次利用我们的输出引脚补偿把fcl2点的相位裕度提高到40度以上。

图9.19:VREF/VIN AC响应:输出引脚补偿 |

网友评论