用FPGA实现数据远距离的高精度传输

发布时间:2012-4-1 11:13

发布者:诸葛孔明

|

1 意义 简单的多机间数据通信在我们的设计中很普遍,一般情况下数据传输距离很短,不会超过百十m,因此仅采用双绞线加RS232或RS485标准就可以有效传输。但有时多机之间的距离也会很远,如我们所设计的一个气象项目,就要求子站遍布在基站1km范围内。因此在考虑成本、不增加很多设备的前提下,有效防止噪声干扰,保证子站与基站的数据高精确传输就很重要。 通常多机短距通信中,可以在收发端加入奇校验、累加和校验等出错就重发的防噪声措施;但以上措施都只能检错,不能纠错,也就是说传输过程中不能容错。在远距离、干扰大、出错概率非常高的情况下,单纯的出错就重发措施会失去工作效率和意义。因此,我们需要一种能容错的数据传输方式,就要对数据编码。因此,不同传输环境的噪声性质不相同,对应的编码方式也不一样,所以我们设计编码时强调更多位的纠错冗余,以适合较多的环境,但相应地就降低了传输速率。另外,出于通用性和简易性的考虑,我们的设计应可直接加载于原有的有线或无线通信系统上,除数据连线外,不需对原有系统做任何改变。 在此,我们采用了交错编码技术来增加数据传输过程的容错能力。编解码设备插入加载到通信系统原来的数据收发端口。因此,微处理器要发送的数据由原先的直接经发送端(无线通信为调制器和发送器)发送,变为先经编码设备编码,然后再经原有的发送端发送;同理,接收端(无线通信为接收器和解调器)收到信息,经解码设备解码出数据,再传送给微处理器。 2 设计方案 为适应多种信道,要求我们的设计能同时纠随机错和突发错,并且能有多位的纠错冗余。因此,我们基于常用的卷积码和循环码特性,自定义一种简单的线性分组码作为纠错编码,以便我们刻意去提高纠错的位数。同时我们采用交错发送技术来提高纠突发错能力,并利用FPGA去实现该方案。 (1)方案的应用范围 我们所设计的方案用于远距离的多机通信。根据实际经验,本方案默认微处理器收发的数据为8位并行数据+1位同步时钟,因此提供8位数据线和1位同步线。对于串口,则可增加串行转换的移位寄存器来转化。 (2)方案的实现 方案的实现如图1所示。

①在子站、基站的收发端口与微处理器之间分别加入相应的编解码设备,使得子站与基站间传输的数据先经过编解码再传输,以达到增强容错的能力。 ②用帧结构实现码字的交错。 ③远距离传输,收发端最好选用同步方式,但这不是本设计的内容,不予以讨论。 (3)基于精度,对数据的每一位单独编码 实际应用中,对数据精确的定义并非数据的完全重合,而是要求某一个精度。完全重合只对用做标志的数据有意义,对单纯计算用的数据并没有必要。基于精度要求,显然一个数据信息的高位对精度影响远比低位大(如:FFH,当最高位出错变为7FH时,精度变化最大,而最低位出错变为FEH时,精度变化最小)。因此,我们并没有对8位数据信息进行整体编码,而是逐位分开进行编码:高数据位,采用更长的编码,以保证更高的正确率;低数据位,则可采用较短的编码,兼顾效率和设备容量。具体编码如表1所列。 表1 8位数据最低位(3,1)码 0对应010,1对应101,汉明距3,纠1错 8位数据第二位(3,1)码 0对应010,1对应101,汉明距3,纠1错 8位数据第三位(5,1)码 0对应01010,1对应10101,汉明距5,纠2错 8位数据第四位(5,1)码 0对应01010,1对应10101,汉明距5,纠2错 8位数据第五位(7,1)码 0对应0101010,1对应1010101,汉明距7,纠3错 8位数据第六位(7,1)码 0对应0101010,1对应1010101,汉明距7,纠3错 8位数据第七位(9,1)码 0对应010101010,1对应101010101,汉明距9,纠4错 8位数据最高位(9,1)码 0对应010101010,1对应101010101,汉明距9,纠4错 表2 第1位 第2位 第3位 第4位 第5位 第6位 第7位 最高位 0 010 010 01010 01010 0101010 0101010 010101010 010101010 1 101 101 10101 10101 1010101 1010101 101010101 101010101 对8个位远逐位编码,8个生成矩阵为1维矢量。因此用FPGA实现编码时,采用查表法更方便,如表2所列。 之所以选用010等作为码字,是因为01相间在组合为帧发送时,可以减少连0或连1的出现概率。 (4)帧结构实现交错发送技术 为纠突发错,码字要按交错格式发送。因此,用帧实现码字的交错,数据发端按帧发送,数据收端按帧解码。8个码字共48位(6字节),加帧头2字节,所以,帧为8字节。为说明帧结构,暂以字母表示码字各位: 码字0:a2a1a0; 码字3:d4d3d2ed1d0; 码字1:b2b1b0; 码字4:e6e5e4e3e2e1e0; 码字2:c4c3c2c1c0; 码字5:f6f5f4f3f2f1f0; 码字6:g8g7g6g5g4g3g2g1g0; 码字7:h8h7h6h5h4h3h2h1h0; 帧结构如表3所列。 利用帧头1和帧头2的重合特点来检测帧头,因为码字交错发送时相邻两字节对应位基本01相间的。由表3可得,第3字节到第8字节,相邻字节至少有6位不相同。因此可借用汉明距的纠错思想,认为帧头1和2不重合的位在2位以内,则表示正确收到帧头。 表3 帧头1 1 1 0 1 0 1 0 0 帧头2 1 1 0 1 0 1 0 0 第3字节 a0 c0 e0 f6 f0 g0 g6 h0 第4字节 a1 c1 e2 d0 f1 g1 g7 h1 第5字节 a2 c2 e2 d1 f2 g2 g8 h2 第6字节 b0 c3 e3 d2 f3 g3 h6 h3 第7字节 b1 c4 e4 d3 f4 g4 h7 h4 第8字节 b2 e6 e5 d4 f5 g5 h8 h5 3 FPGA实现设计 (1)单工条件下的实现 用两块FPGA分别实现编码器和解码器。按前面的编解码原理,编码器接收子站8位信息和1位同步,输出8字节×8位帧结构编码作远程传输,解码器收到帧结构编码,输出8位信息和1位同步给基站。(在实际应用中,子基站两MPU还要加入通常的累加和检错或偶校验检错。因不属编解码内容,不作讨论。)

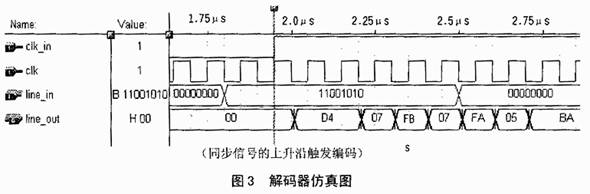

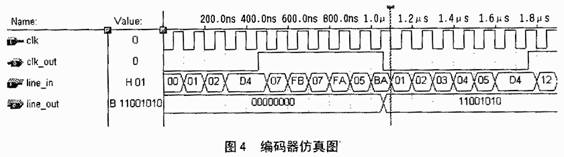

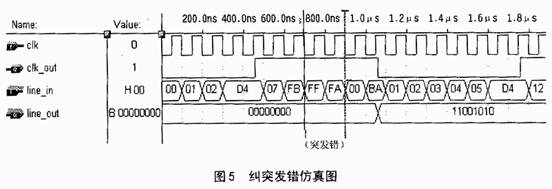

为检验电路设计,假设输入信号为11001010,编码输出的帧结构为表4。 表4 帧头1 1 1 0 1 0 1 0 0 =D4 帧头2 1 1 0 1 0 1 0 0 =D4 第3字节 0 0 0 0 0 1 1 1 =07 第4字节 1 1 1 1 1 0 0 0 =FB 第5字节 0 0 0 0 0 1 1 1 =07 第6字节 1 1 1 1 1 0 1 0 =FA 第7字节 0 0 0 0 0 1 0 1 =05 第8字节 1 0 1 1 1 0 1 0 =BA 同步信号clk_in上升沿到来时,编码器读入数据信息11001010,并按内部的波特率clk;在下降沿产生正确的帧格式编码输出(D4、D4、07、FB、07、FA、05、BA)。

当解码器判断收到帧头(两个D4),则将同步信号clk_out置高,再按内部波特率clk在上升沿收6字节的帧结构码字,在同步信号的下降沿输出译码(11001010)。

当传输过程出现突发错时,第5字节改为FF,第7字节改为00,译码器给出信息11001010。

因为信息最低位的编码能纠1位错,最高位能纠4位错,所以,当第3~5字节、第6~8字节分别出现一个8位的突发错,译码器均能完全纠正。出现多个突发错时,相应的信息低位将出错,但信息高位因具有更多位的纠错能力而仍能保持准确性。我们设计的目标也正是尽可能保证高位的正确,以保证精度。 (2)基于单工的双工通信 此时一片FPGA内集成了编码器和解码器,与MPU相连的数据通信接口仍为8位数据线,由MPU发W/R写读信号来控制编解码,因此同一时间只能单向传送数据,编解码不能同时进行。准确地说,为半双工通信。(要改为全双工,须将MPU的数据线接口翻倍,非常占资源。)

(编码器,解码器与单工的相同。) 实际上,我们对编码器和解码器的输出分别加了一个传输门(transfer_X器件)。该传输门由W/R信号控制,一旦传输门关闭,则将传输门的输出置于高阻态?quot;Z"),因此,编解码器的输入输出不会相互干扰,从而能在同一数据线上进行半双工传输。

MPU向FPGA写信息,FPGA编码输出。W/R=0,信息为11001010。 MPU读FPGA的信息,FPGA收帧结构并解码。W/R=1,解码得11001010。 4 总结 ①我们的设计目的主要在于增加数据的容错能力。FPGA设备加载于MPU的数据接口与数据通信芯片接口之间,数据仍按原系统的发送方式远距离传输,如图8所示。因此原有的通信设备不必作改动,就能很方便地加载我们的设计。同时,因为编码采用的分组码的位数可以根据实际应用场合再做简单调整,因而能够提供更大的噪声冗余。

②FPGA内部提供统一的编解码波特率,最高由FPGA时钟频率决定,仿真图中采用100ns(10MHz)。MPU收发信息的波特率最高为编码波特率的1/8,因为1字节的数据信息要转换为8字节帧结构。也就是说,我们是以降低通信的最高速率为代价来换取数据的高精度的。因此,我们的设计主要应用于不要求过高速率的通信场合。 |

网友评论