基于单片机的温度监测系统的设计

发布时间:2012-3-14 13:53

发布者:1770309616

|

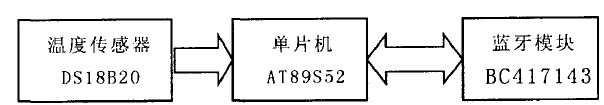

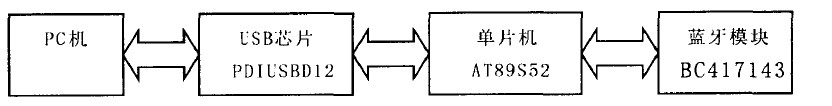

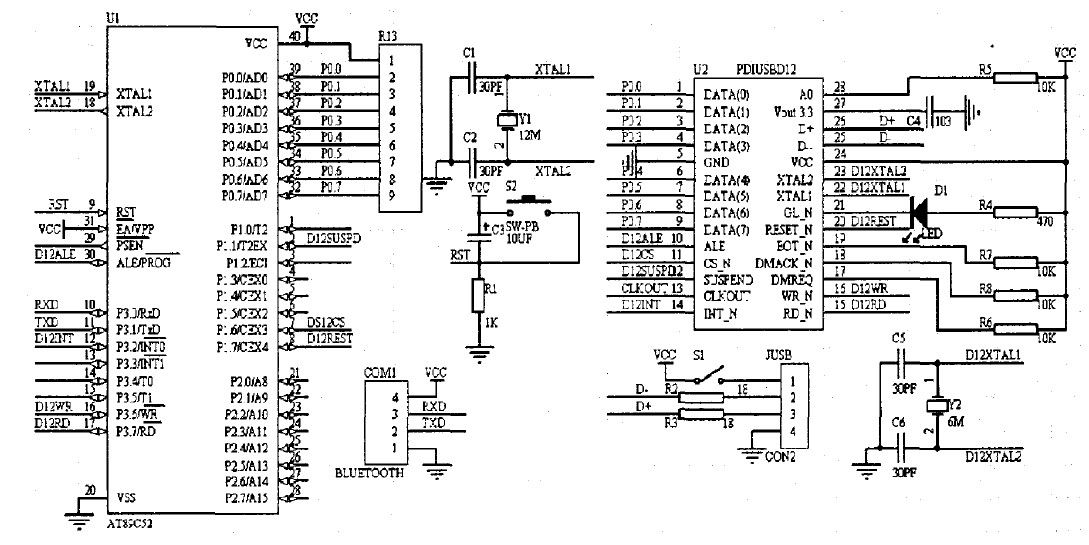

引言 温度检测是许多行业的重要工作条件之一。 无论是粮食仓库、中药仓库,还是图书保存。都需要在符合规定的温度环境条件之中。而温度却是最不易保障的指标。针对这一情况。研制一款可靠、方便、易及时调控的温度检测系统就显得极为重要。笔者运用D1S18B20采集数字信号,通过蓝牙无线通信技术和USB接口技术。实现由89S52单片机检测控制温度的监测系统。 1 系统的结构 整个系统由采集板、通信板和PC机监控程序组成。采集板以温度监测芯片DS18B20t21、单片机芯片AT89S52和蓝牙芯片BC4为核心分时完成监听主机的命令和数据采集以及数据发送的功能。可以根据接收到的主机的命令随时改变系统的工作状态。 如图1。通信板以USB 芯片PDIUSBD12、单片机芯片AT89S52为核心,实现数据接收、数据发送,以及将采集回来的外部信号通过波形图实时显示在PC机界面上。同时把数据保存到数据库中。如图2。

图1采集板系统框图

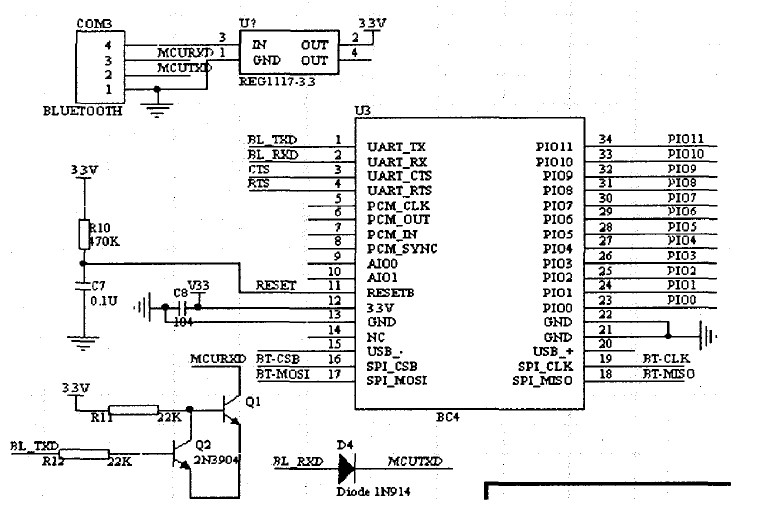

图2通信板系统框图 2 系统硬件设计2.1 采集板电路设计 2.1.1 蓝牙模块—无线接收发射电路 系统采用了CSR公司蓝牙芯片BC417143.该芯片采用Blue2.0、支持主或从模式、支持AT命令集、支持波特率为2 400到1 382 400 bps,适用于嵌入式串口传输无线的全新的模块。 值得注意的是。蓝芯片工作在3.3 V,而MCU工作在5 V.存在逻辑电平不匹配问题。且IO管脚无法容忍MCU的5 V逻辑电平。设计中采用了1117芯片进行电平转换输出3.3 V.蓝牙与MCU连接需经过电平限制以保证蓝牙模块正常工作 以下是蓝牙模块的电源选择方案及串口模块的引脚定义。如图3。

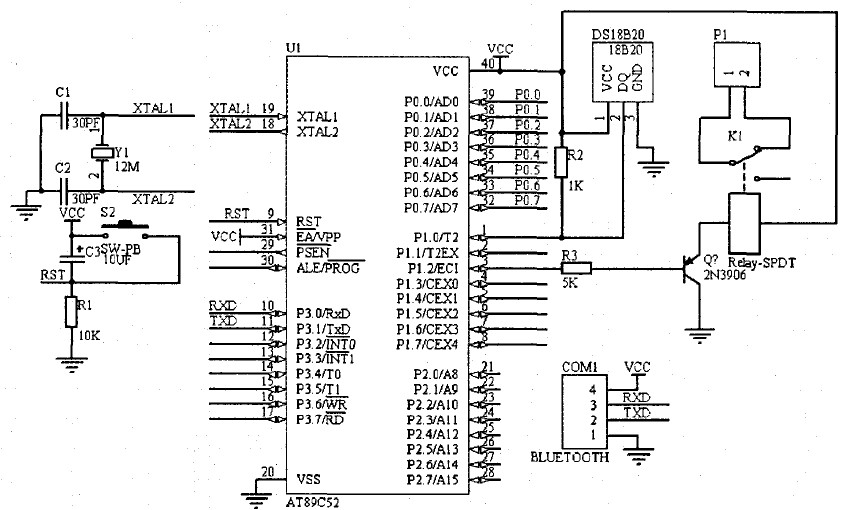

图3蓝牙模块的电路塬理图 在建立蓝牙数据通信时。需要先对其通信协议进行设置:(1)UART参数设置:先设置通信协议长度,再设置波特率、硬件控制流参数。校验参数、数据位数及停止位 (2)工作模式设置:可将蓝牙模块的工作模式设置为主模式或者从模式。 (3)设置蓝牙模块名:名称是蓝牙模块在进行通信的标识之一。通过设置蓝牙模块名协议可以更改蓝牙模块名 (4)设置安全模式:蓝牙通信中的数据安全主要是有蓝牙通信时的PIN码保障的。通过设置安全模式协议。可以根据不同的需要。设置蓝牙通信的安全模式 (5)设置PIN码:设置PIN码可以保证仅有可靠的设备通过蓝牙与模块互相通信系统采用的波特率为9 600 bps.传输距离能达10 In。由于采用蓝牙做为传输。具有很强的抗干扰能力。 2.1.2 采集板电路塬理图 采集板电路塬理图如图4。蓝牙模块主要与单片机的串行IO口连接。数字温度传感器DS18B20与单片机的P1.0口连接。继电器则与P1.2口连接。温度传感器DS18B20将温度转化为数字信号通过P1.0 El送给单片机。经单片机处理后的数据由串口传给蓝牙模块(BLUETOOTH) 也可以通过蓝牙模块接收通信板发来的指令2-2通信板电路设计通信板主要由单片机、蓝牙模块、USB模块等相关电路构成。如图5PDIUSBD12是一款性价比很高的USB器件它通常用作微控制器系统中实现与微控制器进行通信的高速通用并行接口。它还支持DMA传输此外它还集成了许多特性。包括SoftConnetTM、GoodLinkTM、可编程时钟输出低频晶振和终止寄存器集合 所有这些特性都为系统显着节约了成本。 同时使USB功能在外设上的应用变得容易。

图4采集板电路塬理图 PDIUSBD12的8根DATA引脚与单片机的PO口相连接,采用 10 k的排阻作为上拉电阻;SUSPEND是当芯片挂起状态挂起时,输出为高。与单片机的P1.1连接:INT_N是中断请求。与单片机的IN,m 连接:RD N和WR N读写选通信号分别与单片机的RD和WR连接;DMREQ、DMACK N、EOT N分别是DMA 的中断请求、DMA应答和DMA传输完成。由于没用启用DMA功能直接接高电平。RESET N是复位引脚。接单片机的P1.7;GL N是芯片的工作指示灯。接人一个LED指示灯。可以直接观察USB设备的运行状态;XTAL1和XTAL2接6MHZ.CS N为片选信号。接单片机的PI.6,A0地址线,采用I/O口模拟,接单片机P3.4:D+和D一是USB的差分数据线分别串联一个l8 Q的阻抗匹配电阻。后接USB插头上 。 蓝牙模块连接方法与采集板的连接方式相同。 通讯板的信号流程为:由采集板采集的温度数据经蓝牙模块传输到通讯板上,送到单片机上处理。通过PDIUSBD12传输到PC上进行显示保存。 单用户在PC上进行操作时,数据由PC通过PDIUSBD12传送到单片机。再经过蓝牙传输,送到采集板进行相对的响应。

图5通信板电路塬理图 3 软件设计本系统涉及内容较多。开发环境也都不一样,对于单片机软件的开发是基于KEIL uVision 3的uVision3集成开发环境IDE是一个基于Window的软件开发平台,有功能强大的编辑器、项目管理器和制作工具。 对于USB驱动的开发采用了WinDriver9.2.1.用该软件生成所需驱动只需要USB设备插入后通过简单的几步就可以完成,同时还可以根据需要生成相应的应用程序代码。方便应用程序的开发嘲。 采集板的系统流程图如图6,通讯板的系统流程图如图7PC机应用程序则采用了VISUAL STUDIO 6.0进行开发。采用C++语言编写程序代码。由于VC具有文档类程序、对话框类程序等。可以很快地实现界面的编程。

图6采集板程序流程图

图7通信板程序流程图 为了将波形图实时显示。就需要重复绘制波形图。运用传统的绘图方法。会引起屏幕的强烈闪烁。现在常用的解决方法是:利用内存绘图的技术。将需显示的图形绘制在内存位图中。然后再拷贝到屏幕上。很好地解决了屏幕闪烁的问题,并且处理速度快自定义的绘图函数声明如下。在该函数内部实现了内存绘图。void CMyusbDlg::MEM— DRAW( int ID, unsigned char m_buf, int d_ pnow,int ONDRAW, CString TXT) 在数据保存方面。本系统使用Access建立数据库。系统流程图如图8。

图8 PC机主程序流程图 当主程序开始后。初始化了USB和界面后。就创建一个新的线程,和主线程并行工作。新线程主要就是完成USB数据的读取。然后把接收到得数据存放到一个缓冲区和数据库中。缓冲区主要是供主线程显示波形时使用。数据库则供用户日后查看历史记录使用。4 结论 提出了一种基于USB与蓝牙芯片BC417143的无线温度监测系统的设计方案。并从硬件和软件两个方面介绍了系统的设计过程。实现了对温度信息进行的无线数据采集。利用蓝牙芯片作为无线收发模块。DS18B20作为温度数据采集。USB接口芯片作为与PC机的通信接口。简化了电路设计并具有易扩展和组网的特点。 |

网友评论