Globalfoundries 32nm gatefirst HKMG Llano产品工艺揭秘

发布时间:2011-10-15 00:19

发布者:1640190015

|

AMD 由Globalfoundries(以下简称GloFo)代工的Llano集显处理器产品几个月前终于在外界的一片猜测中正式面世了,这款产品采用的是 GloFo的SHP工艺进行制作的,同时也是首款推出上市的,由代工厂生产的基于gate-first HKMG工艺的芯片产品。 功能和性能方面,此前外界已经有许多文章对其进行了正面的品评,不过我们的任务则是分析其工艺和内部组成细节。不过在分析这款产品时,我们竟然无法看出其中NMOS管和PMOS管之间栅堆叠结构的明显区别,这真是一个难解的谜团。因为一般而言,NMOS管和PMOS管所需的功函数值必须有较大的区别,因此一般必须使用不同的功函数材料来制作两种管子。 举例而言,我们以前曾经分析过同属gatefirst HKMG工艺的松下Uniphier芯片产品,为了与PMOS管产生不同的功函数,其NMOS管使用了镧为NMOS管的功函数调节材料。

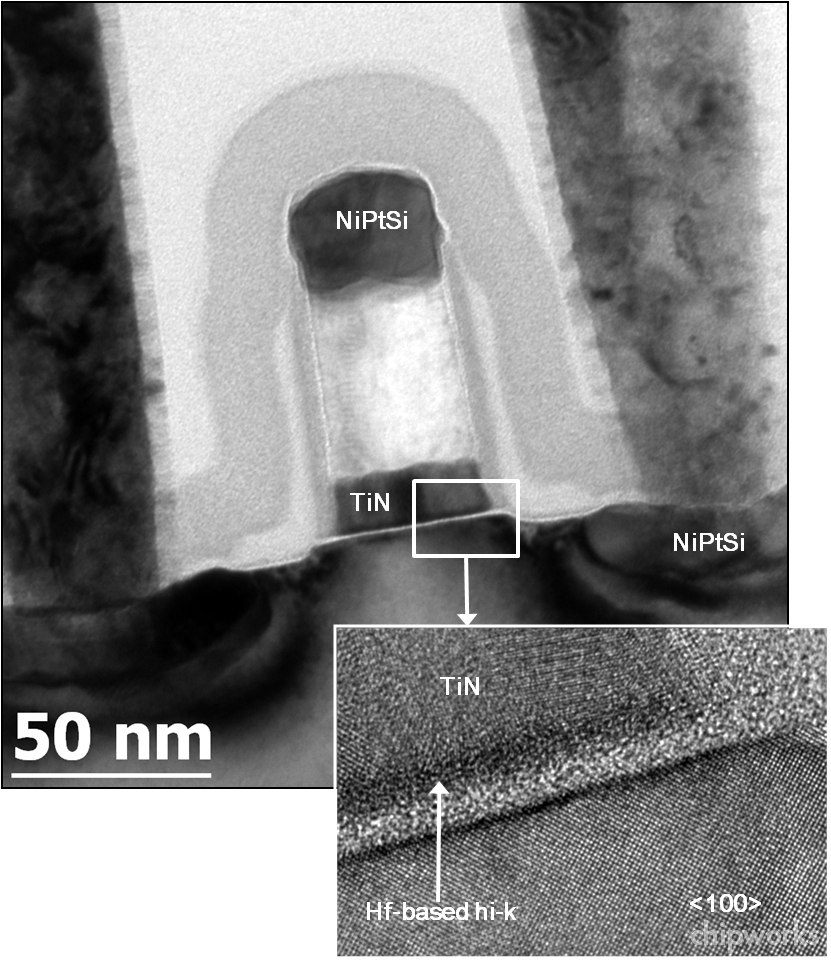

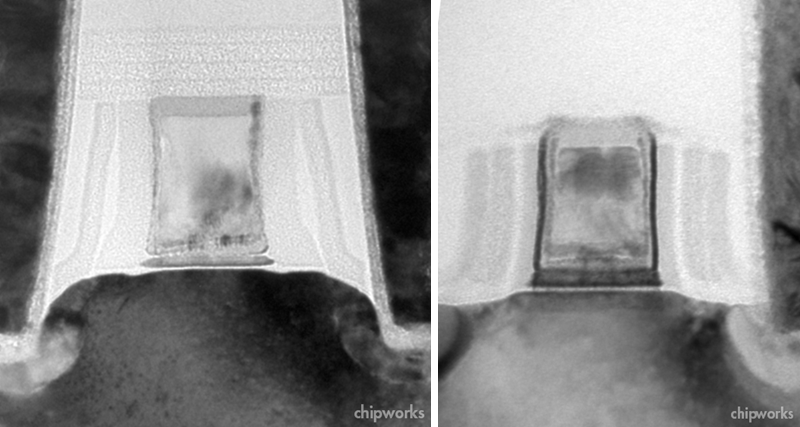

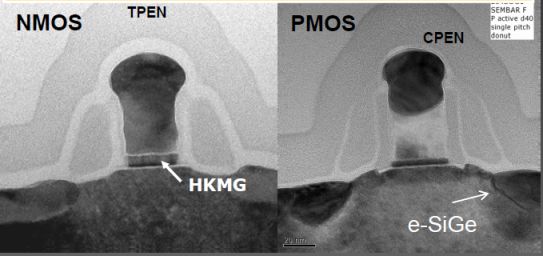

图1 松下的32nm HKMG晶体管(点击查看大图) 如图1所示,Uniphier的金属栅极结构中,多晶硅材料底部使用了TiN金属层,绝缘层部分,High-k层则位于氧化界面层上方。其NMOS管和PMOS管从外观上看,并不存在明显的结构区别,不过进一步分析栅极的细节,我们发现在NMOS管的TiN金属栅极结构中掺杂了微量的镧材料,这样便将NMOS管的功函数值调整到了需要的水平。 Llano同样使用gatefirst HKMG工艺,同样以TiN为金属栅,但其它部分则与Uniphier有比较大的区别。图2是Llano NMOS/PMOS管的纵剖对比图,图中可见其栅极结构要比Uniphier更为复杂。

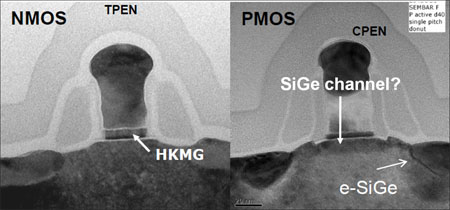

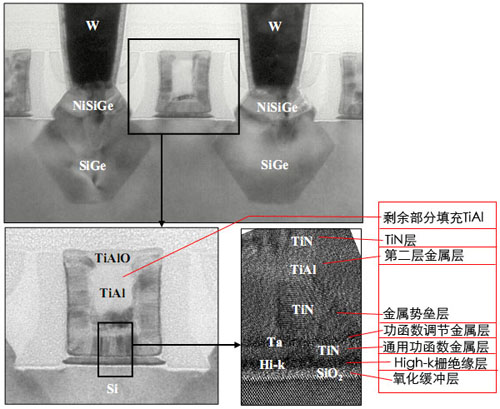

图2 AMD/GloFo的32nm HKMG NMOS/PMOS晶体管(点击查看大图) Llano的金属栅中使用了双应力衬垫(Dual-stress liners)来为沟道施加应变力。图2可见,PMOS管(需要对沟道施加压缩应力)栅极上的氮化层厚度要比NMOS管(需要对沟道施加拉伸应力)厚了一倍。另外,PMOS管中还采用了嵌入式SiGe的技术来对沟道施加压缩应力,而NMOS管中则应用了应力记忆技术(SMT: stress memorization)来对沟道施加拉伸应力。再仔细对比一下,我们还可以发现,PMOS管中的SOI层厚度也比NMOS要稍微厚一些。 图3是NMOS/PMOS管金属栅结构的细节对比图片。图中可见两者的结构基本相似,自上而下同样是采用高度金属化的多晶硅层--AlO势垒层--TiN金属栅层--铪基high-k层--SiO过渡缓冲层--衬底的结构。PMOS栅极中,AlO势垒层的扩散程度相对较高,以至于有一部分Al扩散到了TiN金属栅层中去。而NMOS的AlO势垒层中则如我们所预料的那样发现了砷材料的存在。不过PMOS/NMOS的结构细节是基本相同的。

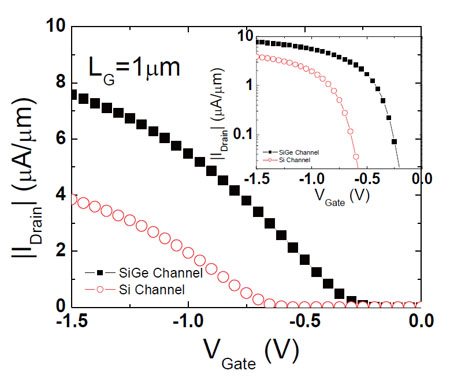

图3 AMD/GloFo的晶体管栅极堆叠(点击查看大图) 那么就产生了一个问题:NMOS/PMOS如何产生不同的功函数值呢?为此,我们在分析过程中曾经花了很多时间对Llano的金属栅进行了除铪,硅,钛等元素之外的掺杂杂质材料的分析,希望能够找到与松下Uniphier在NMOS的TiN金属栅中掺杂镧杂质类似的情况,不过即使真的存在某种掺杂的杂质,也由于掺杂的数量过小而最终没有被我们检测出来。另外一方面,虽然可以在PMOS中掺杂Al来调节功函数,但是要想形成有效的功函数调节功能,则一般也必须将Al添加到铪/SiO层的界面处,以产生电偶极效应,由此来调节功函数,但是目前为止我们并没有在Llano的PMOS管中观察到类似的结构。 那么,PMOS管中厚度更大的SOI层就应该是令NOS/PMOS功函数不同的唯一方法了。PMOS管中厚度更大的SOI层顶部实际上外延生长了一层SiGe层,这样就可以将PMOS管的功函数以及Vt门限电压调节到理想的水平,而没有使用在high-k层掺杂金属杂质的方法。多年前举办的SEMATECH会议上,曾经有人分析过这种技术。而作为该组织成员的AMD和IBM,当然也得到了这种技术的细节数据。 这种技术的原理如图4所示:衬底的价带顶电位由于掺杂了Ge元素,加上沟道两侧采用了嵌入式SiGe技术的漏源极对沟道产生的压缩应力,以及PMOS栅顶氮化应力层对沟道产生的压缩应力,因此衬底的价带顶电位相比硅衬底发生了变化。

图4 叠加SiGe层沟道后的晶体管能带图 图5中可见,SEMATECH会议的技术文件显示了SiGe型沟道相比硅沟道的驱动电流提升幅度,当然SiGe层本身的应力机制对驱动电流就有很大的改善作用。

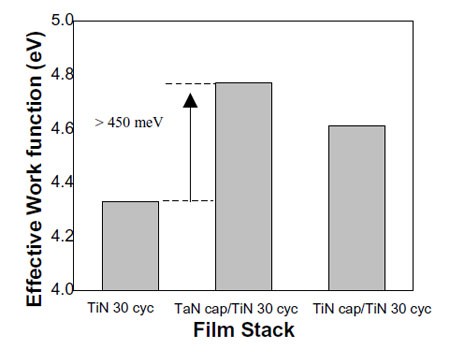

图5 SiGe沟道器件驱动电流性能改善图 PMOS管的功函数调节之谜我们基本已经解开,但是NMOS管的功函数调节问题则仍是一个谜,因为一般认为NMOS管的highk/SiO层界面处仍然需要掺杂金属杂质,而我们在实际分析中则没有发现这种结构。我们只看到在hingk层上设置的TiN层。而在Intel的产品中,他们位于high-k层上的TiN层是作为其PMOS管的功函数金属层而存在的,这样从表面上看,两者都使用了TiN层来控制功函数,那么为什么GloFo是在NMOS里用,而Intel却是在PMOS里用呢?两者的功函数调节作用难道不是一样的吗?追查SEMATECH会议的资料,我们才发现,同样是TiN层,其功函数其实还可以通过改变该层的生长条件和厚度来改变,而这方面的改变足以实现管子的功函数在NMOS/PMOS之间调节。 实际上,SEMATECH会议上2005年以后发表的技术文件所述的TiN层功函数调节技术,与我们对Llano NMOS管的观测结果是非常符合的。其NMOS管中的TiN层厚度约为2nm,而相比之下,Intel的PMOS管中则采用4nm TiN层--1nm Ta基层--2nm TiN层这种至上而下的结构。图6显示,Intel PMOS管中在2nm TiN层上增加的这两层材料完全具备将NMOS的功函数调节为适合于PMOS使用的功函数等级的能力。

图6 左至右--单独的TiN层;3.6nmTiN层上采用原子层淀积技术再淀积10nm厚TaN层;3.6nmTiN层上采用原子层淀积技术再淀积10nm厚TiN层的有效功函数对比(cyc缩写表示的应为原子层淀积的周期数) 实际上,几年前我们可能就已经接触到了GloFo可能会在PMOS管的SOI层上增加一层SiGe层的线索,当时在CICC会议的技术文件中,GloFo曾经展示了一幅类似的图片,当然他们当时并没有明说出来。

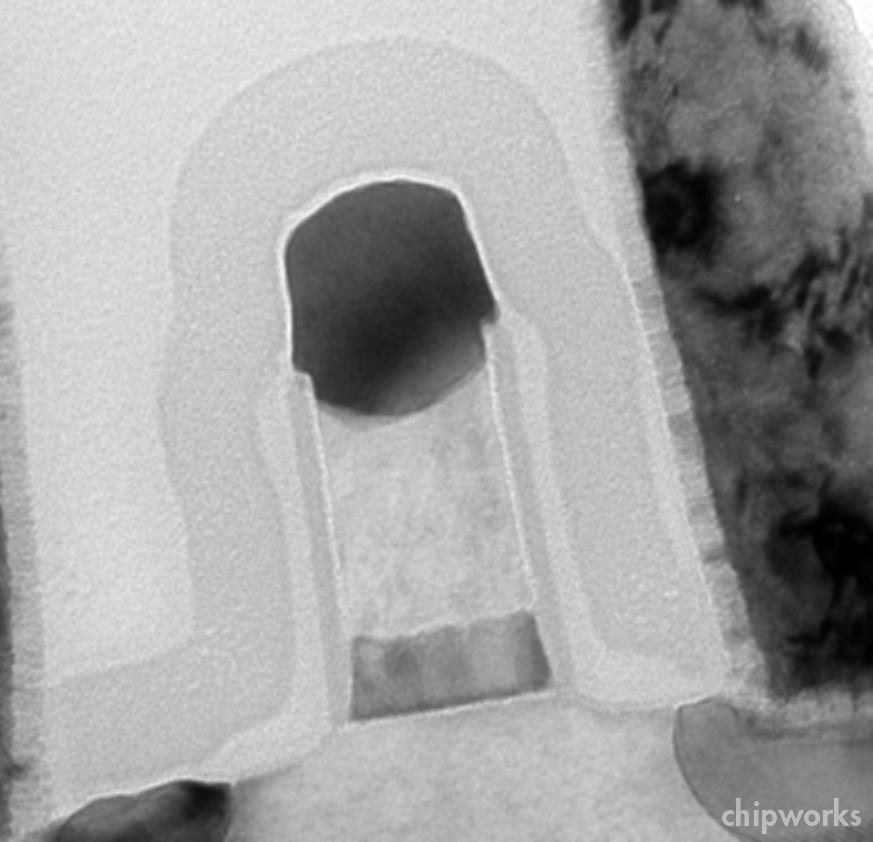

图7 GloFo当年展示的试验型晶体管图片 最后要强调的是,以上所有结论均基于我们的推断,不过我们这些推断的理论假设确实可以解释最近推出的HKMG技术产品上所存在的区别。那么,IBM,三星及其它共有技术联盟的成员会不会也使用类似的技术来制作产品呢?我们将拭目以待。 另补充:有关Intel 45nm gatelast工艺及台积电gatelast HKMG工艺的细节,请参考 : Chipworks台积电28nm HPL制程样品初步分析结果出炉 最近一周以来,Chipworks制程分析室的研究人员非常地忙碌,因为已经有很长一段时间没有采用较高级别制程的CMOS产品送到我们的分析室进行分析了,而最近,我们几乎在同一时间就一下子收到了两款这样的样品芯片。这两款芯片其一是使用台积电28nm HPL制程工艺(基于gatelast HKMG技术)制作的赛林思Kintex-7 FPGA芯片,另外一款则是使用Globalfoundries的32nm制程工艺(基于Gatefirst HKMG技术)制作的AMD A6 Llano集显处理器芯片。 由于我们过去曾经先后分析过Intel前后两代采用gatelast HKMG工艺制作的45nm至强处理器和32nmWestmere处理器两款产品,因此这次我们当然会将台积电的类似产品与其进行对比分析;同样,我们还会回顾我们去年秋季对松下采用gatefirst HKMG工艺制作的Uniphier芯片的分析结果。 台积电Gate last HKMG 28nm HPL制程产品:赛灵思Kintex-7 我们首先从赛林思的Kintex-7 FPGA产品入手吧!Kintex家族产品是赛林思最近推出的28nm制程7系列FPGA芯片中的中端产品,该系列产品的设计诉求是达到最高的性能价格比,保持芯片的性能与其前代Virtex-6产品类似,但价格则减至前者的一半左右。 1-互联层,关键尺寸分析数据: 如图1所示,Kintex-7系列产品采用了11层金属互联层的设计,其中属于1x层的有第1-4层金属层,节距为96nm左右,这也是我们目前为止所见节距最小的产品。

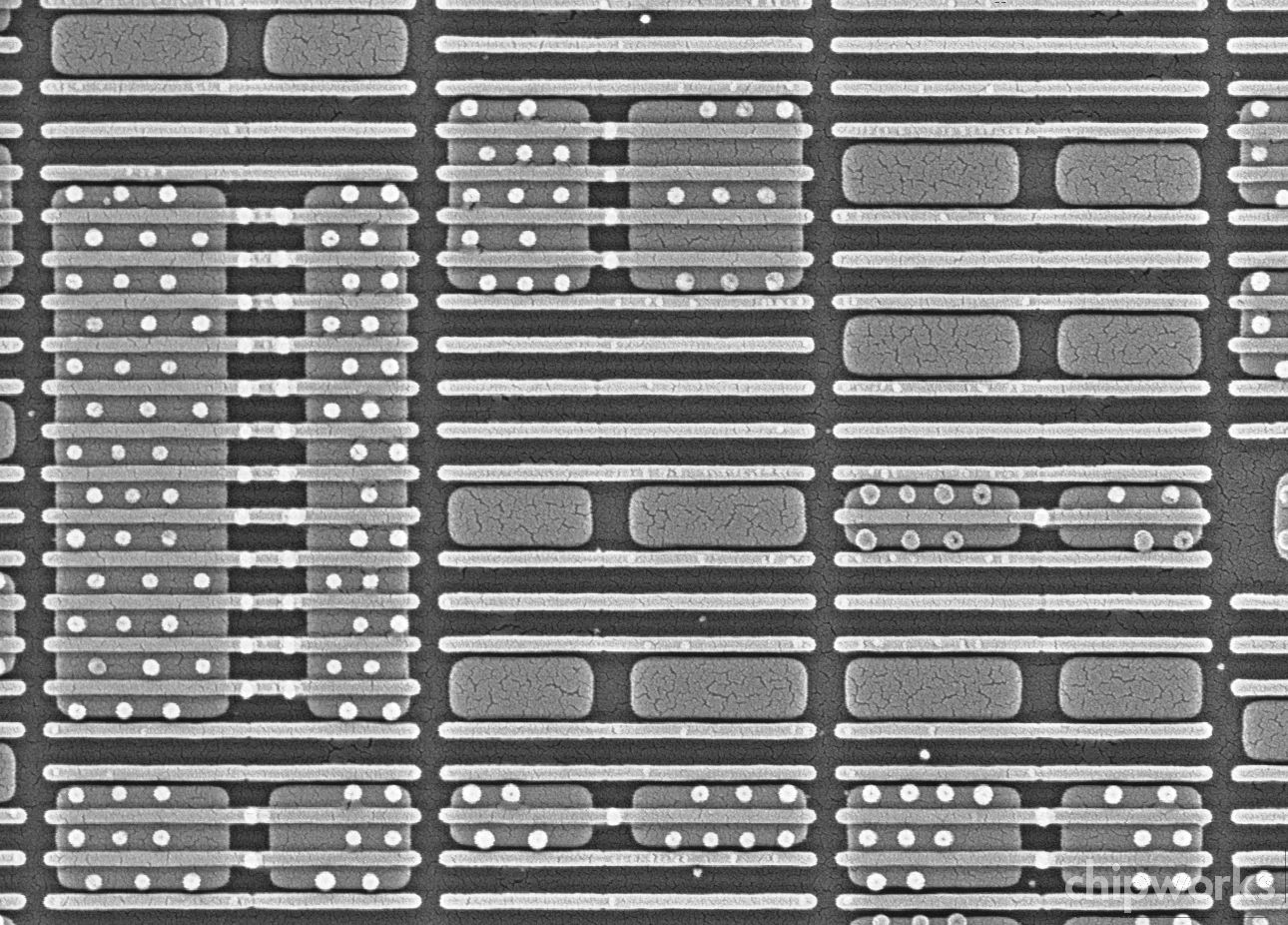

图1 赛林思 Kintex-7 FPGA产品互连层纵剖图(点击放大) 根据我们初步的分析结果,栅极触点节距(Contacted gate pitch)为118nm,最小栅长则为33nm左右,当然由于置换栅技术的采用,我们无从准确地知道原始的多晶硅伪栅极的宽度,而这个宽度才是真正用于在自对准工艺中定义漏源极的重要尺寸。 2-Layout分析: 图2的顶视图则显示台积电在这款芯片中采用了限制条件较为严格的电路布局设计准则,过去在有关gatefirst和gatelast优劣的辩论中,类似的话题也曾被经常提及。图中可见这款产品采用了单向式布局(即通常所说的1D Layout,电路图像仅朝同一个方向延伸,与之相对的是曼哈顿式布局即通常所说的2D Layout,图像可朝水平和垂直方向延伸),并采用了许多虚拟栅来保证光刻尺寸变异性。不过这种单向式布局方式相比曼哈顿式布局,在电路密度方面的确有所下降。

图2 栅极以及有源层显微顶视图(点击放大) 从外表上看,芯片在制造过程中似乎使用了双重成像技术,并应用了Cut掩模板(Cut mask,即利用向垂直方向的图像来切断水平方向的图像)。由于FPGA芯片的布局灵活程度通常要比逻辑芯片要更好,因此这款芯片中采用了大量虚拟栅和虚拟有源区的布局设计。 3-HKMG栅极结构分析: 栅极结构方面,台积电这款28nm制程产品与Intel 45nm制程产品存在一些相似之处,这些我们可以在图3-4中看到。

图3 Intel 45-nm (左) 与台积电/赛灵思28nm HPL 制程(右)NMOS栅纵切图(点击放大)

图4Intel 45-nm (左) 与台积电/赛灵思28nm HPL 制程(右)PMOS栅纵切图 图中可见,两款产品的栅极都采用了以下的同样制作步骤: 1- 首先生成栅极底部的缓冲氧化层,该层的存在可保护High-k栅绝缘层; 2- 接着淀积High-k栅绝缘层; 3- 淀积PMOS/NMOS通用功函数金属层(一般是TiN材料为主); 4- 接着淀积多晶硅牺牲栅极; 5- 用自对准工艺进行漏源极离子注入,漏源极高温退火处理; 6- 淀积互联介电层,并进行平坦化处理,直至多晶硅栅极顶部暴露在外; 7- 多晶硅牺牲栅蚀刻; 8- PMOS/NMOS金属栅形成并进行平坦化处理。 可见与Intel 45nm制程产品采用的High-k first+gate last HKMG工艺类似(Intel 32nm制程产品已升级为采用High-k last+gate last工艺),台积电28nm HPL产品同样采用了High-k first-gate last工艺。 当然两者也存在一些区别,主要在以下几点: 1- 台积电这款芯片中并没有采用嵌入式SiGe硅应变技术; 2- 台积电这款芯片的PMOS栅极中可见存在一个厚度较大的高密度金属层,而Intel的产品中没有类似的结构; 3- 台积电芯片的栅极顶部并未见有采用可施加应力的介电层结构; 4- 台积电芯片栅极的侧墙结构与Intel不同,应该是具备对漏源极进行微调的功能。 过去,Intel曾宣称在NMOS晶体管中可以利用金属栅极和触点结构来向NMOS管的沟道施加应力;我们推测台积电可能也有采用类似的技术,但是其触点的位置距离栅极边缘的距离显然更大,不太可能起到产生应力的作用。另外一方面,我们并没有看出PMOS管上有使用特殊的应变技术,因此其PMOS管中采用的应变技术(如果真有采用的话)机理未知,当然PMOS栅极中较厚的高密度金属层也许有形成应力的功用。 不过,大家不要忘记这款芯片采用的是28nm HPL制程,而这个级别制程的产品一般对管子的电流驱动能力要求并不如HP等高性能制程,因此一般这个级别制程产品中不会应用嵌入式硅锗技术。 目前有关这款产品的详细分析工作还在进行中,需要了解更多细节的读者可以参阅这个链接。 Globalfoundries Gatefirst HKMG工艺32nm AMD Llano A6集显处理器: 相比之下,另外一款样品芯片,AMD的Llano A6集显处理器我们的分析工作则才进行到初级阶段,因此目前我们只能提供一些产品/核心图片给大家先饱饱眼福了。

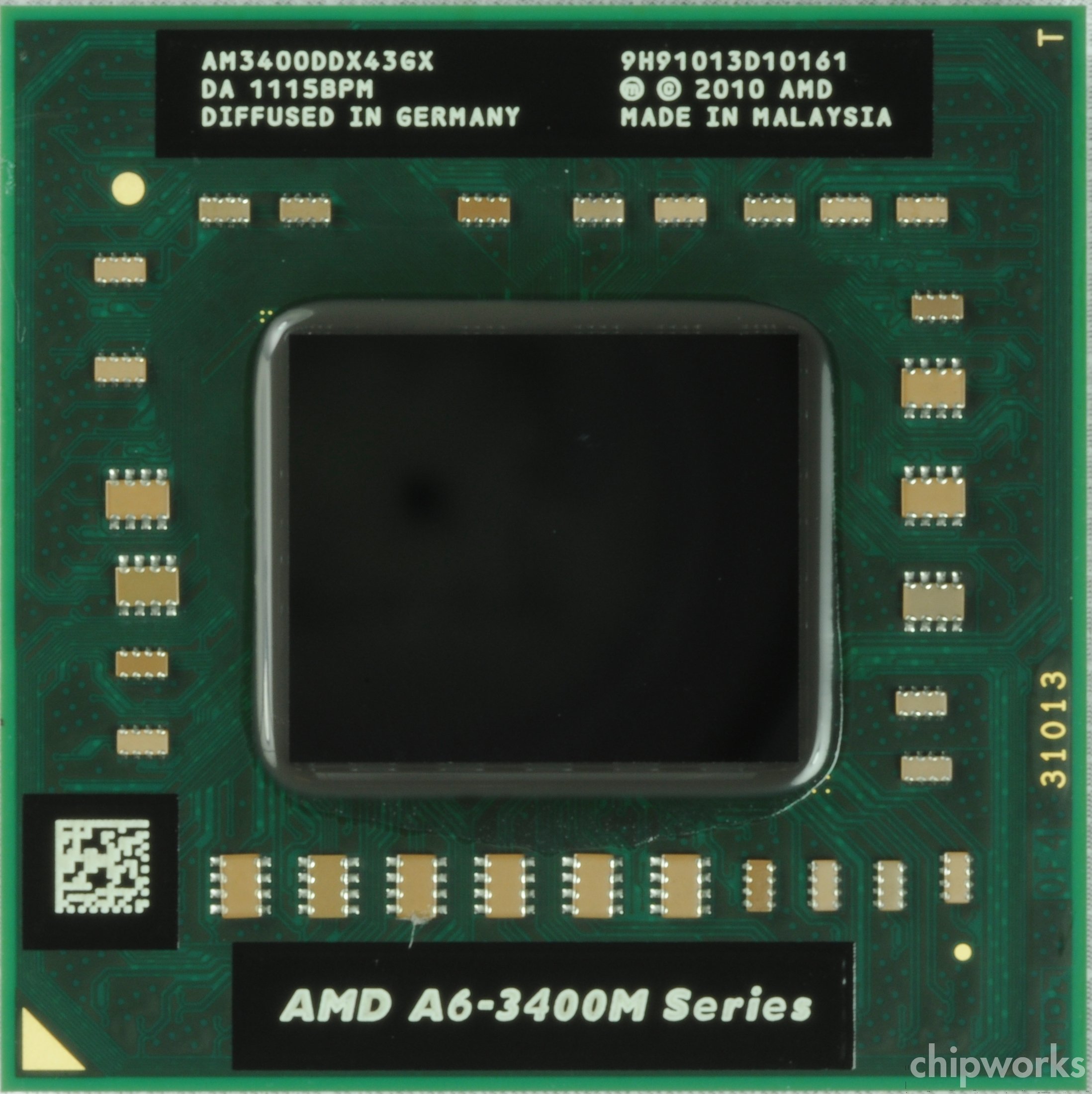

AMD A6-3400M Llano APU (点击放大)

AMD A6-3400M Llano APU Die(点击放大) 另外,CICC09会议上,Globalfoundries曾经展示过其试验型HKMG芯片的晶体管图片,在此一并贴出,也许会给我们带来一些有益的启发。

图7 Globalfoudries Gatefirst HKMG 晶体管纵剖图(点击放大) 最后,当然也不能忘了文章开头提到的松下32nm HKMG芯片的晶体管纵剖图:

松下Gatefirst HKMG工艺32nm制程晶体管纵剖图(点击放大) 补充材料1: Chipworks网站成立的初期,为了打知名度,过去曾经免费公开过一些对Intel 45nm制程处理器制程分析的较详细内容,以下是他们给出的栅极堆叠结构纵剖分析图和栅极制作工序分析。 栅极结构示意图:

PMOS

NMOS 制作工序: 1- 依次形成SiO2缓冲氧化层→High-k栅绝缘层→PMOS/NMOS通用TiN功函数金属层(因其位于High-k层上方,因此有时又被称为capping layer) →多晶硅牺牲栅淀积; 2- 多晶硅牺牲栅淀积→漏源极离子注入+退火→漏源极触点金属化→CESL蚀刻停止层淀积; 3- 多晶硅牺牲栅蚀刻; 4- PMOS/NMOS栅极同时淀积Ta+较厚TiN金属势垒层(由Ta和底部的TiN通用功函数金属层完成对PMOS栅极的功函数值调节); 5- NMOS中的Ta+较厚TiN金属势垒层蚀刻(有较少量Ta残余)→PMOS/NMOS栅极同时淀积NMOS用TiAl功函数金属以及金属栅填充材料TiAl; 6- 对金属栅进行低温热处理,令NMOS中第二层功函数金属TiAl中的Al扩散至底层的TiN通用功函数金属层,形成TiAlN,至此完成NMOS栅极的功函数调节(NMOS栅极功函数由TiAl和底层的TiAlN决定)。 由于High-k和通用功函数金属层TiN是先于漏源极退火工步淀积,可见Intel 45nm HKMG并非如Intel在各种材料(也包括其专利文件)中所说的那样采用的是100%的gatelast工艺(Intel只承认是High-k first+metal gate last)。当时人们还为此展开了一场大辩论,不过intel 45nm产品最后用实际的性能表现封住了大家的嘴,并且在32nm节点将High-k绝缘层的成型也调整到了漏源极退火工步之后,从45nm时的High-kfirst+metal gate last升级到了High-k last+metal gate last。 补充材料2: 台积电2011年1月份审批通过的一份专利中,描述了一种采用High-k first+gate last HKMG工艺制作的NMOS管金属栅极结构,如下图所示,也许可以供大家参考。

CNBeta编译 原文:chipworks |

网友评论