DAC1008D750ЃКЫЋТЗ750MspsЪ§ФЃзЊЛЛЗНАИ

ЗЂВМЪБМфЃК2011-4-28 17:48

ЗЂВМепЃК1046235000

ЙиМќДЪЃК

DAC1008D750 , ЫЋТЗ750MspsЪ§ФЃзЊЛЛ

|

NXPЙЋЫОЕФDAC1008D750ЪЧИпЫй10ЮЛЫЋЭЈЕРЪ§ФЃзЊЛЛЦїЃЈDACЃЉЃЌПЩбЁдё2ЁЂ4Лђ8ФкВхТЫВЈЦївдгХЛЏЖрдиВЈWCDMAЗЂЫЭЦїЁЃ гЩгкЦфЪ§зжЦЌЩЯЕїжЦЃЌDAC1008D750ШУЭЈЙ§ЭЈЕР0ЁЂ1ЁЂ2КЭ3ЬсЙЉЕФИДЭМЯёДгЛљДјЩЯБфЦЕЮЊIFЁЃПЩвдЭЈЙ§Дјга32ЮЛЪ§зжПижЦеёЕДЦїЃЈNCOЃЉЕФДЎааЭтЩшНгПкЃЈSPIЃЉЕїећЛьЦЕЃЌЯрЮЛЪмПигк16ЮЛМФДцЦїЁЃ DAC1008D750ЛЙАќКЌ2ЁЂ4Лђ8ЪБжгГЫЗЈЦїЃЌЬсЙЉСЫЪЪЕБЕФФкВПЪБжгКЭФкВПЕїНкЃЌвдБуЕїећЪфГіТњЖШЕчСїЁЃ ИљОнJESD204AЙцЗЖЕФвЊЧѓЃЌЪфШыЪ§ОнИёЪНЪЧДЎааЕФЁЃгыДЋЭГЕФВЂааНгПкЯрБШЃЌетжжаТНгПкОпгаКмЖрЬиЕуЃКЧсЫЩPCBВМОжЁЂИќЕЭЕФЗјЩфдыЩљЁЂИќЩйЕФв§НХЁЂздЭЌВНСДТЗКЭЭсаБВЙГЅЁЃDAC1008D750ЕФЭЈЕРзюЖрЮЊ4ЬѕЃЌзюИпДЎааЪ§ОнЫйТЪЮЊ3.125GbpsЁЃ ЖрЦїМўЭЌВНЃЈMDSЃЉПЩвдБЃжЄШєИЩDACЦїМўжЎМфЕФ1ИіЪфГіЪБжгжмЦкЕФзюДѓЭсаБЁЃMDSећКЯСЫжї/ДгФЃЪНКЭШЋДгФЃЪНЁЃ

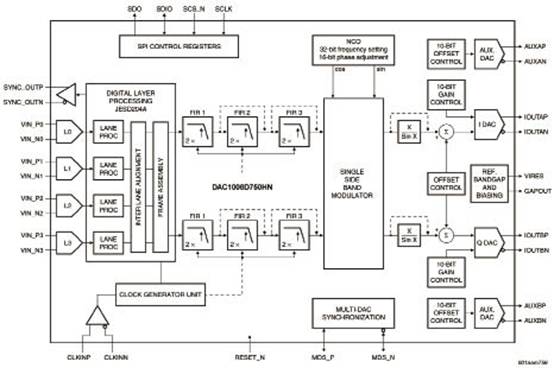

ЭМ1 DAC1008D750ЗНПђЭМ

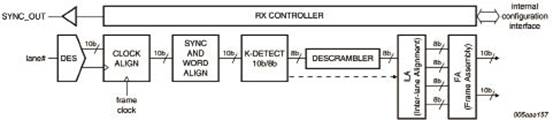

ЭМ2 DAC1008D750 JESD204AНгЪеЦї DAC1008D750ЕФжївЊЬиад • ЫЋТЗ10ЮЛЗжБцТЪ • IMD3ЃК80dBcЃЌfs = 737.28MspsЃЌfo = 140MHz • зюИпИќаТЫйТЪЃК750Msps • ACPRЃК64dBcЃЌЫЋдиВЈWCDMAЃЌfs = 737.28MspsЃЌfo = 153.6MHz • ПЩбЁдё2ЁЂ4Лђ8ФкВхТЫВЈЦї • ЕфаЭЙІКФЃК1.26WЃЈдк4ФкВхТЫВЈЦїЁЂPLLЖЯПЊКЭ740MspsЯТЃЉ • ЪфШыЪ§ОнЫйТЪИпДя312.5Msps • ЕєЕчФЃЪНКЭанУпФЃЪН • ГЌЕЭдыЩљЁЂЮоЕчШнЁЂМЏГЩЪНPLL • ВюЗжПЩЩ§МЖЪфГіЕчСїЗЖЮЇЃК1.6 mA~22mA • 32ЮЛПЩБрГЬNCOЦЕТЪ • ЦЌЩЯ1.25VВЮПМ • 4ЬѕJESD204AДЎааЪфШыЭЈЕР • ЭтВПФЃФтЦЋвЦПижЦЃЈ10ЮЛИЈжњDACЃЉ • ЕчдДЕчбЙЗЖЮЇЃК1.8 V~3.3V • ФкВПЪ§зжЦЋвЦПижЦ • LVDSМцШнЪБжгЪфШы • ЗД(sin x) / xКЏЪ§ • 2ЕФВЙТыЛђЖўНјжЦЦЋвЦЪ§ОнИёЪН • ШЋМцШнSPIЖЫПк • LMF = 421ЛђLMF = 211жЇГж • ЙЄвЕЮТЖШЗЖЮЇЃК-40Ёц~ +85Ёц • ДјгаЧЖШыЪНжеЖЫЕФВюЗжCMLНгЪеЦї • ПЩвдХдТЗМЏГЩЪНPLL • ЖрИіDACЪфГіЭЌВН • ЧЖШыЪНИДЪ§ЕїжЦЦї

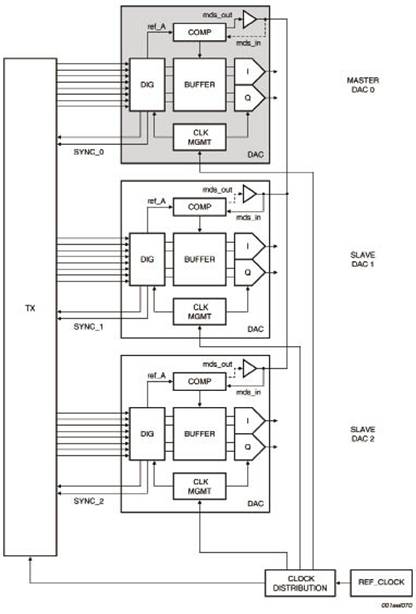

ЭМ3 DAC1008D750жїДгФЃЪНПђ

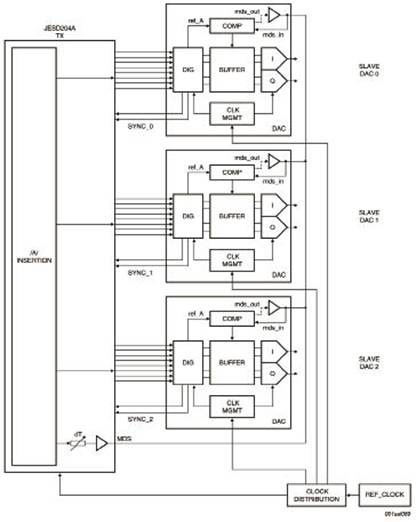

ЭМ4 DAC1008D750ШЋДгФЃЪНПђЭМ DAC1008D750ЕФгІгУ • ЮоЯпЛљДЁЩшЪЉЃКLTEЁЂWiMAXЁЂGSMЁЂCDMAЁЂWCDMAКЭTD-SCDMA • ЭЈаХЃКLMDS/MMDSЁЂЕуЖдЕу • жБНгЪ§зжЦЕТЪКЯГЩЃЈDDSЃЉ • ПэДјЮоЯпЯЕЭГ • Ъ§зжЮоЯпЕчСДТЗ • вЧЦївЧБэ • здЖЏВтЪдЩшБИЃЈATEЃЉ ИќЖрЯъЧщЃЌОДЧыфЏРРЃК http://solution.eccn.com/solution_2011030310591168.htm |

ЭјгбЦРТл